![]() U.2-PCIe変換アダプタ基板 [AB20-U2PCI] 取扱い説明書 [ Ver1.0J]

U.2-PCIe変換アダプタ基板 [AB20-U2PCI] 取扱い説明書 [ Ver1.0J]

はじめに

この度はU.2-PCIe変換アダプタ[型番:AB20-U2PCI] (以下、アダプタと略します)をご採用頂き誠にありがとうございます。 本アダプタは16Lane PCI Expressインターフェイスの16チャネル高速差動信号(Lane15-0)を4つの4-lane PCI規格U.2インターフェイスに変換するアダプタ基板です。 Altera(Intel)l/AMD(Xilinx)製各FPGA評価ボードに適用可能でDesignGateway社製NVMe-IPコア各ファミリ製品の実機評価や同IPコアを使ったユーザ製品開発に使用します。

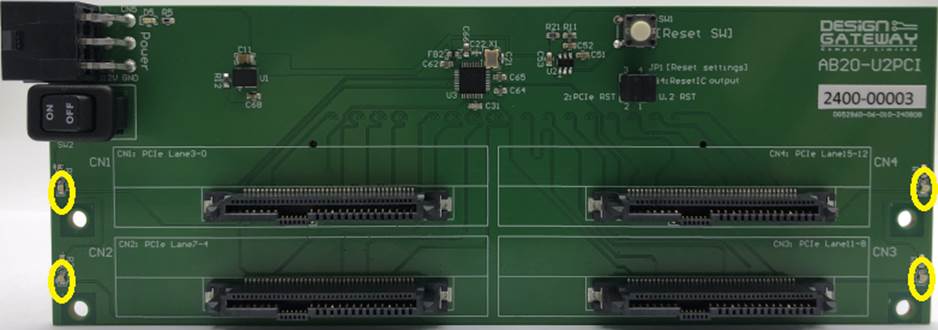

アダプタ基板の部品面には4個のU.2コネクタが実装されており、2.5インチ規格サイズのU.2 SSDを最大4台装着できます。 半田面には16Lane対応のPCIe (PCI Express)コネクタが実装され、Lane3-0/7-4/11-8/15-12がそれぞれCN1/CN2/CN3/CN4に装着されたSSDと接続します。 全チャネルでPCIe Gen5速度での正常動作を実機確認済みです。

本アダプタには低ジッタのクロック発振器やリセット回路が実装され、PCIeおよびU.2 SSDへのクロック/リセット信号へ供給可能です。 本アダプタおよびU.2 SSDへの電源は標準の6ピンタイプPCI Express補助電源から供給します。

本製品には、本アダプタと接続する4台の各SSDドライブを安定して保持するフレーム機構が組み込まれているため、信頼性のある電機接続が維持されます。

FPGAボードに接続した本アダプタとSSDドライブを保持したフレーム機構を下図1に示します。

図1: FPGAボードに接続したアダプタと保持フレーム

本アダプタの特長を以下に示します。

l 16Lane PCI Express対応のU.2 SSD搭載用アダプタ基板

l PCIe Gen5でのFPGA-U.2 SSD間の正常アクセス実機動作確認済み

l 厚さ15mmまでの2.5インチ規格サイズのU.2 SSDを4台まで同時装着可能

l アダプタおよびSSD電源は汎用の外部6pin PCIe補助電源から+12Vで供給

l 本アダプタおよびU.2 SSDへの供給電源はスイッチでON/OFF制御可能

l アダプタ上にPCIe規格の100MHz低ジッタクロック発生源を実装

l PCIeと4台のSSDの計5系統全てに同一位相の100MHz差動クロック信号を供給

l リセットはPCIe-SSD直結とアダプタ基板上のリセット出力をジャンパ・ソケットで選択可

基板外形

本アダプタのフレーム機構を含めたサイズは、横幅166mm 高さ60mm 奥行85mmです。 アダプタ基板の部品面と半田面の基板外観写真をそれぞれ下図2および図3に示します。

図2: アダプタ基板の部品面

図3: アダプタ基板の半田面

電源

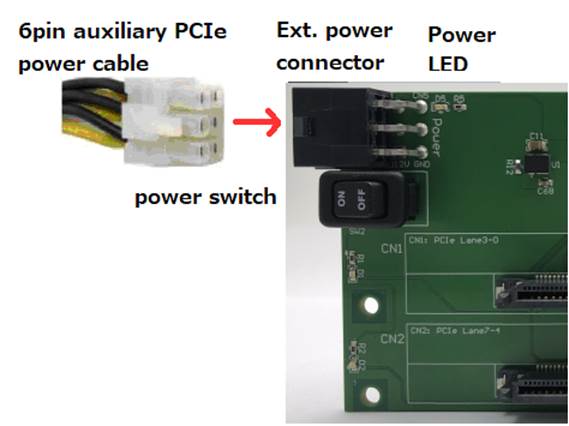

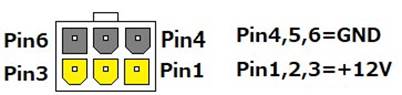

本アダプタおよび装着したSSDへの電源は図4に示すように6ピンタイプのPCIe補助電源から+12Vで供給します。 電源スイッチによりアダプタ基板およびSSDへの+12V電源供給を制御できます。 電源投入状態は電源コネクタ横のLEDで確認可能です。

供給された+12V電源はアダプタ内の電源レギュレータにて動作に必要な+3.3V電源を生成しますが、+3.3V電源はU.2 SSDやPCIeコネクタの+3.3V電源ピンには供給されず、アダプタ内部回路のみに供給されます。 従ってPCIeに接続したFPGAボードへの電源供給は本アダプタのPCIeコネクタ経由ではできません。

図4: 電源スイッチ, PCIe補助電源コネクタおよび電源ピンアサイン

アクセスLED

各U.2コネクタ近傍には図5に示す位置にSSDのアクセスLEDがあり、それぞれのU.2コネクタP11ピン(ACTIVITY#信号)がLowレベルで発光します。

図5: 各SSDのアクセスLED (上図の各黄色枠内)

クロック

本アダプタにはPCI Express Gen5規格対応のクロック・ジェネレータが実装されており、PCIeの差動クロック(A13/A14ピン)および全4チャネルのU.2 SSD用差動クロック(E7/E8ピン)に対して全て同一の位相でシステム・クロックが供給されます。 クロック周波数は100MHz固定で変更できません。

リセット

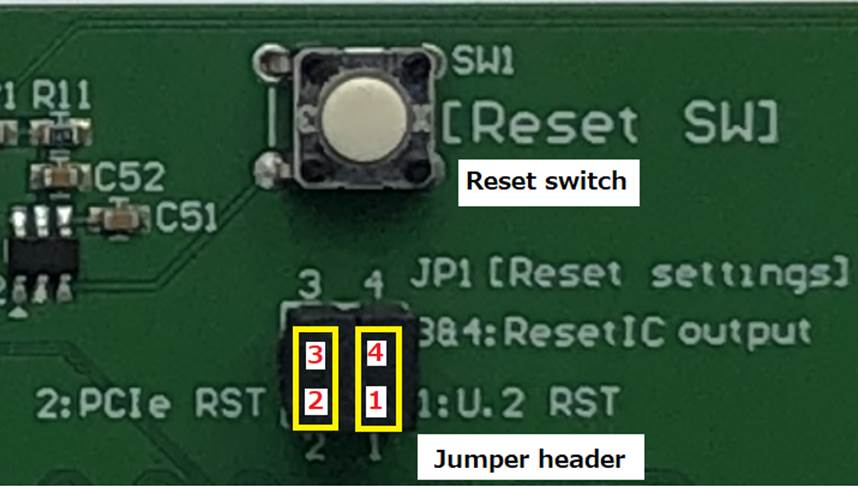

本アダプタにはPCIeおよびU.2のリセット信号を生成するリセットIC, 手動でリセット信号を発生するためのリセットスイッチ、各リセット系統を選択するための2x2ジャンパヘッダが実装されています。

リセットICは+3.3V電源の電圧レベルを常時モニタし約3.0Vを下回った場合にロウ・アクティブのリセット信号を出力します。 またリセットスイッチ押下によっても同様に100msec程度のリセット信号パルスを生成します。

リセット信号の接続は図6に示す2列×2本の4ピンヘッダJP1にソケットを挿入することで以下のように設定可能です。 工場出荷時のソケット設定は図6の1-4間および2-3間の接続(黄色四角枠)となります。

1-4間ショート: リセットIC出力と4個全てのU.2 SSDのリセット(E5ピン)を接続

2-3間ショート: リセットIC出力とPCI Expressのリセット(A11ピン)を接続

1-2間ショート: PCI Expressのリセットと4個全てのU.2 SSDのリセットを接続

図6: リセットスイッチ(SW1)とリセット設定用ピンヘッダ(JP1)

PCIeと各U.2 SSD間の接続

本アダプタにおけるPCIe ソケットの各レーンとCN1-CN4に装着した4台のU.2 SSD間の接続は以下となります。

|

PCIe Lane# (signal direction) |

PCIe signal name |

PCIe Pin# |

U.2 Conn. |

U.2 Pin# |

|

Lane0 Tx (FPGA->PCIe->U.2) |

PERp0/PERn0 |

A16/A17 |

CN1 |

E10/E11 |

|

Lane0 Rx (FPGA<-PCIe<-U.2) |

PETp0/PETn0 |

B14/B15 |

CN1 |

E14/E13 |

|

Lane1 Tx (FPGA->PCIe->U.2) |

PERp1/PERn1 |

A21/A22 |

CN1 |

S17/S18 |

|

Lane1 Rx (FPGA<-PCIe<-U.2) |

PETp1/PETn1 |

B19/B20 |

CN1 |

S21/S20 |

|

Lane2 Tx (FPGA->PCIe->U.2) |

PERp2/PERn2 |

A25/A26 |

CN1 |

S23/S24 |

|

Lane2 Rx (FPGA<-PCIe<-U.2) |

PETp2/PETn2 |

B23/B24 |

CN1 |

S27/S26 |

|

Lane3 Tx (FPGA->PCIe->U.2) |

PERp3/PERn3 |

A29/A30 |

CN1 |

E17/E18 |

|

Lane3 Rx (FPGA<-PCIe<-U.2) |

PETp3/PETn3 |

B27/B28 |

CN1 |

E21/E20 |

|

Lane4 Tx (FPGA->PCIe->U.2) |

PERp4/PERn4 |

A35/A36 |

CN2 |

E10/E11 |

|

Lane4 Rx (FPGA<-PCIe<-U.2) |

PETp4/PETn4 |

B33/B34 |

CN2 |

E14/E13 |

|

Lane5 Tx (FPGA->PCIe->U.2) |

PERp5/PERn5 |

A39/A40 |

CN2 |

S17/S18 |

|

Lane5 Rx (FPGA<-PCIe<-U.2) |

PETp5/PETn5 |

B37/B38 |

CN2 |

S21/S20 |

|

Lane6 Tx (FPGA->PCIe->U.2) |

PERp6/PERn6 |

A43/A44 |

CN2 |

S23/S24 |

|

Lane6 Rx (FPGA<-PCIe<-U.2) |

PETp6/PETn6 |

B41/B42 |

CN2 |

S27/S26 |

|

Lane7 Tx (FPGA->PCIe->U.2) |

PERp7/PERn7 |

A47/A48 |

CN2 |

E17/E18 |

|

Lane7 Rx (FPGA<-PCIe<-U.2) |

PETp7/PETn7 |

B45/B46 |

CN2 |

E21/E20 |

|

Lane8 Tx (FPGA->PCIe->U.2) |

PERp8/PERn8 |

A52/A53 |

CN3 |

E10/E11 |

|

Lane8 Rx (FPGA<-PCIe<-U.2) |

PETp8/PETn8 |

B50/B51 |

CN3 |

E14/E13 |

|

Lane9 Tx (FPGA->PCIe->U.2) |

PERp9/PERn9 |

A56/A57 |

CN3 |

S17/S18 |

|

Lane9 Rx (FPGA<-PCIe<-U.2) |

PETp9/PETn9 |

B54/B55 |

CN3 |

S21/S20 |

|

Lane10 Tx (FPGA->PCIe->U.2) |

PERp10/PERn10 |

A60/A61 |

CN3 |

S23/S24 |

|

Lane10 Rx (FPGA<-PCIe<-U.2) |

PETp10/PETn10 |

B58/B59 |

CN3 |

S27/S26 |

|

Lane11 Tx (FPGA->PCIe->U.2) |

PERp11/PERn11 |

A64/A65 |

CN3 |

E17/E18 |

|

Lane11 Rx (FPGA<-PCIe<-U.2) |

PETp11/PETn11 |

B62/B63 |

CN3 |

E21/E20 |

|

Lane12 Tx (FPGA->PCIe->U.2) |

PERp12/PERn12 |

A68/A69 |

CN4 |

E10/E11 |

|

Lane12 Rx (FPGA<-PCIe<-U.2) |

PETp12/PETn12 |

B66/B67 |

CN4 |

E14/E13 |

|

Lane13 Tx (FPGA->PCIe->U.2) |

PERp13/PERn13 |

A72/A73 |

CN4 |

S17/S18 |

|

Lane13 Rx (FPGA<-PCIe<-U.2) |

PETp13/PETn13 |

B74/B75 |

CN4 |

S21/S20 |

|

Lane14 Tx (FPGA->PCIe->U.2) |

PERp14/PERn14 |

A76/A77 |

CN4 |

S23/S24 |

|

Lane14 Rx (FPGA<-PCIe<-U.2) |

PETp14/PETn14 |

B70/B71 |

CN4 |

S27/S26 |

|

Lane15 Tx (FPGA->PCIe->U.2) |

PERp15/PERn15 |

A80/A81 |

CN4 |

E17/E18 |

|

Lane15 Rx (FPGA<-PCIe<-U.2) |

PETp15/PETn15 |

B78/B79 |

CN4 |

E21/E20 |

表1: PCIe各レーンと4台のU.2 SSD間の接続

免責事項

本アダプタを誤って使用することにより生じたFPGA評価基板あるいはSSDデバイスの損傷については、その一切を免責事項とさせていただきます。 また、本アダプタ基板はあくまで評価を目的としたものであり、FPGA評価ボードや接続先SSDデバイスの特性によっては正常に動作しない可能性がありますが、アダプタ基板の製造不良以外は免責となります。

[問い合わせ先]

URL : https://dgway.com/index.php

Email : info@dgway.com

改版履歴

|

リビジョン |

日付 |

内容 |

|

1.0J |

2024/10/7 |

日本語版の初版発行 |

|

|

|

|