## **SATA-IP Introduction (Intel)**

Ver1.9E

7 October 2019 Design Gateway Page 1

### **Agenda**

- SATA Overview

- Summary, Features and Trend

- Merit and Solution

- SATA-IP Introduction

- Summary

- Application

### What is SATA?

- Standard storage interface of HDD/SSD

- SATA1.0 released in year 2000, the latest standard is SATA3.0.

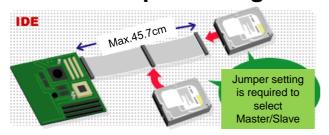

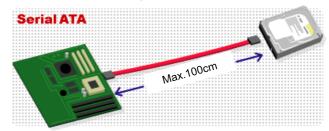

- Improved from IDE (Parallel-ATA)

- Cable (from 80 line 46cm to flat narrow cable 1m)

- High-speed (PATA: Max.133MB/s -> SATA: Max.600MByte/s)

- Jumper setting is not required anymore.

7 October 2019 Design Gateway Page 3

### **Features of SATA device**

- Popular

- Compatibility. Easy to replace.

- Commodity. Easy to buy.

- Low price

- 2.5"SSD 480GB is 50USD

- 3.5"HDD 4TB is 80USD

(06-Jan-2019 Amazon.com)

### Trend of SATA device

- SATA storage is switching to SSD from HDD.

- SSD has advantage compared with HDD in toughness & silence.

- HDD has advantage compared with SSD in capacity and price.

|                          | HDD                 | SDD            |

|--------------------------|---------------------|----------------|

| Life Expectancy          | में में मे          | के के के के के |

| Operating Temperature    | ये ये ये            | ****           |

| Storage Temperature      | ये ये ये ये         | ****           |

| Operating Shock          | \$                  | ***            |

| Operating Vibration      | 7 <b>.</b> 7        | ****           |

| Humidity                 | ये ये ये ये         | ***            |

| Altitude                 | क्रे क्रे क्रे      | ***            |

| Acoustic Noise           | ये ये ये            | के के के के के |

| Raw Media Error Rate     | क्रे क्रे क्रे      | ***            |

| Apps Data Error Rate     | क्रे क्रे क्रे क्रे | ***            |

| Performance - Sequential | प्रे प्रे प्रे प्रे | ये ये ये ये    |

| Performance - Random     | क्रे क्रे           | * * * *        |

| PowerIdle                | प्रे प्रे प्रे      | ***            |

| Power Read/Write         | क्रे क्रे           | * * * *        |

| Capacity                 | ये ये ये ये ये ये   | ***            |

| Cost/IOPS                | र्ज र्ज र्ज         | क्रे क्रे क्रे |

| Cost/MBps                | ये ये ये ये         | ये ये ये       |

| Cost/GB                  | के के के के के      | क्रे क्रे क्रे |

7 October 2019 Design Gateway Page 5

### **Merit of SATA adoption**

- Huge non-volatile storage

- GigaByte/TeraByte capacity.

- High-speed and Low cost

- Several Megabyte per second Read/Write speed

- Mass produced goods

- Compatibility

- Easy and quick to repair and recover, just replace.

- Your product lineup will be various with different capacity storages

Just change storage capacity to arrange various products from high-end model to low cost model.

### Solution for embedded system

- 1: Use Existing SATA chip (ASSP)

- Merit: Device cost

- Demerit: Limitation of MOQ, support and fixed function

- 2: Use FPGA+SATA-IP core

- Merit: Flexibility, support special usage such as RAID, MOQ etc..

- Demerit: Device cost (In case of SATA function only)

#### **Conclusion:**

If the system is simple function and the availability is acceptable, ASSP may be better for you.

For other case, FPGA + SATA-IP core is best solution for you!!

7 October 2019 Design Gateway Page 7

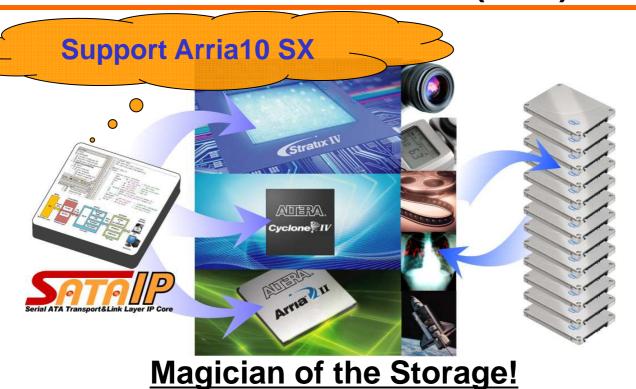

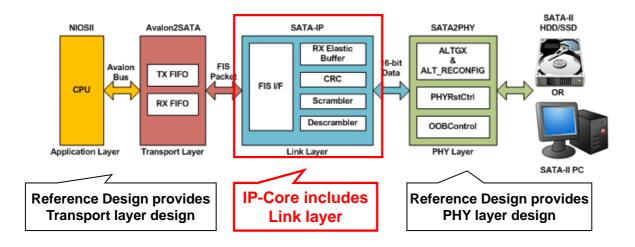

### What is SATA-IP?

- Implement SATA channel by transceiver resource.

- IP-Core includes Link layer (and some part of Transport layer).

- Reference Design available for PHY layer and Transport layer.

### **Product Lineup**

| Prod. No.     | Device       | Speed    | Available reference design        |

|---------------|--------------|----------|-----------------------------------|

| SATA-IP-A10SX | Arria10 SX   | SATA-III | Host                              |

| SATA-IP-A10GX | Arria10 GX   | SATA-III | Host                              |

| SATA-IP-A5GX  | ArriaV GX    | SATA-III | 4chRAID, Host, HostIP, exFAT      |

| SATA-IP-A5ST  | ArriaV ST    | SATA-III | Host, Linux(AHCI)                 |

| SATA-IP-S5GX  | StratixV GX  | SATA-III | 4chRAID, Host                     |

| SATA-IP-S4GX  | StratixIV GX | SATA-III | 4chRAID, Host, HostIP, Duplicator |

| SATA-IP-C5SX  | CycloneV SX  | SATA-II  | Host, Linux(AHCI)                 |

Stratix/Arria family supports SATA3.0 (6Gbps)

Many reference design available (Can check operation for evaluation)

7 October 2019 Design Gateway Page 9

### **Supports both of Host and Device**

- Single IP-Core supports both of Host (PC side) and Device (Disk side).

- Select between Host function and Device function by dev\_host\_n signal input.

### **Approved IP-Core by Intel**

**DesignGateway is DSN partner of Intel**

7 October 2019 Design Gateway Page 11

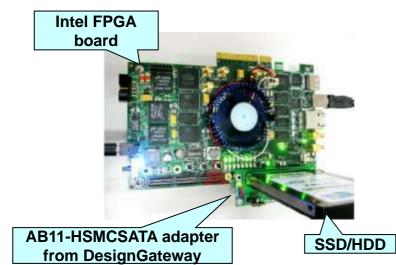

### Free SOF-file for Evaluation

- Write/Read access to SATA device from Intel board.

- Measure real SATA drive performance.

```

Enter Sector Count: 1 - 0x1dcf32lv: 0x1000000

Write Pattern?: [0]Inc32 [1]Dec32 [2]All_0 [3]All_1: 1

Prepare Data... Data Ready

Speed = 279 MB/s

Main Menu

0. SAIA Reset

1. IDENITY DEUICE

2. Write COMMAND

4. Dump Data

3. Read COMMAND

4. Dump Data

6. Sair LBA: 0 - 0x1dcf32af: 0

Enter Sector Count: 1 - 0x1dcf32b0: 0x1000000

Speed = 480 MB/s

Main Menu

0. SAIA Reset

1. IDENITY DEUICE

2. Write COMMAND

```

**Execute command via Nios2-terminal**

**Evaluation Environment (StratixIV GX version)**

## **Reference Design (Summary)**

- QuartusII project attached to the deliverables

- Full source code (VHDL) except IP core

- Can save user system development duration

- Confirm real board operation by original reference design.

- Then modify a little to approach final user product.

- Check real operation in each modification step.

No risk to back to rebuild, able to develop for short term!

7 October 2019 Design Gateway Page 13

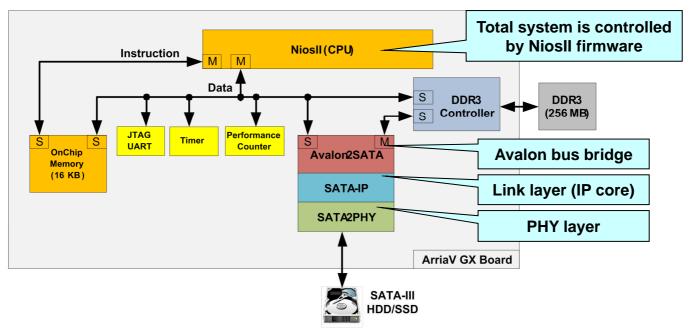

## Reference Design (Structure)

Block diagram of SATA-IP reference design

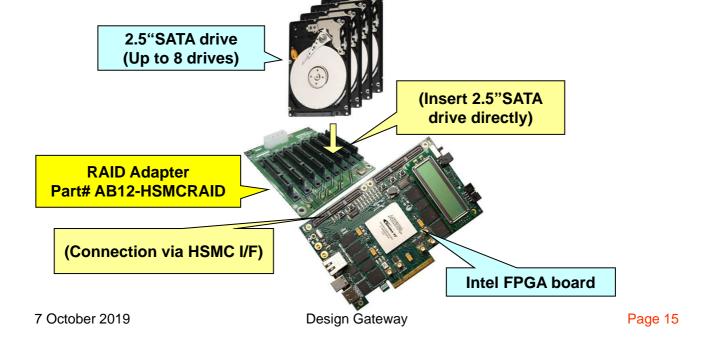

### **Development tool for RAID system**

- HSMC extension board with 8 SATA connectors.

- Direct connect to 2.5 inch SSD or HDD.

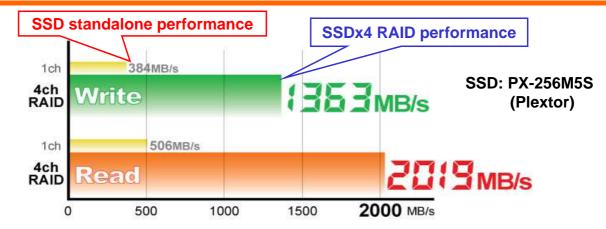

## **RAID System Performance**

- 1.4GB/s for Write speed (RAID efficiency = 89%)

- Enough speed for Super high resolution video recording

- 2GB/s for Read speed (RAID efficiency = 99.8%)

- SSD drive count minimized for video playback system

### **SATA-IP Optional Product**

#### HCTL-IP Core

- Pure hard-wired host controller core

- Automatic read/write execution without CPU

- Best performance because firmware overhead not exist

#### AHCI-IP Core

- SATA access possible from LinuxOS

- Support ARM Core for SoC family

#### FAT32-IP/exFAT-IP

- Provide FAT32/exFAT access feature by hardwired logic

- Can record data as 'file' -> PC can access to data via file

7 October 2019 Design Gateway Page 17

## **HCTL-IP Core (Optional Product)**

- Controller IP core designed by pure hard-wired logic

- Full autimatic SATA-IP control instead of CPU and its firmware

- Can build storage system without CPU

- Can save CPU time completely in SoC application system

- Minimize overhead by high speed state machine

- Theoretically the best performance (especially for write)

- Write improvement example: CPU control=465MB/s -> Host-IP=525MB/s

- Provides reference design for both 1ch and 4ch-RAID0 on Intel board

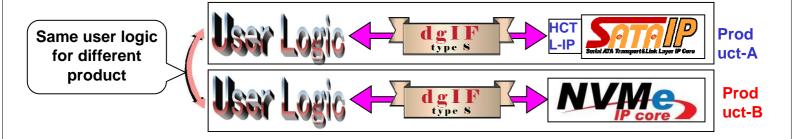

## **HCTL-IP Core (Cont'd)**

- Common interface among all Storage IP-Core (dgIF typeS)

- Same user interface among other IP-Core (NVMe-IP) product

- Can keep same user logic for different storage between SATA and NVMe

- Simple user interface for easy use

- Set R/W type, address, sector count parameter and issue request pulse

- Very popular data interface by general FIFO

7 October 2019 Design Gateway Page 19

### **AHCI-IP Core (Optional Product)**

- Can access to SATA channel from Linux

- Reference design available for SoC device

- Provide AHCI Linux driver C source code

- Supports NCQ feature

- Queue re-order in multiple command

- Minimum latency by using internal RAM for Queue table

- Very high performance for random access

- Multiple port count support by customization

- Standard product support 1 port

- Port count can be increased by core customization

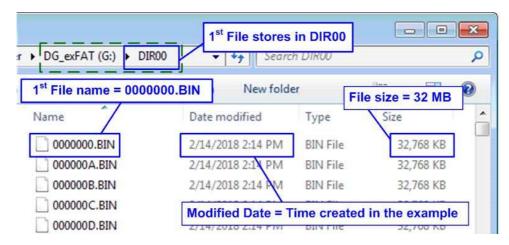

## FAT32-IP/exFAT-IP Core (Optional Product)

- Supports data recording by FAT32/exFAT file format

- In combination with both SATA-IP and HCTL-IP core

- PC can directly access to recorded data as a file

- FPGA writes data to device, reconnect with PC, then PC can read data

PC can directly read recorded data as a file

7 October 2019 Design Gateway Page 21

### FAT32-IP/exFAT-IP (Cont'd 1)

### Feature description

- Executes drive format and data write to file by pure hardwired logic.

- IP core automatically generates file name.

- User logic sends file data via FIFO interface.

#### Limitation

- Drive must be formatted by the IP core, not by the PC.

- Files other than those generated by the IP core cannot be written to the drive.

- File size is determined at format execution and cannot be changed.

### FAT32-IP/exFAT-IP (Cont'd 2)

- Reference design for real operation available

- Executes test file generation via serial console.

- User can confirm file read compatibility by drive re-plug to the PC.

Generate test file, reconnect with PC, and can check file read compatibility

7 October 2019 Design Gateway Page 23

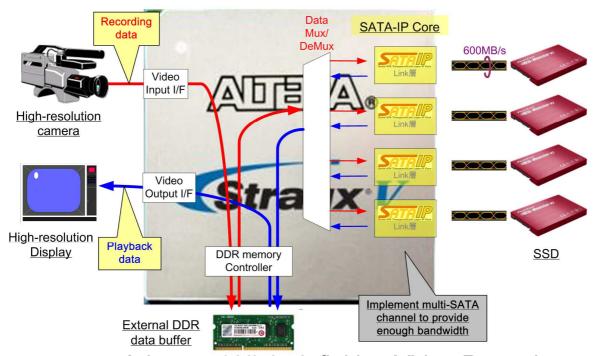

## **SATA-IP Application (1)**

Advanced High-definition Video Recorder

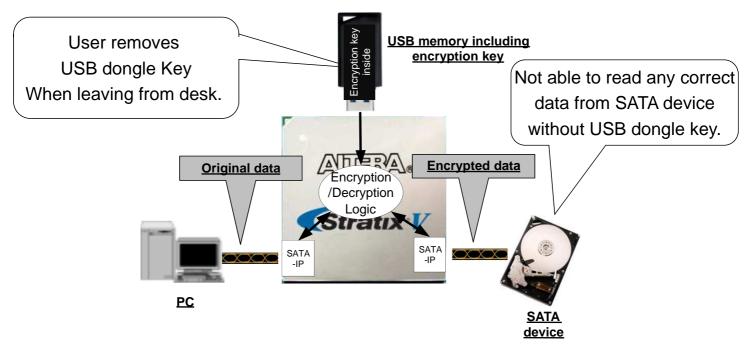

### **SATA-IP Application (2)**

Security Drive System

7 October 2019 Design Gateway Page 25

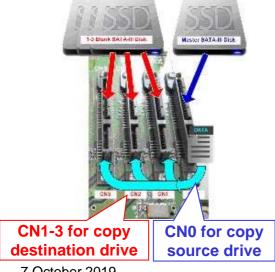

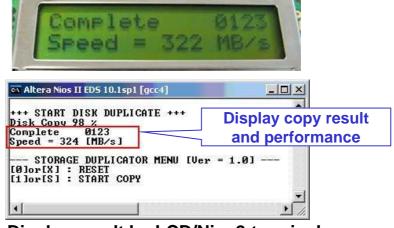

## **SATA-IP Application (3)**

- Duplicator Application Reference Design

- Copy whole data from Master drive to multiple Slave drives

- Reference design for StratixIV GX board

- Design project available for formal SATA-IP customer

**Display result by LCD/Nios2-terminal**

7 October 2019 Design Gateway Page 26

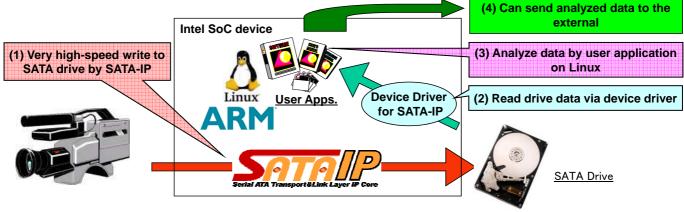

### **SATA-IP Application (4)**

- Recording and Analysis system on Linux

- Mount Linux and user analysis application on SoC device

- Very high-speed data recording to SATA drive via SATA-IP core

- Data read from SATA drive via device driver and analyze by user application

Recording and Analysis sytem on Linux (device driver and reference design available)

7 October 2019 Design Gateway Page 27

### For more detail

- Detailed documents available on the web site.

- http://www.dgway.com/SATA-IP\_A\_E.html

- Contact

- Design Gateway Co,. Ltd.

- E-mail : sales@design-gateway.com

- FAX: +66-2-261-2290

# **Revision History**

| Rev. | Date      | History                                                                                               |

|------|-----------|-------------------------------------------------------------------------------------------------------|

| 1.0  | 04-Feb-09 | English version initial release                                                                       |

| 1.3  | 31-Jul-12 | Add introduction of summary of SATA Update explanation of RAID development tool (AB12-HSMCRAID board) |

| 1.6E | 27-Jul-16 | Add Arria10SoC support                                                                                |

| 1.7E | 03-Apr-17 | Add common user interface (dglF typeS) and its merit description for SATA Host-IP                     |

| 1.8E | 06-Jan-19 | Add FAT32-IP/exFAT-IP for SATA-IP optional products                                                   |

| 1.9E | 04-Oct-19 | Add Linux application example                                                                         |

|      |           |                                                                                                       |

|      |           |                                                                                                       |

|      |           |                                                                                                       |

|      |           |                                                                                                       |

|      |           |                                                                                                       |

|      |           |                                                                                                       |

|      |           |                                                                                                       |

|      |           |                                                                                                       |

|      |           |                                                                                                       |

|      |           |                                                                                                       |

|      |           |                                                                                                       |

|      |           |                                                                                                       |

|      |           |                                                                                                       |

7 October 2019 Design Gateway Page 29