# シリアル ATA-IP コアのご紹介

アルテラ版 2011/10/11

#### IP コア概略

デザイン・ゲートウェイのシリアル ATA(SATA) IP コアは、SATA チャネルを Altera 製 FPGA で実装するためのリンクレイヤ IP コアで、StratixIV GX, ArriaII GX および CycloneIV GX に対応しております。StratixIV GX 版は最新 SATA-III 規格(6Gbps)に対応し、SATA-III 対応 SSD のパフォーマンスを最大限に引き出します。FPGA 内蔵トランシーバをそのまま SATA ポートとして構築するため外部 PHY チップは不要となります。Altera 製評価ボードで実機動作するソースコードつきのリファレンス・デザインが製品に標準添付されているため、短期間の製品開発が可能となります。

また、Altera 社製 StratixIV GX, ArriaII GX および CycloneIV GX FPGA 開発キット用デモファイルを準備しておりますので、購入前に本コアを実機で評価・お試し頂けます。

#### 特長

- Serial ATA 規格 revision 3.0 に準拠

- ホスト側のみならずデバイス側の動作もサポート(SATA 周辺機器開発への応用が可能)

- シンプルな Host プロセッサ向けトランザクション I/F および DMA I/F

- Host I/F は 32bit 幅

- 送受信データパスで BRAM による 4KB の FIFO を実装

- SATA II/III をサポート (SATA III は StratixIV GX に対応。ArriaII GZ にも近日中対応)

- コアロジック自体はタイミングにフィットしやすい低速動作

- o SATA-II: IPコア部は 75.0MHz 動作で PHY 部は 150MHz 動作

- o SATA-II: IPコア部は 150MHz 動作で PHY 部は 300MHz 動作 (StratixIV GX)

- EMI 低減のための CONT プリミティブをサポート

- 20bit 幅の PHY インターフェイス

- StratixIV GX, ArriaII GX および CycloneIV GX FPGA 開発キットで購入前のコア実機評価が可能

- 安心の国内サポート

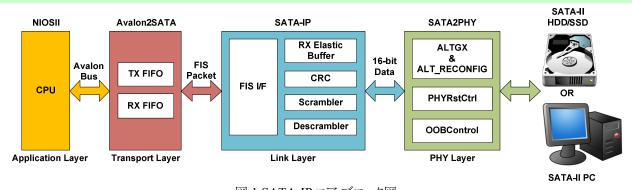

#### ブロック図

図 1 SATA-IPコア ブロック図

#### 使用リソース

表1: コンパイル結果

| Family        | Example Device  | Fmax<br>(MHz) | Combinational ALUTs <sup>1</sup> | Registers <sup>1</sup> | Pin <sup>2</sup> | Block<br>Memory bit | GXB <sup>3</sup> | Design<br>Tools |

|---------------|-----------------|---------------|----------------------------------|------------------------|------------------|---------------------|------------------|-----------------|

| Stratix IV GX | EP4SGX230KF40C2 | 322           | 1,486                            | 2,390                  | 141              | 33,792              | 1                | QuartusII 10.1  |

| Cyclone IV GX | EP4CGX150DF31C7 | 232           | 3,303                            | -                      | 141              | 33,792              | 1                | QuartusII 10.1  |

| Arria II GX   | EP2AGX125EF35C4 | 256           | 1,484                            | 2,390                  | 141              | 33,792              | 1                | QuartusII 10.1  |

#### 備考:

- 1)実際の消費リソースはユーザロジックやフィット条件等に依存します

- 2)このサンプルはコアの全 I/O とクロックがチップ外部と直接インターフェイスするケースでのコンパイル結果となります

- 3)SATA-IPコア自体ではGXBは使用しませんが、PHYレイヤにて必要となるため表1に含めております。

#### 提供物

本 IP 納品時には下記の物が含まれます。

- IP コア本体(Encrypt されたネットリスト)

- テストベンチ(ModelSIM対応),Simulationライブラリ

- NIOS II プロジェクトリファレンスデザイン

- データシート、ユーザガイド、デザインガイド

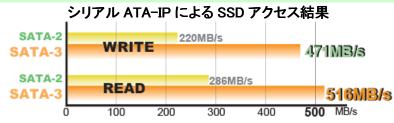

### 動作確認状況・パフォーマンス

本 IPコアは SATA-II/III に対応しているため、 HDD および SSD のパフォーマンスを最大限に引き出します。

Seagate, IBM/Hitachi, WesternDigital および Samsung 製 HDD、Intel, PhotoFast, OCZ および Micron 製 SSD での動作を確認しております(2011年7月現在)。

- ※ Stratix IV GX FPGA 開発キット/NIOS II でのホスト評価

- ※ SATA-2 は Intesl X25-E Extreme SSDSA2SH032G1 を使用

- ※ SATA-3 は OCZ AGT3-23SAT3-60G を使用

- ※ データサイズ 32MB, 0-fill パターンで全容量 60GB をシーケンシャルで一括 Read/Write

## FPGA 開発キットですぐに開発・評価

SATA-IP コア付属のリファレンスデザインは、StratixIV GX, ArriaII GX および CycloneIV GX FPGA 開発キット用にデザインされており、本 IP コアの評価および本コアを使用したロジック開発ををすぐに行なうことができます。

また StratixIV GX, ArriaII GX および CycloneIV GX FPGA 開発キット用 時間限定版 sofファイルを準備しておりますので、購入前に評価することができます。詳しくは弊社ウェブサイトをご覧下さい。

※ SATA/SAS HSMC Card および NIOS II が別途必要です。

時間限定版 sofファイルの評価デモ「StratixIV GX/SATA-3 編」が youtube に公開されております。

SATA-IP StratixIV

検索

で検索