# SATA Host Demo on Altera V-series/10-series Instruction

Rev2.1 1-Aug-16

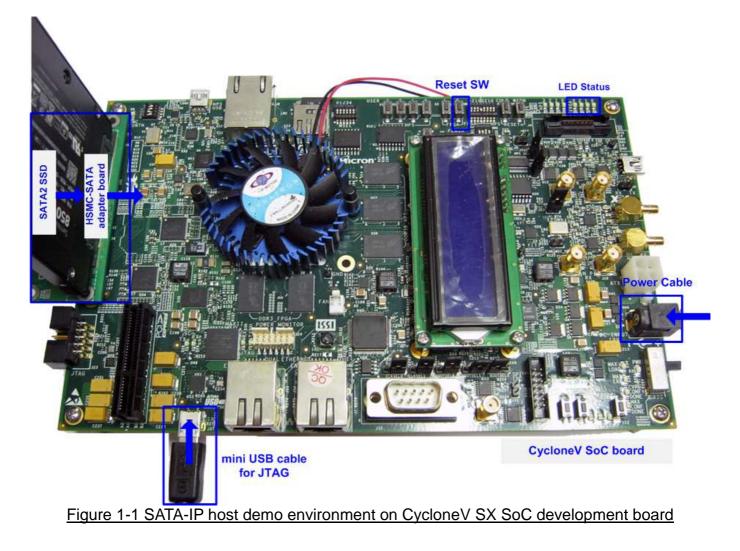

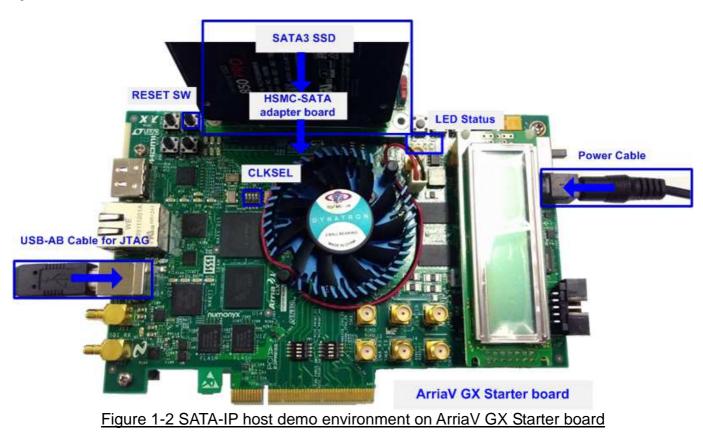

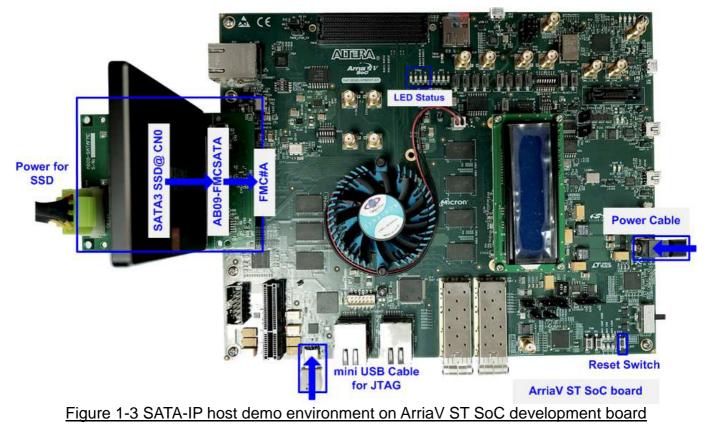

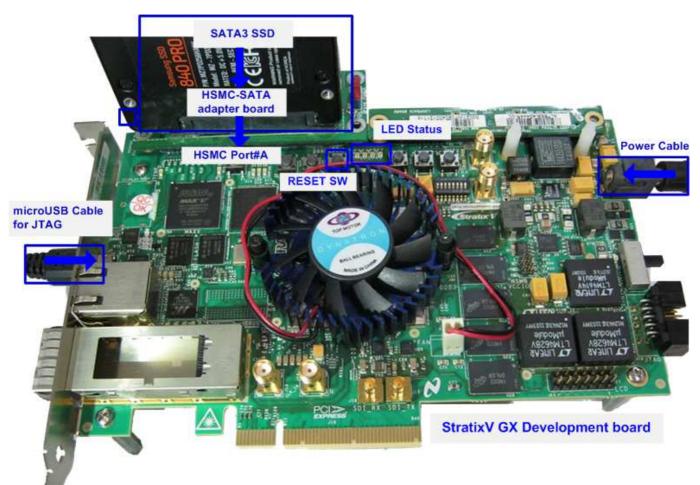

This document describes the instruction to run SATA-IP host demo on Altera development board, i.e. CycloneV SX SoC, ArriaV ST SoC, ArriaV GX Starter, StratixV GX, and Arria10 SoC development board. From device limitation, CycloneV SX SoC board can support only SATA2 while other boards can support SATA3 device.

### 1 Environment Setup

To run SATA host demo, FMC SATA or HSMC SATA adapter board from Design Gateway is required to be interface board between FPGA development board and SATA-III/SATA-II HDD/SSD. Hardware connection for each development board is shown in Figure 1-1 - Figure 1-5.

Figure 1-4 SATA-IP host demo environment on StratixV GX development board

Following step is setup procedure for running demo.

- Power off FPGA board and adapter board.

- Connect HDD/SSD to SATA socket on CN0 @ HSMC/FMC SATA adapter board

a) For Cyclone V SoC board, insert SATA-II HDD/SSD.

b) For other boards, insert SATA-III HDD/SSD.

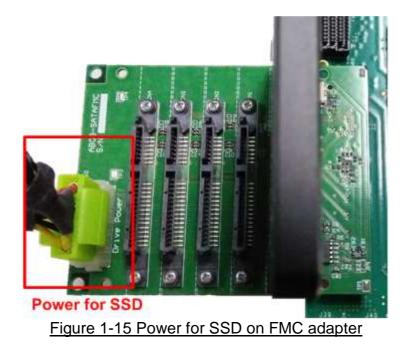

- For FMC adapter board, connect power to power connector on FMCSATA board.

- Connect SATA adapter board to FPGA board.

Note: If FPGA board has FMC/HSMC port more than one, use port#A.

- Connect USB A/B, USB mini, or USB micro cable between FPGA board and PC for JTAG programming and JTAG UART.

- Connect power supply to FPGA board.

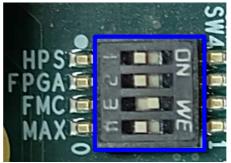

- For CycloneV SX SoC or ArriaV ST SoC board, set JTAG enable at SW4 as shown in Figure 1-6 to enable FPGA and MAX in JTAG chain.

Figure 1-6 Enable FPGA and MAX JTAG on CycloneV SoC and ArriaV SoC board

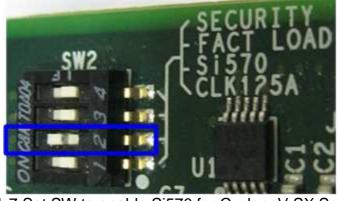

- Enable clock programmable for CycloneV SX SoC, ArriaV GX board, or Arria10 SoC board.

- a) For CycloneV SX SoC board, set bit2 of SW2 to ON position.

Figure 1-7 Set SW to enable Si570 for CycloneV SX SoC board

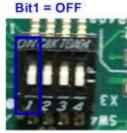

b) For ArriaV GX board, set bit1 of SW4 to OFF position.

Figure 1-8 Set SW to select clock input for ArriaV GX Starter board

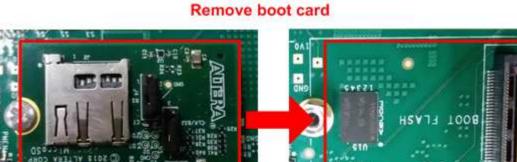

c) For Arria10 SoC board, remove boot card from the board.

Figure 1-9 Remove boot card from Arria10 SoC board

- Power on FPGA board.

0

- Open "Clock Control" application to program clock for CycloneV SX SoC, ArriaV GX board, and StratixV GX board.

- a) For CycloneV SX SoC board, select 1<sup>st</sup> tab (Si570), set Target frequency = 150 MHz, and click "Set New Frequency" button.

| Clock Control                                    | U29                                              |                                                                                                                                     |

|--------------------------------------------------|--------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| Serial port r<br>HS_DIV<br>N1<br>RFREQ<br>fXTAL: | egisters<br>9<br>4<br>02f411261e<br>114.2756 MHz | Target frequency(MHz)<br>150 MHz<br>Valid frequency range values are<br>10.00000000 to 810.0000000 MHz<br>Default Set New Frequency |

|                                                  | to the targe                                     | t<br>iency for CycloneV SX SoC boar                                                                                                 |

b) For ArriaV GX board, select 1<sup>st</sup> tab (U4), set CLK0 frequency = 150 MHz, and click "Set New Frequency" button.

| \land Clock Contro                                  | I                         |              |                     | x |

|-----------------------------------------------------|---------------------------|--------------|---------------------|---|

|                                                     |                           |              |                     |   |

| F_vco                                               | : 000MHz                  |              | Disable all 🥅       |   |

| Registers<br>CLk0                                   | -                         | Frequency (  | (MHZ) 🗠             |   |

|                                                     |                           | 150          | ).00 Disable CLK0 📃 |   |

| CLK1                                                | -                         | CLK1 150     | 0.00 Disable CLK1 📃 |   |

| CLK2                                                | -                         | CLK2 150     | 0.00 Disable CLK2   |   |

| СГКЗ                                                | -                         | CLK3 150     | 0.00 Disable CLK3   |   |

|                                                     | read                      | Defa         | Set New Frequency   |   |

| Messages                                            |                           |              |                     |   |

|                                                     | sterII on lo<br>SPM221002 | )calhost (US | (B-1)/5M(1270ZF324  | * |

| Figure 1-11 Set clock frequency for ArriaV GX board |                           |              |                     |   |

- c) For StratixV GX board, select 3<sup>rd</sup> tab (U38), set CLK0 frequency = 150 MHz, and click "Set New Frequency" button.

| \land Clock Contro | I            |             |                                |

|--------------------|--------------|-------------|--------------------------------|

| Si570 Si571        | U38 U46      |             |                                |

| F_vco<br>Registers | : 2550,0000  | Frequency ( | <sub>(MHz)</sub> Disable all 🦳 |

| CLKO               | 150.0000     |             | 0.00 Disable CLK0 🕅            |

| CLK1               | 150.0000     | CLK1 150    | 0.00 Disable CLK1              |

| CLK2               | 150.0000     | CLK2 150    | 0.00 Disable CLK2              |

| CLK3               | 150.0000     | CLK3 150    | 0.00 Disable CLK3              |

|                    | read         | Defa        | ault Set New Frequency         |

| Messages           |              |             |                                |

| Connected          | l to the tar | get         |                                |

| Figure 1-1         | 2 Set clock  | frequency   | for StratixV GX board          |

- Open QuartusII Programmer and download SOF file to FPGA board, as shown in Figure 1-13.

Figure 1-13 Programmer Environment

- Power-on supply to SATA SSD.

- a) For HSMC adapter, ON power-switch on HSMC adapter which is power supply for SATA SSD/HDD, as shown in Figure 1-14.

b) For FMC adapter, ON power supply which is connected to power connector on the adapter, as shown in Figure 1-15.

Check LED status on FPGA board now and LED0-1 should be ON, as shown in Figure 1-16.

Figure 1-16 LED Status after setup complete

| LED                                         | ON                               | OFF                                                                                    |

|---------------------------------------------|----------------------------------|----------------------------------------------------------------------------------------|

| LED0                                        | ОК                               | SATA-IP cannot detect SATA device. Please check SATA-cable connection or 150 MHz clock |

|                                             |                                  | source.                                                                                |

| LED1                                        | OK                               | Internal PLL is not LOCK.                                                              |

| LED2                                        | In process of write SATA HDD/SSD | Idle Status                                                                            |

| LED3                                        | In process of read SATA HDD/SSD  | Idle Status                                                                            |

| Table 1 LED Status of host reference design |                                  |                                                                                        |

- Open NiosII Command Shell.

- Type "nios2-terminal" and then boot-up screen with Main menu for running SATA host demo is displayed, as shown in Figure 1-17. More details about each Menu are described in next topic.

| 🔜 /cygdrive/c/altera/15.1                                                                                                                                                                                            |              | -O× |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-----|

| Altera Nios2 Command Shell [GCC 4]<br>Version 15.1, Build 189                                                                                                                                                        |              |     |

| Pat@PatPC /cugdrive/c/altera/15.1<br>5 nios2-terminal<br>nios2-terminal: connected to hardware target usin<br>nios2-terminal: "USB-BlasterII [USB-1]", device 1<br>nios2-terminal: (Use the IDE stop button or Ctrl- | , instance Ø |     |

| Starting Nios II                                                                                                                                                                                                     |              |     |

| SATA3 Host Reference Design Ver 1.4<br>Waiting device ready<br>Reset in loop.                                                                                                                                        | Main menu    |     |

| SATA host design menu [Ver = 1.4]<br>[0] : SATA RESET<br>[1] : IDENTIFY DEUICE<br>[2] : WRITE DMA (EXT)<br>[3] : READ DMA (EXT)<br>[4] : DUMP DATA                                                                   |              |     |

Figure 1-17 Run NIOSII Terminal and boot-up screen

## 2 Main Menu

#### 2.1 SATA RESET

Select '0' for sending hardware reset signal to SATA-IP. Hardware reset is designed to reset both SATA-IP and SATA-PHY module. The system will re-initialize, and main menu will be displayed when complete reset sequence, as shown in Figure 2-1.

| /cygdrive/c/altera/15.1                                                                                                                            | _ 🗆 🗙    |

|----------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 0                                                                                                                                                  | <u> </u> |

| +++ SATA RESET selected +++<br>Reset in loop.                                                                                                      | _        |

| SATA host design menu [Ver = 1.4]<br>[0] : SATA RESET<br>[1] : IDENTIFY DEVICE<br>[2] : WRITE DMA (EXT)<br>[3] : READ DMA (EXT)<br>[4] : DUMP DATA | -        |

| •                                                                                                                                                  | <u>)</u> |

Figure 2-1 SATA RESET Menu

#### 2.2 IDENTIFY DEVICE

Select '1' for sending "IDENTIFY DEVICE" command to HDD/SSD. Disk information (Model name, 48-bit LBA supported, disk capacity) will be displayed by using this menu, as shown in Figure 2-2.

| 💷 /cygdrive/c/altera/15.1                                                                                                                                               |                 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

|                                                                                                                                                                         | <u> </u>        |

| +++ IDENTIFY DEVICE selected +++<br>Model name : Samsung SSD 850 PRO 256GB<br>48bit LBA is supported<br>Capacity : 256GB (MAX LBA = 500118192)<br>UDMA mode 6 supported |                 |

| SATA host design menu [Ver = 1.4]<br>[0] : SATA RESET<br>[1] : IDENTIFY DEVICE<br>[2] : WRITE DMA (EXT)<br>[3] : READ DMA (EXT)<br>[4] : DUMP DATA                      |                 |

| •                                                                                                                                                                       | •<br><i>ا</i> ا |

Figure 2-2 IDENTIFY DEVICE Menu

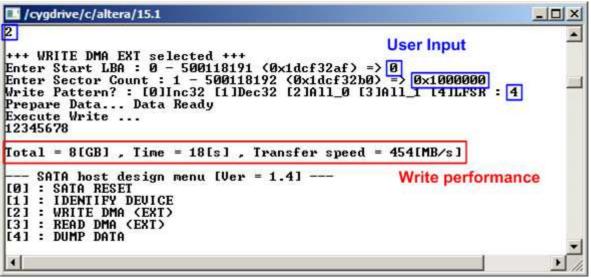

#### 2.3 WRITE DMA (EXT)

Select '2' for sending "WRITE DMA (EXT)" command to HDD/SSD. Three inputs are required for this menu, i.e.

- Start LBA: this value is the start sector number of HDD/SSD to write data.

- Sector Count: this value is the total transfer size in sector unit (512 byte) for writing HDD/SSD. The data size which CPU filled to write buffer is equal to this input. If the input is more than 65536 (maximum size for one SATA command), only 65536 sector data is filled and the later command will use same data area with the first command.

- Write Pattern: this value is used for selecting test pattern to write to buffer and then forward to HDD/SSD. There are five test patterns in this demo, i.e. 32-bit increment [0], 32-bit decrement [1], 0000000H [2], FFFFFFH [3], and LFSR counter [4].

After Software receives all inputs correctly,

- "Prepare data" will be displayed during CPU writing test pattern data to write buffer.

- "Execute Write" will be displayed during CPU sending WRITE DMA (EXT) command and transferring data from write buffer to HDD/SSD.

- Transfer speed will be displayed after write operation complete.

Figure 2-3 shows the example of test result when operation complete. Write operation will be cancelled when receiving error input as shown in Figure 2-4.

Figure 2-3 WRITE DMA (EXT) command input and output

Figure 2-4 Write operation cancelled from error input

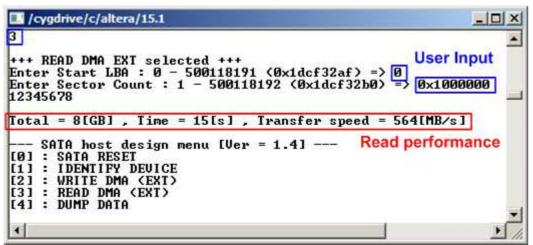

#### 2.4 READ DMA (EXT)

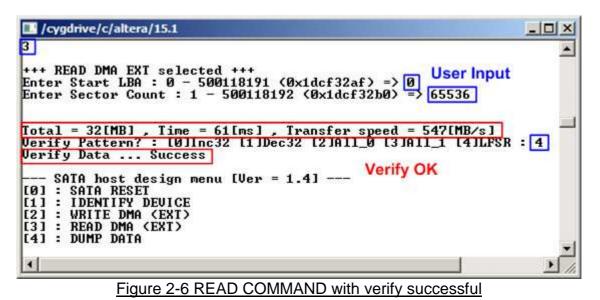

Select '3' for sending "READ DMA (EXT)" command to HDD/SSD. Two or three inputs are required for this menu, i.e.

- Start LBA: same description with Start LBA in WRITE DMA (EXT) menu.

- Sector Count: same description with Sector Count in WRITE DMA (EXT) menu. If this input is not more than 65536, the third input will be displayed for selecting verification pattern. If input is more than 65536, the third input will not be displayed to skip data verification process and run for checking performance only, as shown in Figure 2-5.

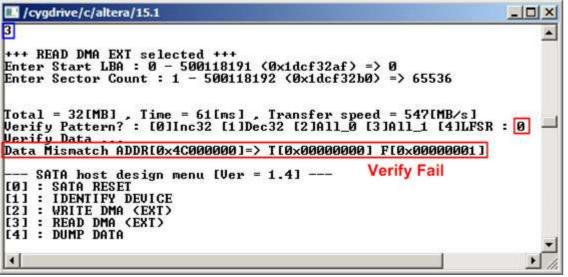

- Verify Pattern (Optional): this value is used for selecting verification pattern. This input should be matched with the pattern in WRITE DMA (EXT) menu. Five verification patterns can be selected, similar to write pattern. "Verify Data ... Success" is displayed for success case, and "Data Mismatch with failure value" is displayed for failure case, as shown in Figure 2-6 and Figure 2-7 sequentially.

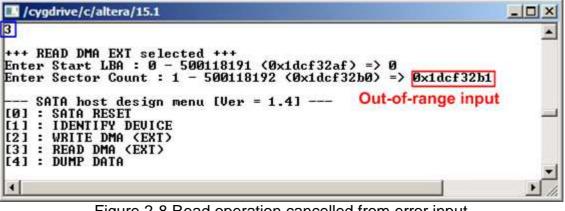

Similar to WRITE DMA (EXT) menu, Read operation will be cancelled if receiving error input as shown in Figure 2-8.

Figure 2-5 READ COMMAND without Verify

Figure 2-7 READ COMMAND with verify failure

Figure 2-8 Read operation cancelled from error input

#### 2.5 DUMP DATA

Select '4' to read data from DDR or read control register inside Avalon2SATA module for debugging. Two inputs are required for this menu, i.e.

- Start address: Heximal value can be input by adding prefix "0x". Memory map of this reference design is displayed in Table 2.

- Byte length: Input read length in byte unit.

After setting all inputs, all read values will be displayed on console, as shown in Figure 2-9.

| /cygdrive/c/altera/15.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| nput start address: 0x48000000 User Input<br>nput dump length: 0x40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | - |

| 0×480000001 00 00 00 00 01 00 00 02 00 00 00 03 00 00 00<br>0×480000101 04 00 00 00 05 00 00 00 06 00 00 00 07 00 00 00<br>0×480000201 08 00 00 00 09 00 00 00 0A 00 00 08 00 00 00<br>0×480000301 0C 00 00 00 00 00 00 00 0E 00 00 0F 00 00 00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   |

| SATA host design menu [Ver = 1.4]<br>Ø] : SATA RESET<br>1] : IDENTIFY DEVICE<br>2] : WRITE DMA (EXT)<br>3] : READ DMA (EXT)<br>4] : DUMP DATA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | - |

| and the second | 2 |

#### Figure 2-9 DUMP DATA Menu

| Address                             | Memory map                |  |

|-------------------------------------|---------------------------|--|

| 0x0100000-0x0100001F                | Avalon2SATA register area |  |

| 0x4000000-0x7FFFFFF                 | DDR memory area           |  |

| - 0x4000000-0x40000FFF              | TX FIS area               |  |

| - 0x40001000-0x40001FFF             | RX FIS area               |  |

| - 0x48000000-0x4BFFFFFF             | TX DATA FIS area          |  |

| - 0x4C000000-0x4FFFFFF              | RX DATA FIS area          |  |

| Table 2 Memory map in NIOSII system |                           |  |

## 3 Revision History

| Revision | Date      | Description                                 |

|----------|-----------|---------------------------------------------|

| 1.0      | 11-Mar-16 | Initial version release                     |

| 2.0      | 5-Jul-16  | Support Arria10 and merge V-series document |

| 2.1      | 1-Aug-16  | Modify Figure 1-5 to add DDR4 information   |