SHA256 IP Core Datasheet

Core Facts |

|

|

Provided with Core |

|

|

Documentation |

User Guide, Design Guide |

|

Design File Formats |

Encrypted File |

|

Instantiation Templates |

VHDL |

|

Reference Designs & Application Notes |

Vivado Project, See Reference design manual |

|

Additional Items |

Demo on KCU105 |

|

Support |

|

|

Support Provided by Design Gateway Co., Ltd. |

|

Design Gateway Co., Ltd.

E-mail: ip-sales@design-gateway.com

URL: design-gateway.com

Features

· Support SHA 256-bit standard function.

· Support input data length up to 261-1

bytes.

(264-8 bits)

· Super high throughput rate at 65 clocks per

64-byte data (1.015625 cycles/byte).

· Hash speed up to 1.575 Gbps @ 200MHz.

· Simple user interface signals as same as FIFO interface.

Table 1 Example Implementation Statistics for SHA256IP

|

Family |

Example Device |

Fmax (MHz)

|

CLB Regs

|

CLB LUTs

|

CLB1 |

IOB |

BRAMTile |

Design Tools |

|

Kintex-UltraScale |

XCKU040FFVA1156-2E |

200 |

1004 |

1244 |

218 |

- |

0.5 |

Vivado 2022.1 |

Notes:

1) The actual logic resource depends on the percentage of unrelated logic.

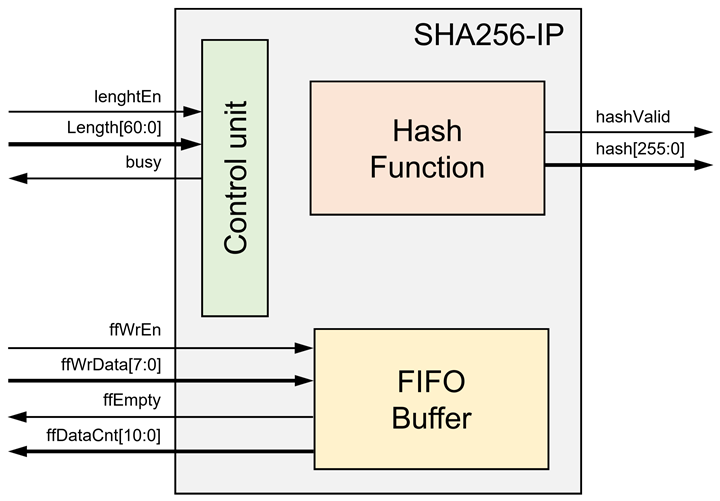

Figure 1 SHA256IP Block Diagram

General Description

SHA256IP implements the SHA-256 algorithm which is widely used for authenticating in many applications such as communication, password authentication, and also data authentication in blockchain system.

Functional Description

Table 2 shows interface signals of SHA256IP.

Table 2 I/O signals

|

Signal name |

Dir |

Description |

|

RstB |

In |

IP core system reset. Active low. |

|

Clk |

In |

IP core system clock. |

|

version[31:0] |

Out |

32-bit version number of IP |

|

HASH function control signals |

||

|

lengthEn |

In |

lengthEn is a signal to set the length of data for hash function. And then SHA256IP will start to wait data. |

|

length[60:0] |

In |

data length in byte unit. |

|

busy |

Out |

busy is active after the user set lengthEn, until SHA256IP gets all data and finishes hash process. |

|

hashValid |

Out |

hashValid signal is active 1 cycle at the end of hash process, the user can capture hash result at this cycle. |

|

hash[255:0] |

Out |

256-bit hash result. |

|

Input data interface (FIFO interface) |

||

|

ffWrEn |

In |

ffWrEn is a control signal to write ffWrData[7:0] to internal memory. |

|

ffWrData[7:0] |

In |

8-bit input data. |

|

ffEmpty |

Out |

ffEmpty

is empty status of the internal memory to wait for input data. |

|

ffDataCnt[10:0] |

Out |

ffDataCnt[10:0]

is the current valid data in byte unit. The user must pause data transfer

when remained buffer is less than 128 bytes (ffDataCnt[10:0] > x"780") |

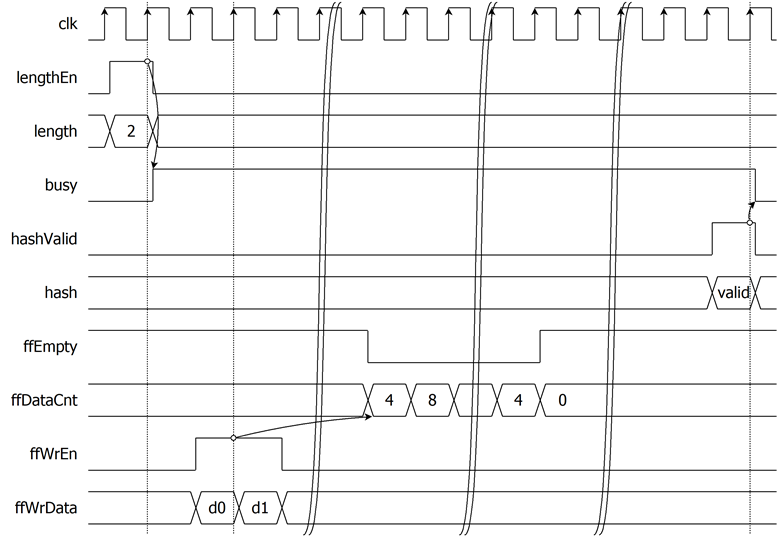

SHA256IP operation is as simple as 3 steps as below and Figure 2 shows timing diagram of SHA256IP interface signals.

· Set the length of data

The hash operation begins when the user sets lengthEn=‘1’ and specifies the data size using the length[60:0] signal in the same cycle.

The busy signal is set to be ‘1’ and remains active until SHA256IP receives all data and finishes hash function.

· Input data transfer

After setting the length to SHA256IP, SHA256IP waits for the data corresponding to the specified size. The hash function is calculated while the data is transferring.

The data interface signals are as simple as 8-bit FIFO interface signals. User logic must pause data transfer when ffDataCnt[[10:0] reaches “780” value because SHA256IP needs internal data buffer at least 128 bytes.

· Hash result valid

After SHA256IP receives all data equal to the specific length and hash function is finished, hash value is set to hash[255:0] signal while hashValid signal is set to be ‘1’. Then busy is set to be ‘0’ in next cycle, and wait for next operation cycle.

Figure 2 SHA256IP interface timing diagram

Verification Methods

The SHA256IP Core functionality was verified on real board design by using KCU105 development board.

Recommended Design Experience

The user must be familiar with HDL design methodology to integrate this IP into a system.

Ordering Information

This product is available directly from Design Gateway Co., Ltd. Please contact Design Gateway Co., Ltd. For pricing and additional information about this product, use the contact information on the front page of this datasheet.

Revision History

|

Revision |

Date (D-M-Y) |

Description |

|

1.00 |

12-Mar-25 |

Initial release |