**Datagram ProtocollP Core UDP1G-IP Introduction (Intel)**

## Super UDP Speed by hard-wired IP-Core

7-Dec-17

Design Gateway

Page 1

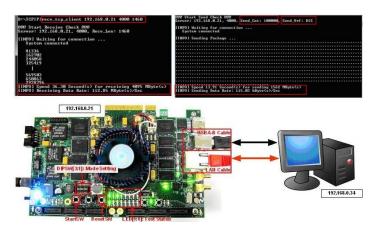

Application example

## Merit and demerit of UDP protocol

- Merit

- High-speed and low-latency by minimum overhead

- Supports 1-to-N multicast and 1-to-All broadcast

- Suitable for real-time application such as VOD system

## • Demerit

- No ACK/retransmit, so data reliability is not guaranteed

- If reliability is necessary, application layer must support it

7-Dec-17

Design Gateway

Page 3

D•G

- Problem in performance and latency

- CPU resource consumption by UDP packet building

- Check-sum calculation

- Concatenate header and transmit data

- Bandwidth is not stable due to firmware process

- The problem gets even worse with full duplex

- CPU needs to process time sharing between Tx&Rx

- Bandwidth and latency further drops

- Fatal problem for real time application

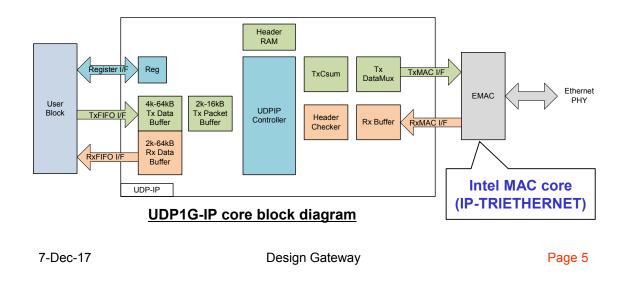

## UDP1G-IP core can provide ideal solution!

- Fully hard-wired UDP control for both Tx and Rx

- Inserts between user logic and Intel TEMAC module

- Supports Full Duplex communication

##

Arria 10

# **UDP1G-IP core Advantage 1**

#### Fully hard-wired UDP protocol control

- Possible to build CPU-less network system

- Zero load for CPU

- Support all of Tx only, Rx only, and full-duplex

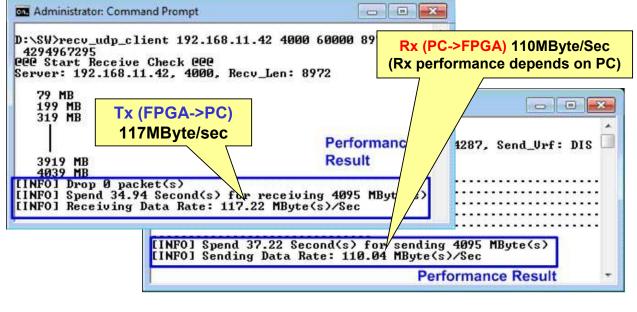

- More than 110MByte/sec real performance

- Can even keep some data reliability

- Tx: Calculate check sum and build header automatically

- Rx: Discard received Packet if check sum does not match

- Selectable data buffer size

- Selectable buffer size of memory usage vs. performance

- Compatible with Intel MAC core (IP-TRIETHERNET)

- Direct connection between UDP1G-IP and MAC

## Reference design on Intel evaluation board

- Full Quartus project for standard Intel board

- Free sof-file for evaluation before purchase

- All source code (except IP-core) in design project

7-Dec-17

**Design Gateway**

Page 7

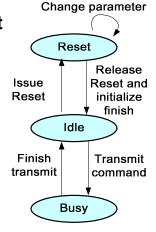

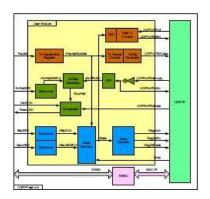

# **UDP1G-IP core Operation**

- Set parameter (IP-adr&MAC-adr, etc) during Reset

- Release Reset then initialize including ARP

- Idle state after initialization finish, wait command

- Tx operation starts by user command

- Rx operates at any time except Reset state (Accepts all Rx packet if parameter match)

- Tx and Rx operates individually (full duplex)

- If want change parameter, move to Reset state (transfer/packet length can change except Busy)

#### State Diagram

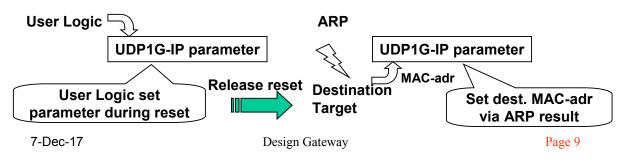

## Set parameter to UDP1G-IP

- User logic can set parameter during UDP1G-IP reset

- Set IP address, MAC address, and Port number

- Release reset after parameter setting finish

- UDP1G-IP executes ARP after reset release

- Issue ARP to destination target

- Get MAC-adr of the target via ARP result

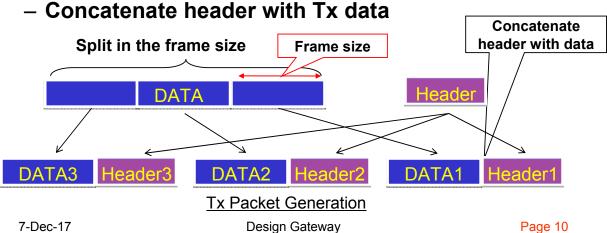

# High-Speed Tx

- Tx Packet Generation

- User Logic writes Tx data to TxFIFO

- Split Tx data in the frame size

- Calculate check sum and set to the header

# **High-Speed Rx**

- Rx packet header check

- Verify all of MAC, IP, and UDP header

- Supports multicast and broadcast

- Check sum calculation and verification

- Calculate check sum in received packet

- Verify calculated value with header value

- When mismatch, packet data is discarded

Page 11

7-Dec-17

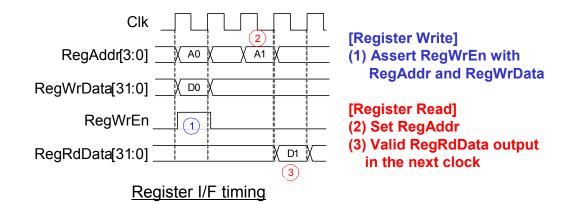

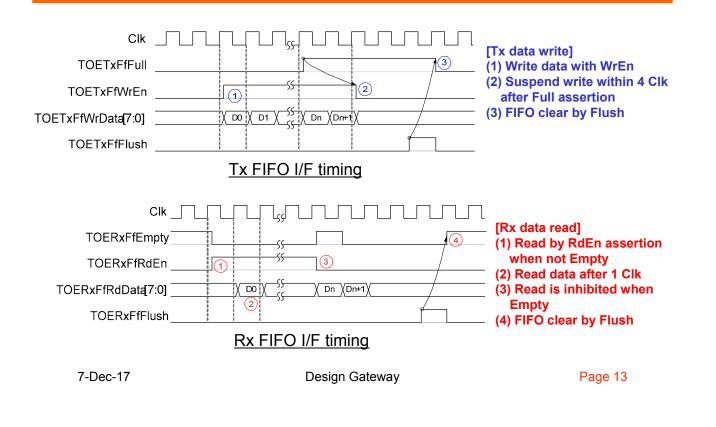

• 3 types of Register I/F, Tx FIFO I/F, and Rx FIFO I/F

**Design Gateway**

- Register I/F for initial parameter setting and Tx/Rx command

- Tx FIFO I/F and Rx FIFO I/F is standard FIFO interface

## **User Interface (Data)**

# **Buffer Capacity**

#### Parameterized 3 types of data buffer

- (1) Tx Data Buffer: 4KByte 64KByte

- (2) Tx Packet Buffer: 2KByte 16KByte

- (3) Rx Data Buffer: 2KByte 64KByte

- User can optimize resource usage and performance

| Generic Name  | Range | Description                                                   |

|---------------|-------|---------------------------------------------------------------|

| TxBufBitWidth | 12-16 | Set Tx data buffer size in address bit width                  |

|               |       | When set to 12, size is 4KByte, when 16, 64KByte for example. |

| TxPacBitWidth | 11-14 | Set Tx packet buffer size in address bit width                |

|               |       | When set to 11, size is 2KByte, when 14, 16KByte for example  |

| RxBufBitWidth | 11-16 | Set Rx data buffer size in address bit width                  |

|               |       | When set to 11, size is 2KByte, when 16, 64KByte for example. |

#### Buffer size is selectable by parameterization

Design Gateway

- SOF file for evaluation with Intel standard board

- Support both Half-Duplex and Full-Duplex operation

- Measure transfer speed performance and data reliability

**Design Gateway**

Evaluation environment for Intel board

7-Dec-17

# Reference Design Overview

- Quartus design project for real operation

- All source code (except IP-core) included in full project

- Both half-duplex and full-duplex design in IP-core package

| DGGGG & LEAR                 | 1 (* 1120414) * 1977600 C + 0 10 0 0 1 4 0                            |  |  |  |  |

|------------------------------|-----------------------------------------------------------------------|--|--|--|--|

| can't Merigatur              | ER 6                                                                  |  |  |  |  |

|                              |                                                                       |  |  |  |  |

| inter contract in the second |                                                                       |  |  |  |  |

| DOMESTIC IN DESIGNATION      | 45 B                                                                  |  |  |  |  |

| • TOESHITHE &                | C C C C C C C C C C C C C C C C C C C                                 |  |  |  |  |

|                              |                                                                       |  |  |  |  |

|                              | 49 E Component TORBATATION In                                         |  |  |  |  |

|                              | 50 FI Port (                                                          |  |  |  |  |

|                              | St Back r in and Jugior                                               |  |  |  |  |

|                              | - 11 Prers : in std insic                                             |  |  |  |  |

|                              |                                                                       |  |  |  |  |

|                              | 54 Facility 1 in and logant - "D": To Bost-Dame Frame (1600 hyper)    |  |  |  |  |

|                              | 55 Rodebal 1 10 att Logici - 'D'i Jaco dano, 'J'i Parative dano       |  |  |  |  |

|                              | 58 Verifiers - in and indian 1011 Perceive alloging verification, 11  |  |  |  |  |

|                              | 17                                                                    |  |  |  |  |

|                              | 38 Fachegadd 1 con and inpir vectors 7 downto 0 12                    |  |  |  |  |

|                              | 10 Rectoply the state will be to                                      |  |  |  |  |

|                              | 50 FachepWrData : out stil Logic martor   31 Bowato 0 17              |  |  |  |  |

|                              | 42 BackeyVallBerg 1 bit did begins                                    |  |  |  |  |

|                              | c:                                                                    |  |  |  |  |

|                              | 43 Faithed to the ped inght;                                          |  |  |  |  |

|                              | 84 RecTation a set and legits                                         |  |  |  |  |

|                              | 85 FacTulate : out and Logic vector   7 downs 0 ;;                    |  |  |  |  |

|                              | 48 ResTator + est and inglo                                           |  |  |  |  |

|                              | 47 BarToValid r cut std Logier                                        |  |  |  |  |

|                              | 68 BarToleanzy 1 In and Logics                                        |  |  |  |  |

|                              |                                                                       |  |  |  |  |

|                              | No Machelik : in sud inght:                                           |  |  |  |  |

|                              | 72 Residentify of the Artic_Topics                                    |  |  |  |  |

|                              | The Replandation of an et al. Largic_wattact ( 7 downton 0 ) r        |  |  |  |  |

|                              | 72 Facilitation is the send implicit                                  |  |  |  |  |

|                              | 78 Rectornated a in sta_ingtor                                        |  |  |  |  |

|                              | 75 Installer a part and install                                       |  |  |  |  |

|                              |                                                                       |  |  |  |  |

|                              | 71. Consilite a set stat ingini<br>78. Facturillers : out stat ingini |  |  |  |  |

|                              |                                                                       |  |  |  |  |

|                              | The Treatment of the State                                            |  |  |  |  |

| ineractiv III rise   # Desg  | AL DA Desirest THEATINGS                                              |  |  |  |  |

Quartus/Qsys project in package

Reference design block diagram

Page 15

- Quartus project is attached to UDP1G-IP package

- Full source code (VHDL) except IP core

- Can save user system development duration

- Confirm real board operation by original reference design.

- Then modify a little to approach final user product.

- Check real operation in each modification step.

7-Dec-17

Design Gateway

Page 17

# **Resource Usage**

## • UDP1G-IP core standalone resource usage – Condition = Maximum buffer setting

(TxDataBuf=RxDataBuf=64KB, TxPacketBuf=16KB)

|    |     | 5 |   |

|----|-----|---|---|

| 1  | 200 |   | 7 |

|    |     |   | 1 |

| 20 |     |   | 1 |

| Example Device     | Fmax<br>(MHz)                                    | ALMs                                                                              | Regist<br>ers                                                                                       | Block<br>Memory bit                                                                                                       | Design<br>Tools                                                                                                                                                    |

|--------------------|--------------------------------------------------|-----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EP4SGX230KF40C2    | 125                                              | 1,125                                                                             | 1,553                                                                                               | 1,181,696                                                                                                                 | Quartusll 14.0                                                                                                                                                     |

| 5CEFA7F31I7        | 125                                              | 1,048                                                                             | 1,698                                                                                               | 1,181,696                                                                                                                 | Quartusll 15.1                                                                                                                                                     |

| 5AGXFB3H4F35C5     | 125                                              | 1,047                                                                             | 1,686                                                                                               | 1,181,696                                                                                                                 | Quartusll 14.0                                                                                                                                                     |

| 10AS066N3F40E2SGE2 | 125                                              | 996                                                                               | 1,635                                                                                               | 1,181,696                                                                                                                 | Quartusll 16.0                                                                                                                                                     |

|                    | EP4SGX230KF40C2<br>5CEFA7F31I7<br>5AGXFB3H4F35C5 | Example Device (MHz)   EP4SGX230KF40C2 125   5CEFA7F31I7 125   5AGXFB3H4F35C5 125 | Example Device (MHz)   EP4SGX230KF40C2 125 1,125   5CEFA7F31I7 125 1,048   5AGXFB3H4F35C5 125 1,047 | EXample Device (MHz) ers   EP4SGX230KF40C2 125 1,125 1,553   5CEFA7F31I7 125 1,048 1,698   5AGXFB3H4F35C5 125 1,047 1,686 | EXample Device (MHz) ers Memory bit   EP4SGX230KF40C2 125 1,125 1,553 1,181,696   5CEFA7F31I7 125 1,048 1,698 1,181,696   5AGXFB3H4F35C5 125 1,047 1,686 1,181,696 |

UDP1G-IP core standalone compilation result

This result is based on maximum buffer size setting. User can save memory resource by smaller buffer size setting

## **Transfer Performance**

## Real performance in data Tx and data Rx

**Design Gateway**

7-Dec-17

User Datagram ProtocollP Core

Page 19

# **UDP1G-IP** Application

#### Video-on-Demand via Broadcast

- Stream video transmission in real time

- Requires minimum overhead and latency

- UDP1G-IP provides best solution

## Real time Online game

- Full duplex of game data download and user operation data upload

- Very low latency required for realistic game

- UDP1G-IP can cover full duplex within minimum latency

• Detailed documents available on the web site

- http://www.dgway.com/UDP-IP\_A\_E.html

- Contact

- Design Gateway Co,. Ltd.

- E-mail :

ip-sales@design-gateway.com

- FAX : +66-2-261-2290

7-Dec-17

DG DESIGN

Page 21

(§ All SHI

## **Revision History**

**Design Gateway**

| Rev.                         | Date       | Description                     |  |  |

|------------------------------|------------|---------------------------------|--|--|

| 1.0E 6-Mar-2017 English vers |            | English version initial release |  |  |

| 1.01E                        | 7-Dec-2017 | Fixed incorrect expression      |  |  |

|                              |            |                                 |  |  |

|                              |            |                                 |  |  |

|                              |            |                                 |  |  |

|                              |            |                                 |  |  |

|                              |            |                                 |  |  |

|                              |            |                                 |  |  |

|                              |            |                                 |  |  |

|                              |            |                                 |  |  |

|                              |            |                                 |  |  |

|                              |            |                                 |  |  |

<sup>&</sup>lt;text><text><text><text><text><text><text><text><list-item><list-item><section-header><section-header>