#### **APS-IP Introduction for Altera**

Ver1.1E

### Ideal for embedded storage!

24-Feb-16 Design Gateway Page 1

## **Agenda**

- PCIe SSD Overview

- SSD Trends

- Merit of PCIe SSD for embedded system

- APS-IP Introduction

- Summary

- Function

- User Interface

- Performance and Size

- Development Environment/Reference Design

- Application

### **SSD Trends**

- SATA interface is now performance bottle neck

- SSD Read/Write speed is limited to 600MB/sec SATA bandwidth

- Move to PCI Express for faster speed

- PCIe GEN3 x4lane can provide 4GB/sec transfer speed

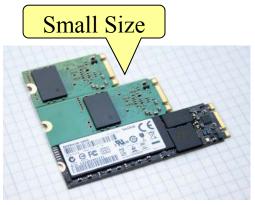

- M.2 form factor suitable for compact product application

- Width=22mm, Lenth=20/42/80/120mm, DIMM-like very small outline

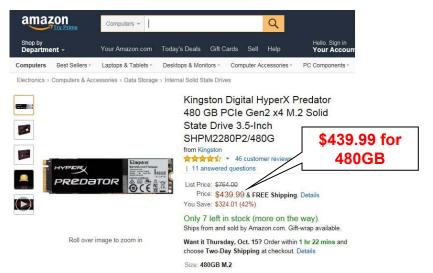

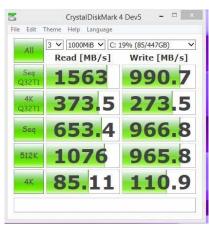

**Latest M.2 type PCIe SSD**

Design Gateway

Page 3

24-Feb-16

- · High Bandwidth: 1.5GB/s for Read, 1GB/s for Write

- Cost effective: Cost difference from SATA SSD is small

(http://www.bjorn3d.com/2015/03/480gb-hyperx-predator-m-2-pcie-ssd-shpm2280p2480g/6/)

#### Cost and Performance of M.2 PCIe SSD (Kingston 480GB)

## Merit of PCIe SSD for Embedded System 2

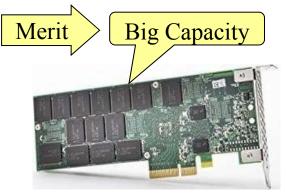

- Various form factor

- HHHL(Half-Height, Half-Length) general PCIe board

- M.2 cost saving module

- SFF-8639 of 2.5" drive compatible size

**HHHL PCIe board**

M.2 module (length=42/60/80mm)

SFF-8639 package

24-Feb-16 Design Gateway Page 5

# D-(F

#### What's APS-IP

- What's APS-IP?

- Function?

- How to use?

- User Merit?

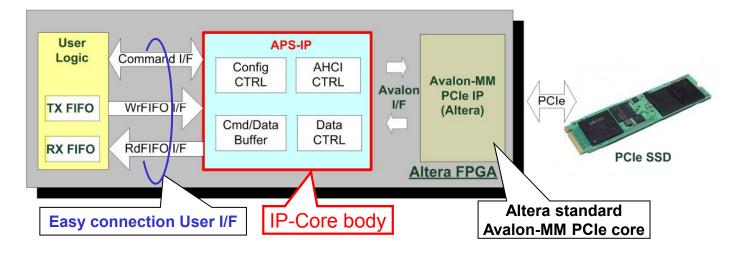

- -> Reduction of AHCI PCIe SSD IP Core

- -> PCle Root with full automatic SSD R/W function

- -> Just connect with user logic, no need CPU&F/W

- -> Can develop Storage Application in short period

#### **APS-IP Merit**

- 1. Function: Full automatic access to PCle SSD

- No CPU and firmware necessary, just wired logic is enough

- 2. Interface: Simple and easy connection

- Direct connection to Altera standard Avalon-MM PCIe core

- User I/F control is parameter with pulse, data is simple FIFO

- 3. High Performance and Compact size

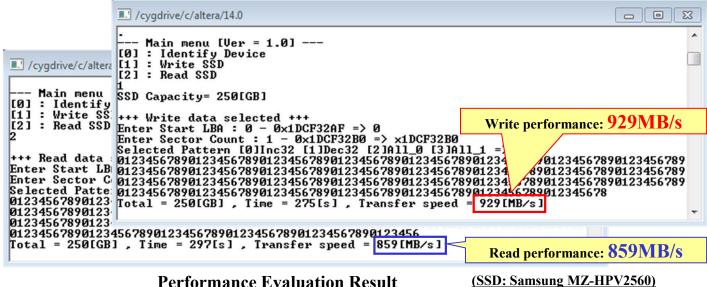

- Write speed=929MB/s, Read speed=859MB/s (measured speed in real board)

- Core size=580ALM, 880DFF

Full design project with real board operation in the package

24-Feb-16 Design Gateway Page 7

#### **APS-IP Merit 1: Function**

- Special PCIe Root port function for SSD control

- PCle Initialization: BAR Init./MSI Interrupt set/Master mode set

- SSD Status Monitor: Intr./Status automatic check

- AHCI Read/Write function

- Control AHCI register by user R/W request and execute access

- Data transfer and flow control between PCIe and FIFO

Can set next parameter for

next access after

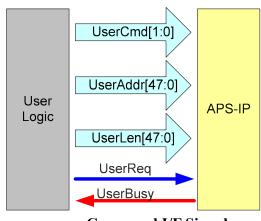

#### **APS-IP Merit2: Command I/F**

- Easy Connection User I/F

- Set Command/Address/Length

- Issue UserReq pulse

- Full Automatic control for SSD access

- User only can wait UserBusy negation

**Command I/F Signals**

User Command

Us

Issue command by UserReq

together with Cmd, Addr, and Len

Command I/F waveform

24-Feb-16 Design Gateway Page 9

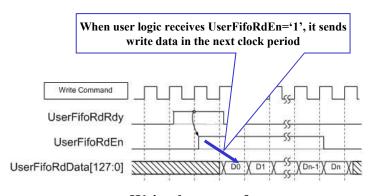

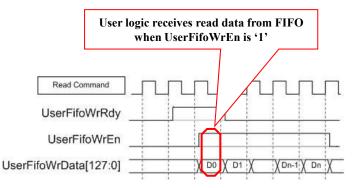

### **APS-IP Merit2: Data I/F**

- Simple 128bit FIFO for each of read and write

- User Logic sends write data by UserFifoRdEn from IP-Core

- User Logic gets read data with UserFifoWrEn from IP-Core

Write data waveform

Read data waveform

#### **APS-IP Merit3: Performance**

- Automatic PCIe SSD access by pure hard-wired logic

- Intelligent state machine for complete read/write command execution

- Minimum over head and best performance by synchronized circuit

**Performance Evaluation Result**

24-Feb-16 Design Gateway Page 11

## **APS-IP Merit3: Compact Size**

- Optimized size with minimum resource consumption

- Includes necessary control logic and temporary buffer only

- Data FIFO is not in IP-Core so user can select FIFO size

- 580ALM, 890DFF

| Family    | Example Device | Fmax<br>(MHz) | Logic utilization<br>(ALMs) | Registers <sup>1</sup> | Design<br>Tools |

|-----------|----------------|---------------|-----------------------------|------------------------|-----------------|

| ArriaV GX | 5AGXFB3H4F35C4 | 125           | 576                         | 891                    | QuartusII 14.0  |

| ArriaV ST | 5ASTFD5K3F40I3 | 125           | 578                         | 861                    | QuartusII 14.0  |

Notes:

1) Actual logic resource dependent on percentage of unrelated logic

(Note: Altera Avalon-MM PCIe core and data FIFO is not included in this result)

#### **APS-IP Core resource usage**

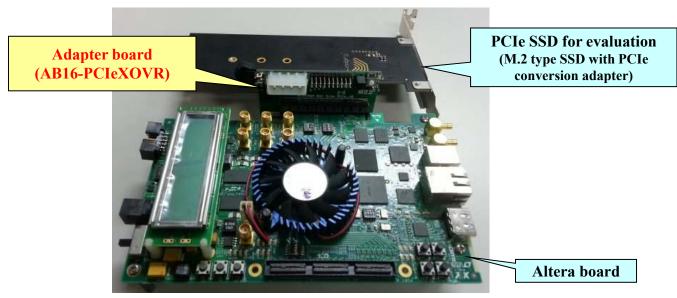

#### **APS-IP Merit4: Environment**

- Real operation check with Altera evaluation board

- Free sof-file for evaluation before IP-core purchase

IP-Core evaluation environment using ArriaV GX Starter Kit

24-Feb-16 Design Gateway Page 13

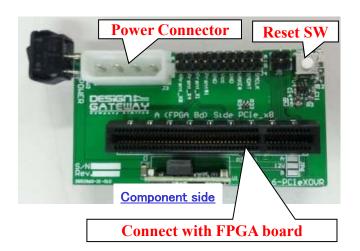

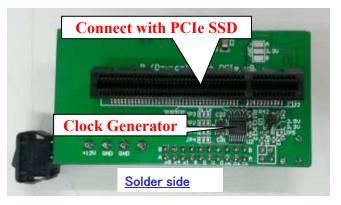

## **APS-IP Merit4: Development Tool**

- Adapter board for FPGA board evaluation (Part#: AB16-PCleXOVR)

- Connect FPGA board to PCle socket on component side

- Connect PCle SSD to PCle socket on solder side

- SSD R/W access via adapter board from APS-IP in FPGA

## **APS-IP Merit4: Reference Design**

- Vivado project is attached with APS-IP deliverables

- Full source code (VHDL) except IP core

- Can save user system development duration

- Confirm real board operation by original reference design.

- Then modify a little to approach final user product.

- Check real operation in each modification step.

Short-term development is possible without big turn back

24-Feb-16 Design Gateway Page 15

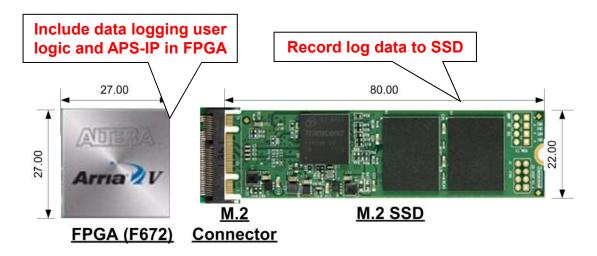

## **APS-IP Application Example**

- Space-Saving FPGA data logging system

- Latest FPGA + M.2 SSD

System space image by F672 package FPGA and M.2 SSD (unit: mm)

#### For more detail

- Detailed technical information available on the web site.

- http://www.dgway.com/APS-IP\_A\_E.html

- Contact

- Design Gateway Co,. Ltd.

- sales@design-gateway.com

- FAX: +66-2-261-2290

24-Feb-16 Design Gateway Page 17

## **Revision History**

| Rev. | Date      | Description                 |

|------|-----------|-----------------------------|

| 1.0E | 12-Jan-16 | English Version 1st release |

| 1.1E | 23-Feb-16 | Support ArriaV ST (SoC)     |

|      |           |                             |

|      |           |                             |

|      |           |                             |

|      |           |                             |

|      |           |                             |

|      |           |                             |

|      |           |                             |

|      |           |                             |

|      |           |                             |

|      |           |                             |

|      |           |                             |

|      |           |                             |

|      |           |                             |

|      |           |                             |

|      |           |                             |

|      |           |                             |

|      |           |                             |