# SATA-IP Intel V-シリーズ/10-シリーズ・ホスト・デモ手順書

Rev2.2J 2017/04/26

本ドキュメントは Altera 向け SATA-IP コアにおいて、Altera 評価キットを使ったホスト・リファレンス・デザインの実機評価デモ手順について説明したものです。デバイス・ファミリごとに対応する IP コア型番および Altera 評価キットは以下となります。 なお、評価キットの拡張インターフェイスに応じた DesignGateway 社製 SATA アダプタも必要となります。

| デバイス・ファミリ   | IP コア型番       | 検証用 Altera 評価キット  | 対応 SATA アダプタ                   |

|-------------|---------------|-------------------|--------------------------------|

| CycloneV SX | SATA-IP-C5SX  | DK-DEV-5CSXC6N    | AB11-HSMCSATA                  |

| ArriaV GX   | SATA-IP-A5GX  | DK-START-5AGXB3N  | AB11-HSMCSATA or AB12-HSMCRAID |

| ArriaV ST   | SATA-IP-A5ST  | DK-DEV-5ASTD5N    | AB09-FMCRAID                   |

| StratixV GX | SATA-IP-S5GX  | DK-DEV-5SGXEA7N   | AB11-HSMCSATA or AB12-HSMCRAID |

| Arria10 SX  | SATA-IP-A10SX | DK-SOC-10AS066S-A | AB09-FMCRAID                   |

CycloneV SX デバイスにおいてはトランシーバの制約から SATA-Ⅱ(3.0Gbps)の対応となり、その他のデバイスは SATA-Ⅲ(6.0Gbps)に対応します。

# 1 評価環境

SATA-IP ホスト・デモを実施するためには、検証用 Altera 評価キットのほかに SATA デバイスと接続するための、 DesignGateway 社製の SATA アダプタ基板が必要となります。各評価キットにおける接続状態を図 1-1~図 1-5 にそれぞれ示します。

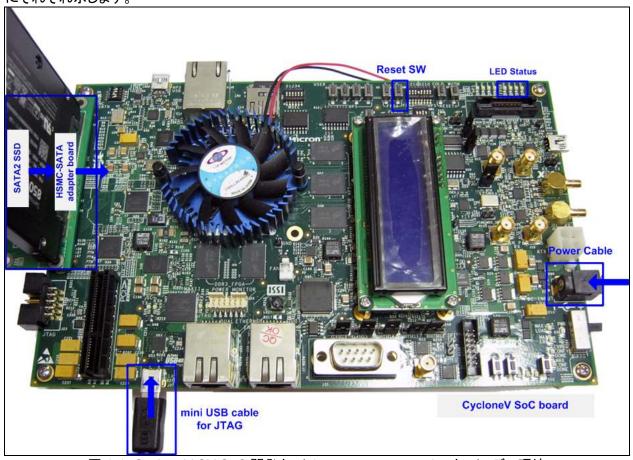

図 1-1: CycloneV SX SoC 開発キット(DK-DEV-5CSXC6N)のホスト・デモ環境

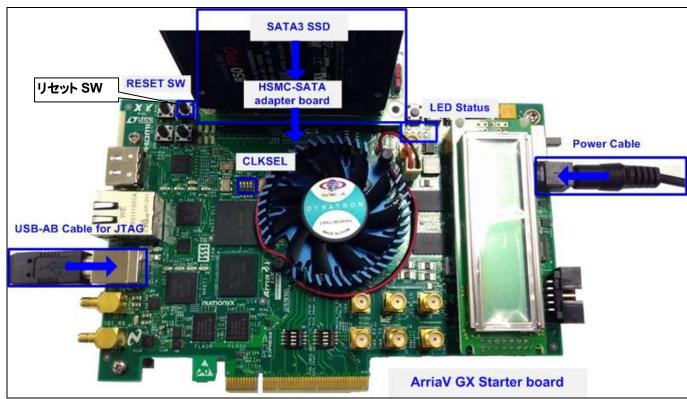

図 1-2: ArriaV GX スタータ開発キット (DK-START-5AGXB3N)のホスト・デモ環境

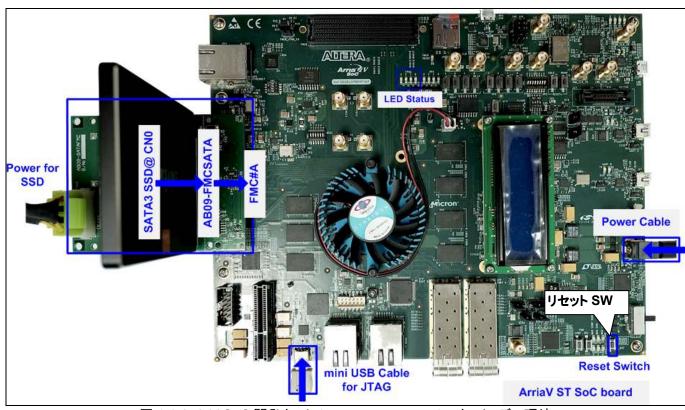

図 1-3 ArriaV SoC 開発キット (DK-DEV-5ASTD5N)のホスト・デモ環境

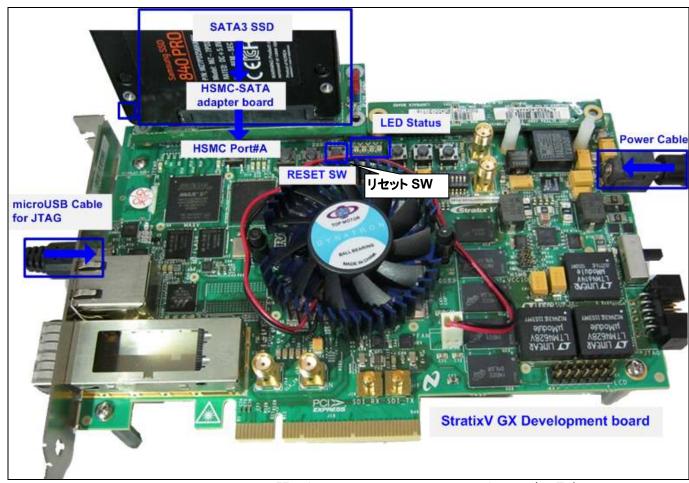

図 1-4 StratixV GX FPGA 開発キット(DK-DEV-5SGXEA7N)のホスト・デモ環境

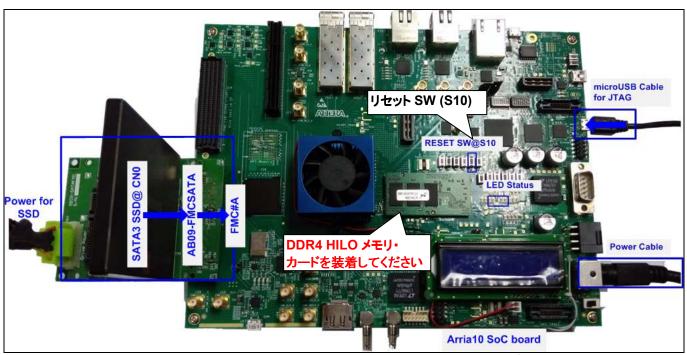

図 1-5 Arria10 SoC 開発キット(DK-SOC-10AS066S-A)のホスト・デモ環境

評価には評価デモ SOF ファイルが必要です。以下の SATA-IP Altera 紹介ページにてユーザ登録の上ダウンロードしてください。

SATA-IP Altera 紹介ページ URL: http://www.dgway.com/SATA-IP A.html

#### デモは以下の手順にて実行してください。

- FPGA 評価キット、SATA アダプタ・ボード、SATA デバイスの電源が全て OFF であることを確認します。

- SATA デバイスを HSMC/FMC の SATA アダプタ・ボードの CN0 に接続します。

- AB09-FMCRAID アダプタを使う場合 SATA デバイス用とし 4PIN の ATX 電源を接続します。

- SATA アダプタ・ボードを FPGA 評価キットの HSMC または/FMC 拡張コネクタと接続します。 注意:評価キットに複数の FMC/HSMC 拡張コネクタがある場合、Port#A 側に接続してください。

- JTAG プログラムや JTAG UART と接続するため、USB A/B, USB mini,または USB マイクロ・ケーブルで PC と FPGA 評価キット間を接続します。

- FPGA評価キットの電源を接続します。

- CycloneV SX SoC または ArriaV SoC 開発キットの場合、下図 1-6 に示す SW4 の JTAG イネーブルを設定し FPGA(および MAX デバイス)を JTAG チェーンに接続します。

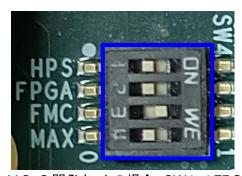

# 図 1-6 CycloneV SX SoC/ArriaV SoC 開発キットの場合、SW4 で FPGA を JTAG チェーンに接続

- CycloneV SX SoC 開発キット、ArriaV GX スタータ開発キット、または Arria10SoC 開発キットの場合以下としてプログラマブル・クロックをイネーブルとします。

- a) CycloneV SX SoC 開発キットの場合、図 1-7 のように SW2 の Bit2 を ON とします。

図 1-7 CycloneV SX SoC 開発キットの場合 SW2 の Bit2 を ON

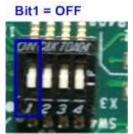

b) ArriaV GX スタータ開発キットの場合、図 1-8 のように SW4 の Bit1 を OFF とします。

図 1-8 ArriaV GX スタータ開発キットの場合 SW4 の Bit1 を OFF

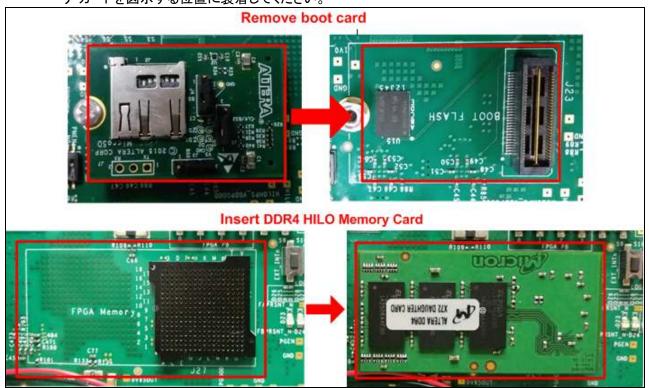

c) Arria10 SoC 開発キットの場合、図 1-9 のようにボードからブート・カードを外し、更に DDR4 HILO メモリ・カードを図示する位置に装着してください。

図 1-9 Arria10 SoC 開発キットの場合、ブート・カードを外し DDR4 カードを装着しておく

- FPGA評価キットの電源を投入します。

- CycloneV SX SoC, ArriaV GX スタータ開発キット、または StratixV GX FPGA 開発キットの場合、"Clock Control"アプリケーションを起動し、プログラマブル・クロック発生器の周波数を設定します。

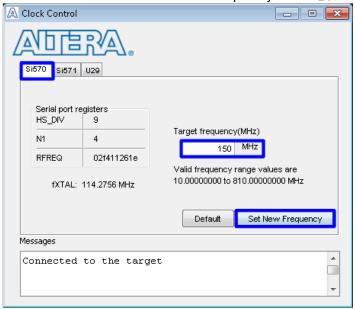

- a) CycloneV SX SoC 開発キットの場合、下図 1-10 のように最初のタブ(Si570)を選択し、Target frequency = 150 MHz にセットしてから"Set New Frequency"ボタンを押下します。

図 1-10 CycloneV SX SoC 開発キットの場合のクロック周波数設定

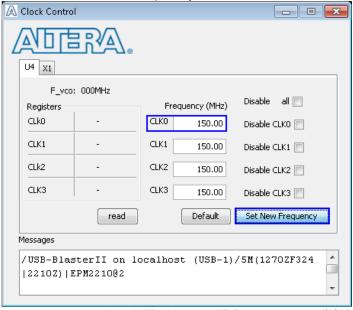

b) ArriaV GX スタータ開発キットの場合、下図 1-11 のように最初のタブ(U4)を選択し、CLK0 frequency = 150 MHz にセットしてから"Set New Frequency"ボタンを押下します。

図 1-11 ArriaV GX スタータ開発キットの場合のクロック周波数設定

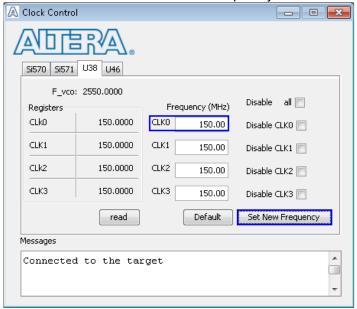

c) StratixV GX FPGA 開発キットの場合、下図 1-12 のように 3 番目のタブ(U38)を選択し、CLK0 frequency = 150 MHz にセットしてから"Set New Frequency"ボタンを押下します。

図 1-12 StratixV GX FPGA 開発キットの場合のクロック周波数設定

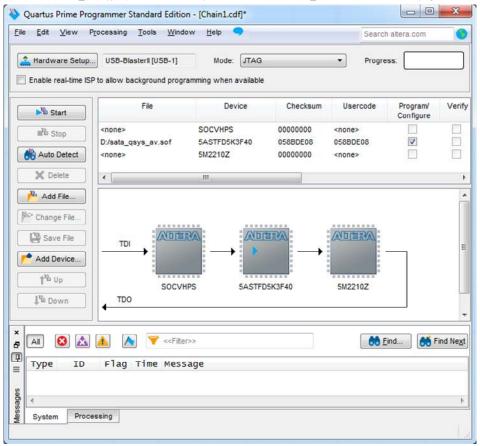

- Quartus II プログラマを起動し図 1-13 のように SOF ファイルをダウンロードします。

図 1-13 プログラマからコンフィグレーションを実行

- 評価 SATA デバイスの電源を投入します。

- a) SATA アダプタとして AB11-HSMCSATA を使う場合、下図 1-14 のように電源スイッチを ON として評価 SATA デバイスに電源を供給します。

図 1-14 AB11-HSMCSATA アダプタの SATA デバイス用電源スイッチを ON とする

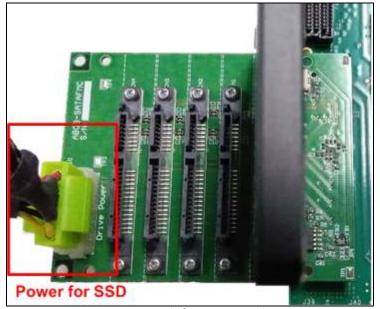

b) SATA アダプタとして AB09-FMCRAID を使う場合、図 1-15 のように SATA デバイス用の 4PIN 電源コネクタから供給する電源を ON とします。

図 1-15 AB09-FMCRAID アダプタの SATA デバイス用電源を投入

- Altera 評価キットの LED 状態をチェックし、図 1-16 のように LED0-1 がともに ON となっていることを確認します。 また、LED の定義について表 1 に示します。

図 1-16 セットアップ完了時の LED の状態

| LED  | ON          | OFF                                   | 点滅             |

|------|-------------|---------------------------------------|----------------|

| LED0 | OK          | SATA-IP が接続 SATA デバイスを認識できません。 SATA ケ | SATA-IP エラー(*) |

|      |             | ーブル接続・電源・150MHz クロック等を確認してください。       |                |

| LED1 | OK          | FPGA 内部 PLL がロックしません。                 | SATA-IP エラー(*) |

| LED2 | SATA デバイスに対 | アイドル状態                                |                |

|      | してライトを実行中   |                                       |                |

| LED3 | SATA デバイスに対 | アイドル状態                                |                |

|      | してリードを実行中   |                                       |                |

表 1 ホスト・デモにおける LED の定義

### (\*) ご注意:

- LED0/LED1 が点滅した場合は SATA-IP 内部エラーです、以下の場合 LED が点滅し内部エラーを報告します。

- (1) データ受信中、接続デバイスからのディスコネクト要求(trn\_rsrc\_dsc\_n)がアサートされた

- (2) データ送信中、接続デバイスからのディスコネクト要求(trn tdst dsc n)がアサートされた

- (3) トランザクション終了時に IP コアからエラー・コードが報告された

- いずれの場合も接続デバイスで異常を検出しデータ転送やコマンドの強制中断が発生したことを意味します。

- LED0/LED1 点滅が発生した場合、送受信 SATA 信号品質や FPGA トランシーバの送受信特性に問題があって SATA シリアル通信自体が正常に行えない状態となっています。

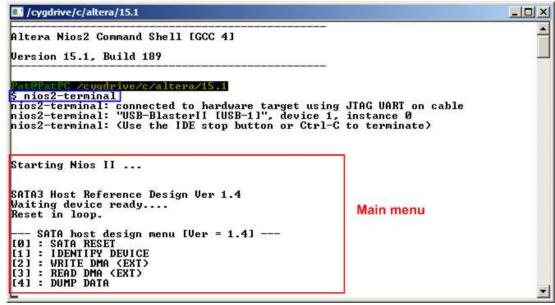

- Niosll コマンド・シェルを起動します。

- "nios2-terminal"とタイプすると図 1-17 に示すように SATA ホスト・デモのメニュー画面が表示されます。各メニューについての詳細は次章以下で説明します。

図 1-17 Niosll ターミナルの起動画面

# 2 メイン・メニュー

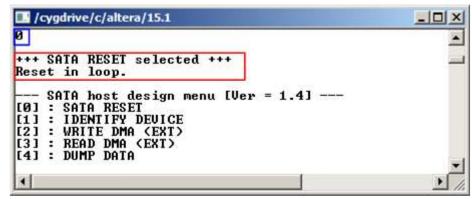

#### 2.1 SATA RESET

● '0'キー入力により SATA-IP と PHY モジュールの両方に対してハードウエア・リセットを発行します。 このメニューにより SATA のイニシャライズ処理が再実行され、図 2-1 に示すコンソール画面のように"SATA RESET selected"メッセージが表示されます。 リセット処理が完了し再度デバイスと Link Up するとメイン・メニューが再表示されます。

図 2-1 SATA RESET メニュー

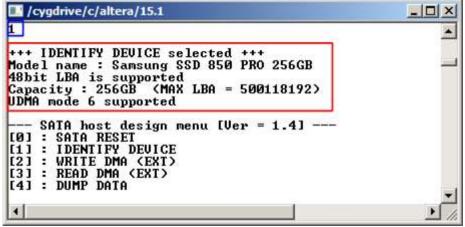

#### 2.2 IDENTIFY DEVICE

- '1'キー入力により接続 SATA デバイスに対して"IDENTIFY DEVICE"コマンドを発行します。

- 実行結果としてドライブ情報(モデル番号、48bitLBA サポートの有無、ドライブ容量等)が図 2-2 に示すように表示されます。

図 2-2 IDENTIFY DEVICE コマンドによるドライブ情報の表示画面

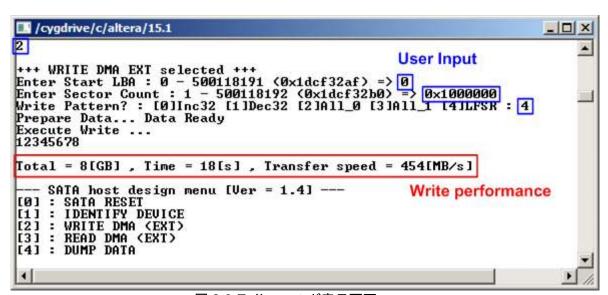

# 2.3 WRITE DMA (EXT)

- '2'キー入力により接続 SATA デバイスに対してライト・コマンドを発行します。

- このコマンドには以下の3パラメータ入力が求められます。

- 1) Start LBA: ライトを開始する LBA アドレスを入力します。 入力はデフォルトでは 10 進数ですが先頭に"0x"をつけて入力すると 16 進数で入力できます。(例:"0x123ABC"など)

- 2) Sector Count: ライトするデータ量をセクタ数(1 セクタ=512 バイト)単位で入力します。 先頭に"0x"を つけると 16 進数で入力できます。この値が 65,537 以上の(32M バイトのライト・データ・バッファの容量 を超える)場合、HDD/SSD にライトされるデータは 65,536 セクタごとに繰り返すパターンで書き込まれます。

- 3) Write pattern: HDD/SSD に書き込むデータ・パターンを指定します。本デモでは以下 5 種類のテスト・パターンの中から選択できます。

- [0] 32 ビット・インクリメンタル・パターン

- [1] 32 ビット・デクリメンタル・パターン

- [2] オール 0(0000000H)パターン

- [3] オール 1(FFFFFFFH)パターン

- [4] LFSR による擬似ランダムパターン

- パラメータが正しく入力されると以下の流れでコマンドを実行します。

- "Prepare data"が表示され CPU が指定パターンをライト・バッファに書き込みます。

- "Execute Write"が表示され CPU が WRITE DMA(EXT)コマンドを発行しライト・バッファから SATA ドライブにデータを転送します。

- 完了するとコマンド実行時間と転送データ量から計算された転送速度が表示されます。

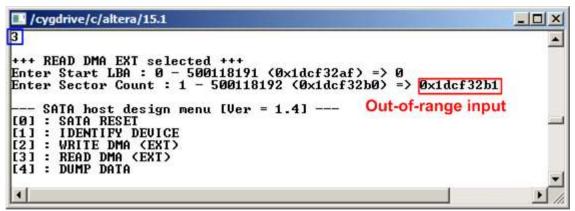

下図 2-3 にライト・コマンドの実行画面の例を表示します。 このライト・コマンドは図 2-4 のように無効なパラメータ値を入力するとコマンド実行前に中断します。

図 2-3 ライト・コマンド表示画面

```

/cygdrive/c/altera/15.1

/**HARITE DMA EXT selected +++

Enter Start LBA : 0 - 500118191 (0x1dcf32af) => 0

Enter Sector Count : 1 - 500118192 (0x1dcf32b0) => 0x1dcf32b1

--- SATA host design menu [Ver = 1.4] --- Out-of-range input

[0] : SATA RESET

[1] : IDENTIFY DEUICE

[2] : WRITE DMA (EXT)

[3] : READ DMA (EXT)

[4] : DUMP DATA

```

図 2-4 無効なパラメータ入力によるライト・コマンドの中断

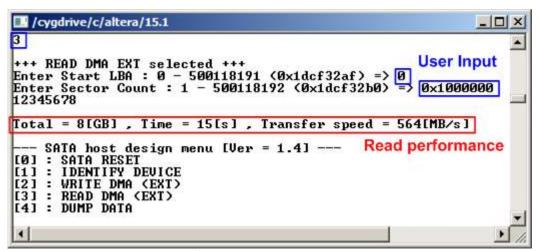

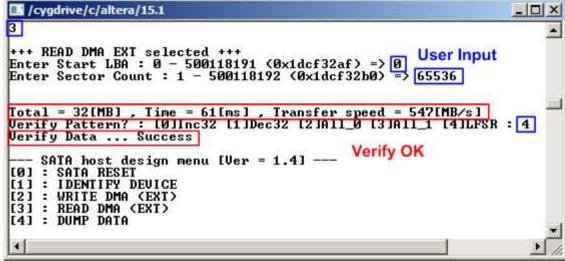

# 2.4 READ DMA (EXT)

- '3'キー入力により接続 SATA デバイスに対してリード・コマンドを発行します。

- このコマンドには以下の3パラメータ入力が求められます。

- 1) Start LBA: リードを開始する LBA アドレスを入力します。 入力はデフォルトでは 10 進数ですが先頭に"0x"をつけて入力すると 16 進数で入力できます。(例: "0x123ABC"など)

- 2) Sector Count: リードするデータ量をセクタ数(1 セクタ=512 バイト)単位で入力します。 先頭に"0x"をつけると 16 進数で入力できます。 この値が 65,537 以上の(32M バイトのリード・データ・バッファの容量を超える)場合、ベリファイ実行の選択メッセージを表示せず図 2-5 のように転送速度を表示してからメイン・メニューに戻ります。

- 3) Verify pattern: このメニューは Sector Count 数が 65,536 あるいはそれ以下の場合、図 2-6 のようにリード動作を実行した後に表示されます。指定するベリファイ・パターンは WRITE DMA (EXT)メニューにおける Write Pattern と同じ 5 種類のテスト・パターンとなります。 ベリファイを選択した場合、データ中に不一致データを見つけた時点で図 2-7 のように "Data Mismatch"と表示し、それ以降のベリファイ動作を完了します。(T の値が期待値で F の値が検出されたリード値です。)

- リード・コマンドでもライト・コマンドと同様、無効なパラメータ値を入力すると図 2-8 のようにコマンド実行前に中断します。

図 2-5 Sector Count が 65,537 以上の場合のリード・コマンド表示画面

図 2-6 Sector Count が 65,536 以下でベリファイを実行した場合の表示画面

図 2-7 ベリファイ中不一致データが見つかった場合の表示画面

図 2-8 無効なパラメータ入力によるリード・コマンドの中断

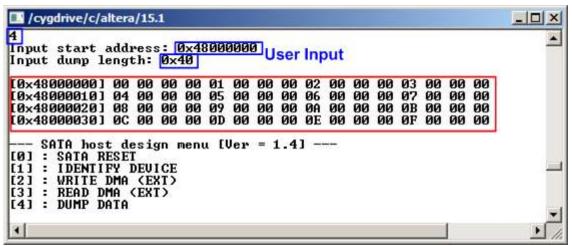

#### 2.5 DUMP DATA

- '4' キー入力により DDR3 メモリで構築したデータ・バッファやデバッグ用として Avalon2SATA モジュール内部を表示する DUMP メニューに移ります。

- このコマンドには以下の 2 パラメータ入力が求められます。(それぞれの入力はデフォルトでは 10 進数ですが先頭に"0x"をつけて入力すると 16 進数で入力できます。)

- 1) start address:表示を開始するアドレスを入力します。 本デモのアドレス・マップを表 2 に示します。

- 2) dump length:表示するデータ量をバイト単位で入力します。

- パラメータ入力後、下図 2-9 のように指定した範囲のメモリ内容が 16 進数で表示されます。

図 2-9 ダンプ・コマンド表示画面

| アドレス範囲                  | メモリ・マップ                 |

|-------------------------|-------------------------|

| 0x01000000-0x0100001F   | Avalon2SATA モジュール内部レジスタ |

| 0x40000000-0x7FFFFFF    | DDR メモリ空間、さらにその内訳は以下の通り |

| - 0x40000000-0x40000FFF | - TX FIS エリア            |

| - 0x40001000-0x40001FFF | - RX FIS エリア            |

| - 0x48000000-0x4BFFFFF  | - TX DATA FIS エリア       |

| - 0x4C000000-0x4FFFFFF  | - RX DATA FIS エリア       |

表 2 メモリ・マップ

# 3 改版履歴

| リビジョン | 日付         | 更新内容                                        |

|-------|------------|---------------------------------------------|

| 1.0   | 11-Mar-16  | Initial version release (英語版)               |

| 2.0   | 5-Jul-16   | Support Arria10 and merge V-series document |

| 2.0J  | 2016/07/08 | 英語版 2.0 を翻訳した日本語版作成                         |

| 2.1J  | 2017/02/15 | Arria10SoC ボードの場合 DDR4 HILO メモリカード装着の説明追加   |

| 2.2J  | 2017/04/26 | 表 1 にて LED0/1 点滅の説明を追加                      |