### **RAID prototype system introduction** Ver1.3E

### SATA-IP RAID prototype system for Xilinx FPGA

3 September 2018

Design Gateway

Page 1

## System Outline

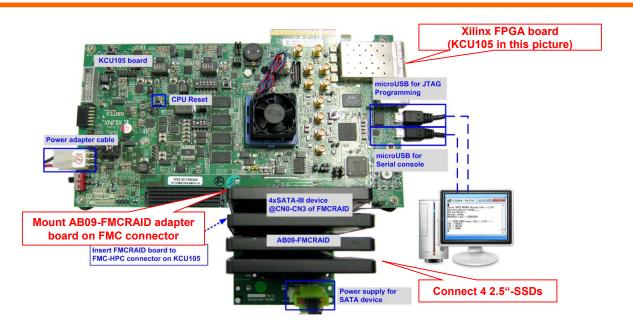

- RAID prototype for the latest Xilinx FPGA

- Use RAID adapter board (AB09-FMCRAID)

- Operate 4-channel RAID0 (parallel access)

- Standard and High Performance version

- Show read/write result to PC via RS232C

- Execute test pattern read/write

- Display measured transfer performance

### RAID prototype system using Xilinx FPGA board

3 September 2018

Design Gateway

Page 3

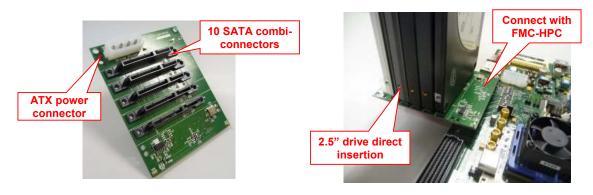

# **RAID Adapter Board**

- Can support up to 10 SATA channels (each 5 SATA ports on both component and solder side)

- Connect with FMC-HPC connector on Xilinx FPGA board

- 2.5"-SSD/HDD drive direct insertion

- Drive power supply via standard ATX power connector

- Part Number: AB09-FMCRAID

- Available on Mouser website <u>https://www.mouser.com/</u>

3 September 2018

Design Gateway

Page 4

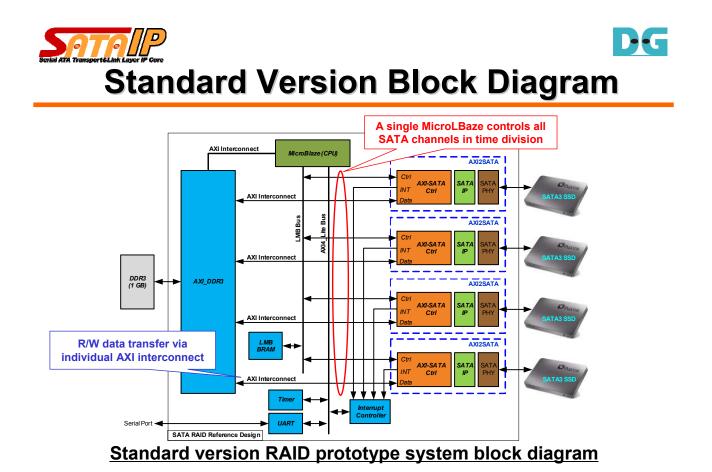

## Two types RAID design

• Standard Version (MicroBlaze control)

- Use MicroBlaze for SATA-IP controller

- All channel control by time division in CPU F/W

- Requires SATA-IP only (no need HCTL-IP)

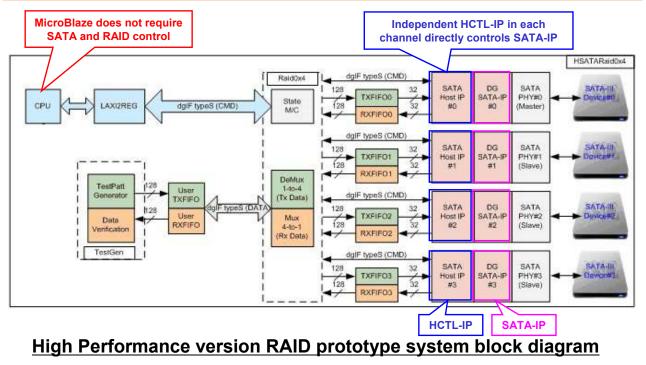

- High Performance Version (HCTL-IP control)

- Use HCTL-IP core for SATA-IP controller

- Minimum latency, Maximum performance

- Requires Both SATA-IP and HCTL-IP core

3 September 2018

Design Gateway

### **High Performance Version Block Diagram**

**Design Gateway**

3 September 2018

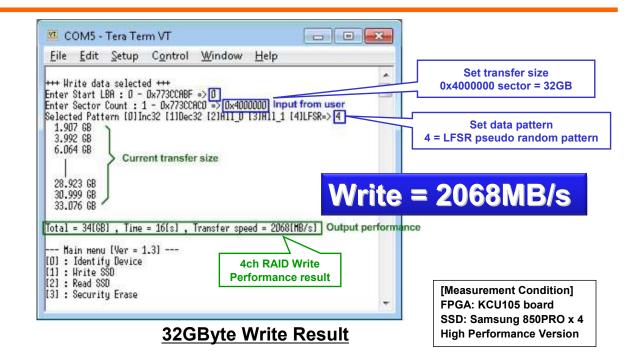

### Write Result (High Performance Version)

Page 7

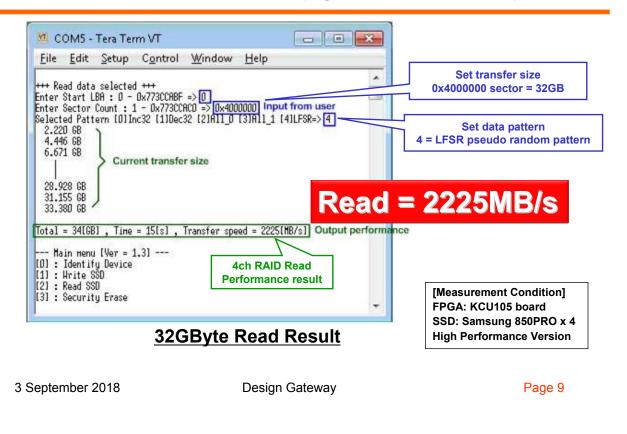

Read Result (High Performance Version)

## **RAID** Performance

- Write speed efficiency=99%

- Single=520MB/s, 4ch-RAID=2068MB/s

- Speed efficiency = 2068/(4 x 520) = 99%

- Read speed efficiency=97.29%

- Single=560MB/s, 4ch-RAID=2225MB/s

- Speed efficiency = 2225/(4 x 560) = 99%

- Vivado project is attached with SATA-IP and/or HCTL-IP product

- Full source code except IP core

- VHDL for hardware and C for MicroBlaze firmware

### Can save user system development duration

- Confirm real board operation by original reference design

- Then modify a little to approach final user product

- Check real operation in each modification step

3 September 2018

Design Gateway

Page 11

# Conclusion

- Can build RAID prototype with FPGA & RAID adapter

- Quick check of RAID system without new board building

- RAID performance is almost 100% of single drive total

- Multiply performance by drive count

- Prototype design is available for SATA-IP users

- Reduce RAID system development period based on this design

### For more detail

- Detailed technical information available on the web site.

- <u>https://dgway.com/SATA-IP\_X\_E.html</u>

- Contact

- Design Gateway Co,. Ltd.

- sales@design-gateway.com

- FAX: +66-2-261-2290

3 September 2018

Design Gateway

Page 13

## **Revision History**

| Rev. | Date      | Description                                                             |

|------|-----------|-------------------------------------------------------------------------|

| 1.0  | 04-Jun-09 | RAID prototype system introduction 1st release                          |

| 1.1E | 21-Feb-13 | Updated toKC705 based RAID system                                       |

| 1.3E | 03-Sep-18 | Added latest family support, added high performance version description |

|      |           |                                                                         |

|      |           |                                                                         |

|      |           |                                                                         |

|      |           |                                                                         |