# SATA-IP Related Products Selection Guide

#### **Description of SATA-IP Related Products**

2019/1/6 Design Gateway Page 1

## **SATA-IP Core Related Products List**

| Product Name                              | Description                                                                                                                                                           | Application                          |

|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| HCTL-IP core<br>(Host Controller IP core) | It substitutes whole control for SATA-IP with pure hard-<br>wired logic, and can reduce CPU as well as can provide<br>the best performance.                           | For high performance                 |

| AHCI-IP core                              | AHCI adapter function that is necessary to access from LinuxOS via AHCI device driver.                                                                                | For SOC device                       |

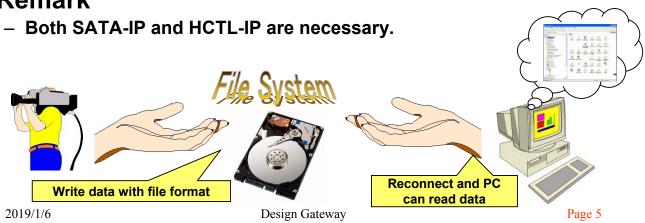

| FAT32-IP core<br>exFAT-IP core            | ✓ Support FAT32/exFAT file system.  ✓ FPGA can store data to drive and PC can read as file.  ✓ Pure hard-wired logic, no CPU necessary.  ✓ Needs HCTL-IP and SATA-IP. | FPGA – PC data<br>exchange (w/o CPU) |

- All solution requires SATA-IP core.

- Demo bit/sof file available for real board operation before purchase.

### **Summary of SATA-IP core related production**

# **Host Controller IP (HCTL-IP)**

#### Feature

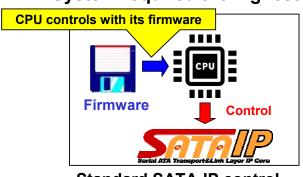

- Standard design use CPU to control SATA-IP.

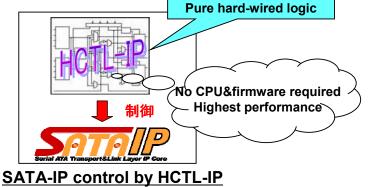

- HCTL-IP is substitution of SATA-IP controller by pure logic core.

- Minimum latency by state machine provides the best performance.

### Application

- System without CPU or remove CPU resource for SATA control.

- System required the highest performance.

Standard SATA-IP control

Design Gateway Page 3

2019/1/6

### **AHCI-IP**

#### Feature

- Converts SATA-IP upper layer interface to AHCI standard.

- SATA access is possible from embedded Linux via AHCI driver and AHCI-IP.

### Application

- Intel SOC family (with Angstrom) or Xilinx Zynq family (with PetaLinux)

- System requires SATA drive access under file-system (such as EXT3).

# File System IP (FAT32-IP/exFAT-IP)

#### Feature

- Implements file system by hard-wired logic, no CPU necessary.

- Supports 3 commands of Format, FileWrite, and FileRead (for check).

### Application

- Record data to SATA drive, reconnect to PC, then PC can read data.

# Comparison of FAT32-IP and exFAT-IP

| Item                 | FAT32-IP                | exFAT-IP            |

|----------------------|-------------------------|---------------------|

| Drive Capacity       | 64MB - 2TB              | 8GB - 64PetaB       |

| File Size            | 32MB - 2GB              | 32MB - 512GB        |

| Directory count      | No (Root directry only) | 16 directory        |

| Resource (Intel) *1  | 700ALM+42Kbit(Ram)      | 1440ALM+98Kbit(Ram) |

| Resource (Xilinx) *2 | 240CLB+1.5BRAMTile      | 400CLB+3BRAMTile    |

| Name Hash            | Not supported           | Supported           |

| Check Sum            | Not supported           | Supported           |

### Comparison of FAT32-IP and exFAT-IP

- \*1 Device family = Arria10SX

- \*2 Device family = Kintex-Ultrascale

# Detail information of each products

#### HCTL-IP core datasheet

- Intel: http://www.dgway.com/products/IP/SATA-IP/Altera/dg\_sata\_host\_ip\_datasheet\_alt\_en.pdf

- Xilinx: http://www.dgway.com/products/IP/SATA-IP/dg\_sata\_host\_ip\_data\_sheet\_en.pdf

#### AHCI-IP core datasheet

- Intel: http://www.dgway.com/products/IP/SATA-IP/Altera/dg\_sata\_ahci\_ip\_datasheet\_altera\_en.pdf

- Xilinx: http://www.dgway.com/products/IP/SATA-IP/dg\_sata\_achi\_ip\_data\_sheet\_en.pdf

#### FAT32-IP core datasheet

- Intel: http://www.dgway.com/products/IP/SATA-IP/Altera/dg\_fat32ip\_sata\_data\_sheet\_intel\_en.pdf

- Xilinx: http://www.dgway.com/products/IP/SATA-IP/dg\_fat32ip\_sata\_data\_sheet\_en.pdf

#### exFAT-IP core datasheet

- Intel: https://dgway.com/products/IP/SATA-IP/Altera/dg\_exfatip\_sata\_data\_sheet\_intel\_en.pdf

- Xilinx: <a href="https://dgway.com/products/IP/SATA-IP/dg\_exfatip\_sata\_data\_sheet\_en.pdf">https://dgway.com/products/IP/SATA-IP/dg\_exfatip\_sata\_data\_sheet\_en.pdf</a>

2019/1/6 Design Gateway Page 7

# **Revision History**

| Rev. | Date        | Description                             |

|------|-------------|-----------------------------------------|

| 1.0E | Feb-5-2018  | English Version first release           |

| 1.1E | Dec-21-2018 | exFAT-IP core release                   |

| 1.2E | Jan-06-2019 | Fixed FAT32-IP and exFAT-IP description |

|      |             |                                         |

|      |             |                                         |

|      |             |                                         |

|      |             |                                         |

|      |             |                                         |

|      |             |                                         |

|      |             |                                         |

|      |             |                                         |

|      |             |                                         |

|      |             |                                         |

|      |             |                                         |