# TOE100G-IP on Alveo card reference design

Rev1.0 21-Sep-22

| 1 | Introdu  | ıction                                    | 2  |

|---|----------|-------------------------------------------|----|

| 2 |          | 00DMATest (Hardware)                      |    |

|   | 2.1 10   | OG Ethernet Subsystem (100G BASE-SR)      | 5  |

|   | 2.2 TO   | E100G-IP                                  | 5  |

|   | 2.1 Ax   | iDMACtrl512                               | 6  |

|   | 2.1.1    | MtMainCtrl                                | 8  |

|   | 2.1.2    | AxiMtPRd                                  | 11 |

|   | 2.1.3    | AxiMtPWr                                  | 14 |

|   | 2.2 LA   | xi2Reg                                    | 20 |

|   | 2.2.1    | SAXIReg                                   | 21 |

|   | 2.2.2    | UserReg                                   | 23 |

| 3 | The ho   | ost software                              | 27 |

|   | 3.1 Fra  | amework                                   | 28 |

|   | 3.1.1    | Device interface                          | 28 |

|   | 3.1.2    | Shell                                     | 31 |

|   | 3.2 Ap   | plication                                 | 37 |

|   | 3.2.1    | Display parameters                        | 39 |

|   | 3.2.2    | Reset IP                                  | 39 |

|   | 3.2.3    | Send data test                            | 40 |

|   | 3.2.4    | Receive data test                         | 41 |

|   | 3.2.5    | Full duplex test                          | 43 |

|   | 3.2.6    | Function list in application              | 45 |

| 4 |          | oftware on the target                     |    |

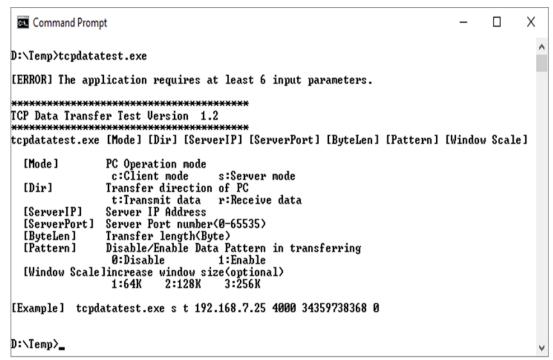

|   | 4.1 "tc  | odatatest" for half duplex test           | 51 |

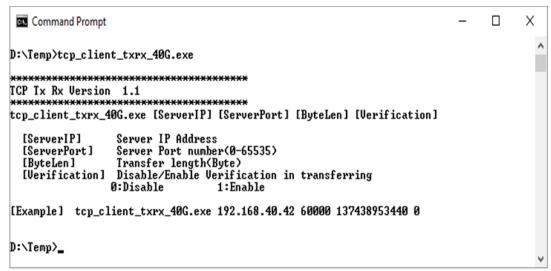

|   | 4.2 "tc  | o_client_txrx(_40G)" for full duplex test | 53 |

| 5 | Revision | on History                                | 55 |

### 1 Introduction

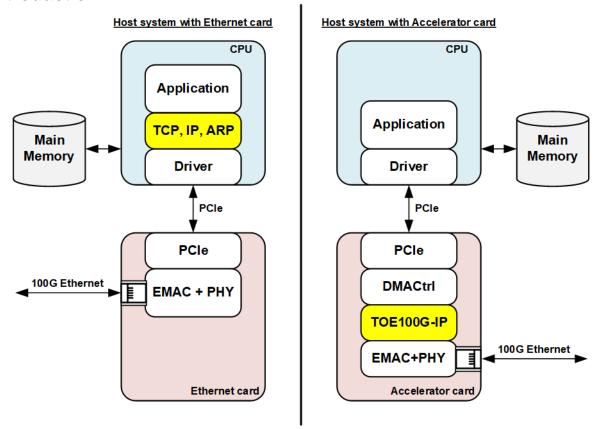

Figure 1-1 Ethernet card and Accelerator card comparison

The left side of Figure 1-1 shows the general solution when 100G Ethernet is required in the host PC. 100G Ethernet card is plugged-in to PCIe slot and then the user designs the test application on the software platform that has the library to handle TCP, IP, and ARP protocol. The device driver is provided by the 100G Ethernet card vendor to operate with the OS. Generally, the performance result on the test application when transferring the data via 100G Ethernet is limited by CPU task and the host system resource, so the maximum throughput of 100G Ethernet is not achieved.

The right side of Figure 1-1 is the Accelerator system that uses the Alveo Accelerator card to be the network interface card instead. TOE100G-IP by Design Gateway is integrated to be offload engine for TCP/IP protocol. TOE100G-IP offloads CPU to handle TCP, IP, and ARP protocol, so the TCP payload data is DMA transferred to Main memory, instead of Ethernet frame that is the output from EMAC. Also, the platform to transfer the data with the Main memory by using DMA engine via PCIe interface is specially developed by Xilinx. Therefore, the performance result when using the Accelerator card with TOE100G-IP is much better than using Ethernet card.

The TOE100G-IP on Alveo card reference design shows the complete solution on the hardware and the software to transfer TCP payload data on one TCP session with high-speed performance. The software application on the host system is developed by C++ languages, so it is easy for the user to integrate and modify the software to match with the system requirement.

Please see more details how to prepare the host system for running the Alveo accelerator card from the following site.

https://www.xilinx.com/products/boards-and-kits/alveo.html

Design Gateway also provides the development host system for Alveo card – Turnkey Accelerator System. Please check more details from our website.

https://dgway.com/AcceleratorCards.html

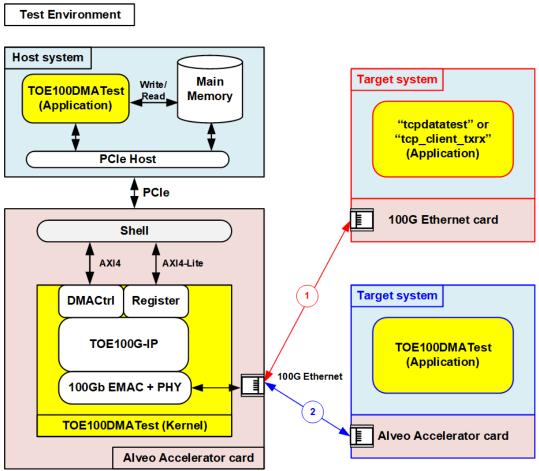

Figure 1-2 Test environment

The architecture of the TOE100G-IP demo on Alveo card can be separated into two systems - the host system which runs Ubuntu OS (Linux) and the hardware system which contains the TOE100DMA (FPGA logic). Two systems are connected through PCIe. The low layer on both the host system and the hardware system are handled and managed by Xilinx Runtime Library (XRT) and Vitis target platform. To transfer the TCP/IP payload data at 100Gb speed on the host system, the data is generated by the application with the memory allocation for transferring the data. The memory uses multiple buffering to maximize the TCP/IP transmission performance.

To run the demo, the target system can be either Test PC with Ethernet card or TOE100G-IP on another system. To use Test PC with Ethernet card, Design Gateway provides the test applications – "tcpdatatest" and "tcp\_client\_txrx" for the half-duplex transfer (send or receive data) and the full-duplex transfer (send and receive data at the same time by using one TCP session). The test applications are provided on both Windows 10 OS and Ubuntu 20.04 OS. However, using the test applications and the 100G Ethernet card show limited transfer performance. To achieve the maximum performance on 100G Ethernet, the target system should be TOE100G-IP on another system.

In the document, topic 2 shows the details of the hardware design on Alveo card. Topic 3 describes the software implementing on the Accelerator system. The last topic is the details of test application on the target system for half-duplex test and full-duplex test.

• : Tx Transfer

## 2 TOE100DMATest (Hardware)

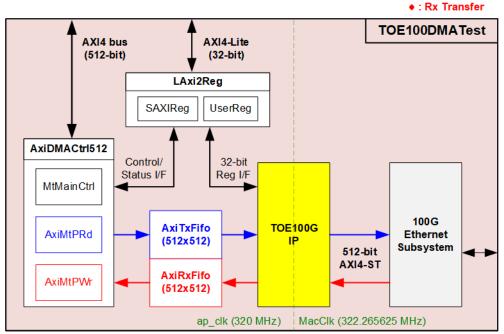

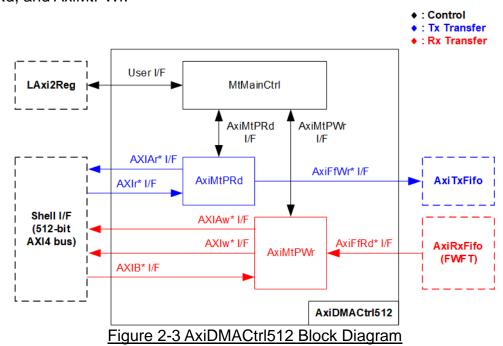

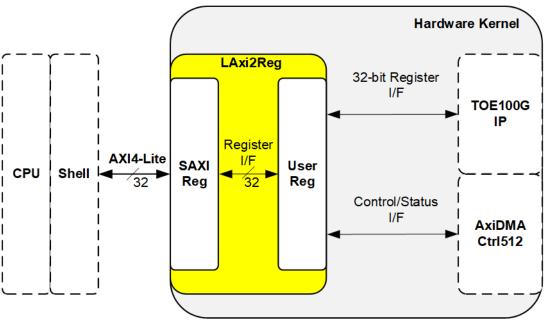

Figure 2-1 TOE100DMATest block diagram

The platform provides two interface types for the hardware kernel – AXI4 for transferring data with the Main memory and AXI4-Lite for register access which is generally applied to be control/status signals of the hardware kernel. AxiDMACtrl512 is the DMA engine for transferring data in two directions. The first one is to read the data from the Main memory and then forward to TOE100G-IP via FIFO (AxiTxFifo). After that, the TCP/IP packet is transmitted to the target system. The TCP payload data on the host memory is prepared by the test application. The second one is to receive the data from TOE100G-IP via FIFO (AxiRxFifo) and then write it to the Main memory. The test application on the host system reads the data from the Main memory with or without data verification.

AXI4-Lite bus, the platform interface, connects to LAxi2Reg module which is the adapter to convert AXI4-Lite bus to be Register interface for Control/Status signals. In TOE100DMATest kernel, it maps the register interface of AxiDMACtrl512 and TOE100G-IP to LAxi2Reg, so the test application can set the test parameters and monitor the test progress of the hardware.

TOE100G-IP connects with 100G Ethernet Subsystem via 512-bit AXI4-ST bus for connecting with the 100G Ethernet hardware connection. The Ethernet Subsystem uses MacClk domain which is equal to 322.266 MHz while the AXI interface of the platform uses ap\_clk that is configured by the platform. In this demo, ap\_clk is configured to be equal to 320 MHz for high-performance operation. CDC (Clock-crossing domain) is implemented inside TOE100G-IP. According to TOE100G-IP datasheet, clock frequency of user interface (ap\_clk) must be more than or equal to 220 MHz. More details of each hardware module inside the TOE100DMATest are described as follows.

## 2.1 100G Ethernet Subsystem (100G BASE-SR)

This module implements EMAC and PCS/PMA logic of 100G Ethernet. The physical interface on FPGA board can be applied by QSFP28 or 4xSFP28 for 100Gb BASE-SR standard. The user interface for connecting with EMAC is 512-bit AXI4-stream interface running at 322.265625 MHz. This IP core is generated by using Xilinx IP wizard. More details of the core are described in the following link.

PG203: UltraScale+ Devices Integrated 100G Ethernet Subsystem Product Guide <a href="https://www.xilinx.com/products/intellectual-property/cmac\_usplus.html">https://www.xilinx.com/products/intellectual-property/cmac\_usplus.html</a>

<u>Note</u>: In this demo, 100G Ethernet Subsystem enables RS-FEC feature, so please confirm the network equipment of the test environment for running this demo that it can support RS-FEC.

### 2.2 TOE100G-IP

TOE100G-IP implements TCP/IP stack to be the offload engine for transferring TCP/IP packet with the network device. User interface has two signal groups, i.e., control signals and data signals. Register interface is applied to set control registers and monitor status signals while Data signals are accessed by using FIFO interface. The interface with 100G EMAC is 512-bit AXI4-ST interface. More details are described in datasheet.

https://dgway.com/products/IP/TOE100G-IP/dg toe100gip data sheet xilinx.pdf

#### 2.1 AxiDMACtrl512

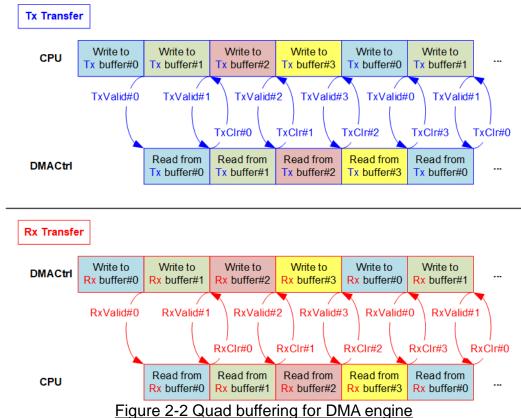

The TOE100G-IP supports full-duplex transfer test, so it is possible that data on AXI4 bus is transferred in both directions at the same time for sending and receiving data with TOE100G-IP. The test application on the host system must allocate two buffers (Tx buffer and Rx buffer) for each transfer direction. To achieve the high performance, each buffer should be split to many areas to allow the hardware and the software to operate parallelly. This reference design, each buffer consists of four areas – quad buffering (Tx Buffer#0-#3 and Rx Buffer#0-#3), as shown in Figure 2-2.

<u>Note</u>: Typically, using double buffer should be enough for CPU and DMACtrl transferring the data with the Main memory at different area as parallel processing. However, four areas are applied to add more safe time gap when CPU or DMACtrl pauses data transmission for long time.

The order to use each buffer area for both Tx and Rx Buffer is fixed to be #0 -> #1 -> #2 -> #3 -> #0.

For Tx transfer, the Main memory is written by the test application on the host system and read by the DMA engine (DMACtrl). The sequence of the operation is described as follows.

- 1) The CPU prepares the test data (dummy or incremental pattern) in the first area of the Main memory (Tx buffer#0). After filling the last data, the Valid status of this memory area (TxValid#0) is asserted.

- 2) If there is remaining data for transferring and the next memory area is free, the CPU starts writing the test data to the next area (Tx buffer#1). At the same time, DMACtrl detects the new memory area is valid and then it starts reading until the last data is read.

- 3) After finishing reading the last data, Clear status (TxClr#0) is asserted by DMACtrl to free the current memory area. If the next memory area is valid (TxValid#1 is asserted), DMACtrl starts the new operation. Repat step 1) 3) until total data is transferred.

On the other hand, the Main memory is written by DMACtrl and read by the test application for Rx transfer. The sequence of the operation is described as follows.

- 1) The DMACtrl prepares the test data in the first area of the Main memory (Rx buffer#0). After filling the last data, the Valid status of this memory area (RxValid#0) is asserted.

- 2) If there is remaining data for transferring and the next memory area is free, the DMACtrl starts writing the test data to the next area (Rx buffer#1). At the same time, CPU detects the new memory area is valid and then it starts reading until the last data is read.

- 3) After finishing reading the last data, Clear status (RxClr#0) is asserted by CPU to free the current memory area. If the next memory area is valid (RxValid#1 is asserted), CPU starts the new operation. Repeat step 1) 3) until total data is transferred.

As Tx transfer and Rx transfer are operated individually, the AxiDMACtrl512 is designed by using three submodules for controlling Tx and Rx transfer separately, i.e., MtMainCtrl, AxiMtPRd, and AxiMtPWr.

MtMainCtrl has the registers to store the test parameters, set by CPU. After decoding the test parameters, MtMainCtrl generates the request with the parameters for AxiMtPRd and AxiMtPWr to start Tx transfer and Rx transfer, respectively. AxiMtPRd generates the memory read request to the host system via AXI4 I/F to read the data from the Main memory (TxBuffer#0-#3) and transfer to AxiTxFifo. On the other hand, AxiMtPWr generates the memory write request to write data from AxiRxFifo to the Main memory (RxBuffer#0-#3) via AXI4 I/F. More details of each submodule are described as follows

### 2.1.1 MtMainCtrl

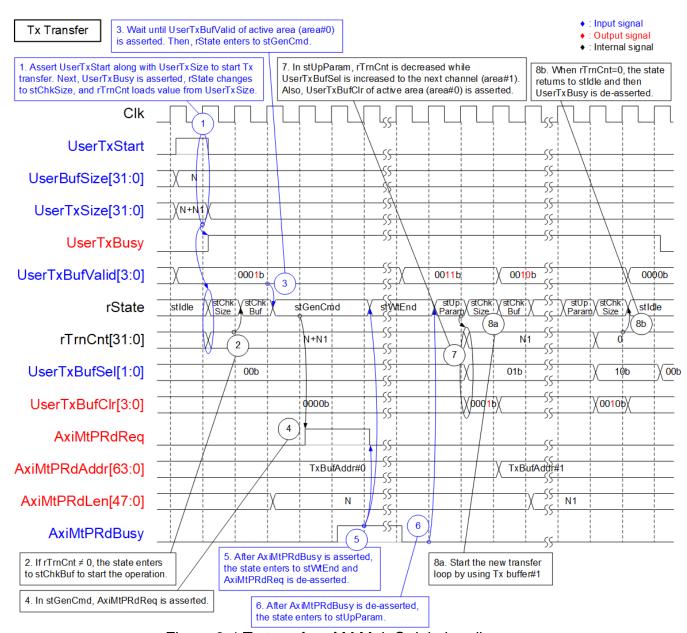

MtMainCtrl is designed to generate a command request to AxiMtPWr and AxiMtPRd for transfer the data of each buffer area. Therefore, when the total transfer size that is requested by the user is more than the buffer size area, multiple command requests are created by MtMainCtrl to AxiMtPWr/AxiMtPRd. It needs to have two individual submodules for generating command request to AxiMtPWr and AxiMtPRd. The operation to generate request to AxiMtPWr and AxiMtPRd are similar, so the same submodule, called AxiMtPCmd, is applied. This document shows the operation of AxiMtPCmd to control AxiMtPRd in Tx transfer and AxiMtPWr in Rx transfer by using timing diagram (Figure 2-4 and Figure 2-5).

The details of Figure 2-4 are described as follows.

- 1) UserTxStart is asserted by CPU to start reading the data from the Main memory. The first area to read is area#0 (TxBuffer#0). Thus, UserTxBufSel which shows the active buffer area is reset to 00b. The user input parameters UserBufSize (buffer size of each area) and UserTxSize (total transfer size of this request) are loaded to the internal logic. UserTxBusy is asserted to '1' to show that the Tx request is accepted and the operation begins. The state enters to stChkSize.

- <u>Note</u>: In Figure 2-4, total size value is equal to N + N1 to show that the transfer size of the last loop (N1) can be any value that is less than or equal to N (buffer size).

- 2) In stChkSize, the remaining transfer size (rTrnCnt) is read. If the read value is not equal to 0, the state continues to stChkBuf. Otherwise, the state returns to stIdle (step 9).

- 3) In stChkBuf, the buffer status (UserTxBufValid) of the active area is read. Each bit of UserTxBufValid is mapped to show the status of each area. When the active area is area#0, bit[0] is read. If UserTxBufValid is asserted to '1', the state enters to stGenCmd.

- 4) In stGenCmd, the parameters of AxiMtPRd I/F are prepared. AxiMtPRdAddr is equal to the start address of the active area of Tx buffer (TxBufAddr#0). Also, AxiMtPRdLen is equal to UserBufSize (N) for every run loop, except the last loop which is equal to the remaining value (N1). Then, AxiMtPRdReq is asserted to '1' to send the request to AxiMtPRd.

- 5) After that, AxiPRdBusy is asserted to '1' to confirm the request is accepted. The state enters to stWtEnd to wait until the operation of AxiPRd is done.

- 6) When AxiPRdBusy is de-asserted to '0', the state changes to the last state stUpParam.

- 7) In stUpParam, the internal signals are updated. rTrnCnt decreases the value to show the remaining transfer length. UserTxBufSel is increased to show the next active area of Tx Buffer. UserTxBufClr of the active area (area#0) is asserted to '1' for one cycle to clear UserTxBufValid flag. Therefore, UserTxBufValid of the active area is de-asserted in the next clock cycle. Next, the state returns to stChkSize.

- 8) The next state is determined by rTrnCnt Value.

- a. If rTrnCnt  $\neq$  0, repeat step 2) 7) to read the data from the next area of Tx buffer. When the next buffer is TxBuffer#1, use bit1 of UserTxBufValid and UserTxBufClr to operate.

- b. If rTrnCnt = 0, the state returns to stldle. After that, UserTxBusy is de-asserted to '0'.

Figure 2-4 Tx transfer of MtMainCtrl timing diagram

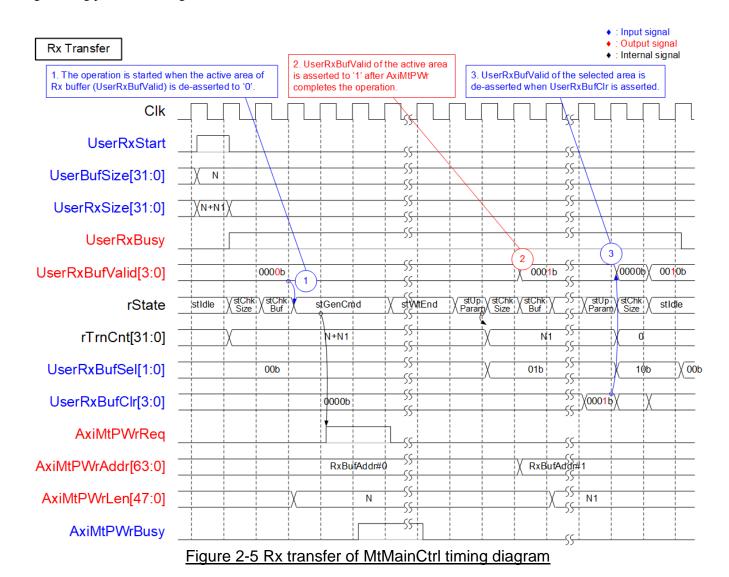

Figure 2-5 shows the details for Rx transfer operation which the request is generated to AxiMtPWr and Rx buffer is applied. The work flow of Rx transfer is almost similar to Tx transfer, but it uses Rx parameter and AxiMtPWr interface. The description in Figure 2-5 shows only the different point between Rx transfer and Tx transfer. The transfer direction of Rx buffer is inversed from Tx buffer, so UserRxBufValid is asserted by MtMainCtrl and UserRxBufClr is the input from CPU.

- In stChkBuf, UserRxBufValid of the active area must be de-asserted to '0' (no data available) before asserting the request to AxiMtPWr. After that, the data is written to the Main memory.

- 2) After AxiMtPWr finishes writing the data in each loop, UserRxBufValid of the active area is asserted to '1'.

- 3) When CPU finishes reading the data from the Main memory, UserRxBufClr is asserted. After that, the buffer status is empty.

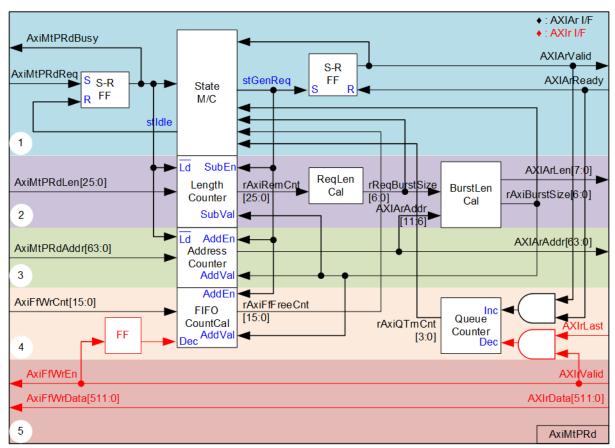

#### 2.1.2 AxiMtPRd

Figure 2-6 AxiMtPRd Block diagram

According to AXI4 standard, AXIAr I/F which is applied to send the read command request and AXIr I/F which is applied to transfer the data stream can be operated parallelly. Therefore, the logic inside AxiMtPRd is designed to send the new read command request via AXIAr I/F without waiting the data returned via AXIr I/F to achieve the best performance.

The operation is started when the user asserts AxiMtPRdReq along with AxiMtPRdLen (Total transfer length in 64-byte unit) and AxiMtPRdAddr (Start address of the Main memory in byte unit). After that, the read command request (AXIArValid) is generated by the State machine (Block no.1). Block no.2 is the logic to set the transfer size (AXIArLen) of each command request which can be equal to three values – 1, 8, or 64. Length Counter loads the total length from user (AxiMtPRdLen) before starting the operation. It calculates the remaining transfer size (rAxiRemCnt) after generating each request to AXIAr I/F. The remaining transfer size is fed to ReqLenCal to find the maximum transfer size of each request (rReqBurstSize). However, it needs to check the current address (AXIArAddr[11:6]) to confirm that this transfer does not cross the address boundary, designed by BurstLenCal block. The actual transfer size (AXIArLen) may be less than rReqBurstSize value if the current address is not aligned to the requested transfer size. Block no.3 is the address counter that calculates the next start address (AXIArAddr) after generating each command request to AXIAr I/F.

Block no.4 is the flow control logic to pause the new request that is generated by State machine. Two factors must be calculated before sending the new request. First is the actual free space size that is available in AxiTxFIFO (rAxiFfFreeCnt), calculated by FIFOCountCal. The current value of FIFO data counter (AxiFfWrCnt) is read and then added by the amount of data that is requested but does not transfer to be the usage size. The free space size is computed by using NOT logic to the used size. The new request is generated when the free space size is enough for storing the data of the new request. The second factor is the number of command request that does not receive the data (rAxiQTrnCnt), calculated by Queue Counter. The counter is up-counted when the new command request is asserted and down-counted when the last data of each request is received. AxiMtPRd uses 4-bit Queue counter, so State machine can create up to 15 commands (rAxiQTrnCnt=1111b) without waiting the new data is transferred on AxirData. The last block, Block no.5, shows the data path that is directly mapped from Axir I/F to AxiFIFO I/F.

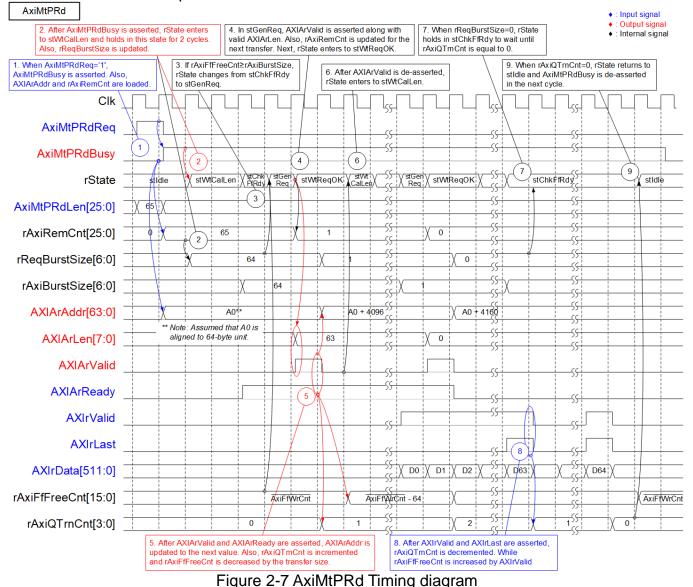

Figure 2-7 shows the timing diagram of AxiMtPRd logic when the user command request sets total transfer size to 65 and the start address on AxiPRdAddr (A0) is aligned to 64-byte unit. Two read command requests are generated by AxiMtPRd. First request is 64-beat transfer while the second request is 1-beat transfer. The details are described as follows.

- 1) The new command request (AxiMtPRdReq) is asserted to '1' along with the valid AxiMtPRdAddr (the start address of Main memory) and AxiMtPRdLen (total transfer size in 64-byte unit). AxiMtPRd asserts AxiMtPRdBusy to '1' to accept the request. Meanwhile, AXIArAddr loads the initial value from AxiMtPRdAddr and rAxiRemCnt loads the initial value from AxiMtPRdLen.

- 2) After AxiMtPRdBusy is asserted, rState enters to stWtCalLen to start calculating the transfer size of this command request, sent to AXIAr I/F. If rAxiRemCnt is more than or equal to 64, rReqBurstSize (the maximum request size) is set to 64. Otherwise, it is set by rAxiRemCnt. rReqBurstSize and the lower bit of AxiArAddr are read to calculate rAxiBurstSize. rAxiBurstSize may be less than rReqBurstSize if the lower bit of AxiArAddr is not aligned to rReqBurstSize. The state holds in stWtCalLen for two clock cycles to wait until rAxiBurstSize is valid before entering to stChkFfRdy.

- 3) In stChkFfRdy, it holds in this state to wait until the FIFO has enough free space for this transfer (rAxiFfFreeCnt ≥ rAxiBurstSize) when there is remaining command request to generate (rAxiRemCnt≠0). After that, it enters to stGenReq.

Note: Step 7 shows the example when all command request is generated.

- 4) The new command request is generated when rState enters to stGenReq which is one-cycle state. In the next clock, rState enters to stWtReqOK. AXIArValid is asserted and AXIArLen loads the value from the calculation unit. AXIAr I/F output signals hold the value until the request is accepted by asserting AXIArReady to '1'.

- 5) When the command request is accepted (AXIArValid='1' and AXIArReady='1'), AXIArAddr is updated to the next value and rAxiQTrnCnt is incremented. While rAxiFfFreeCnt is decreased by the current transfer size (64).

Note: rAxiFfFreeCnt is decreased when the request is sent to compensate the amount of

- the data that does not received from the latest request.

6) After AXIArValid is de-asserted to '0', rState returns to stWtCalLen to wait until the next transfer size (rAxiBurstSize) is valid. Step 2) 6) are repeated to generate the second request to AXIAr I/F.

- 7) In stChkFfRdy, if there is no more command request to generate (rReqBurstCnt=0), rState holds the value to wait until all data are transferred completely (rAxiQTrnCnt=0).

- 8) The data interface is run independently. The data transfer can be started any time. When the last data of each request is received (AXIrLast='1' and AXIrValid='1'), rAxiQTrnCnt is decremented. While rAxiFfFreeCnt is incremented every cycle that AXIrValid is asserted. Finally, when the last data is received, rAxiQTrnCnt is equal to 0 and rAxiFfFreeCnt (the free size) is equal to the NOT value of AxiFfWrCnt (the used size).

- 9) After the operation is done, rState returns to stldle and then AxiRdBusy is de-asserted to '0'. After that, MtMainCtrl can send the new command to AxiMtPRd.

#### 2.1.3 AxiMtPWr

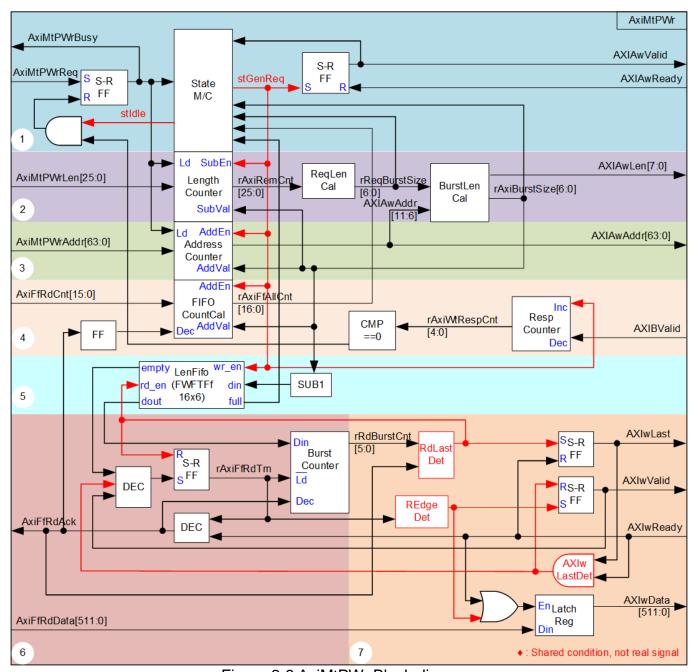

Figure 2-8 AxiMtPWr Block diagram

Similar to AxiMtPRd module, the write command request via AXIAw I/F can be generated without starting data transferring via AXIw I/F. Therefore, the logics for controlling the AXIAw I/F and AXIw I/F are designed individually. As shown in Figure 2-8, the logic inside AxiMtPWr can be divided to three parts. First is the logic for interface with AXIAw I/F which is shown in Block no.1 – no.4. Second is Block no.5 which is the small FWFT FIFO that stores the transfer length which is requested to AXIAw I/F for controlling data transfer in the AXIw I/F. Finally, Block no.6 and no.7 are the logic for interface with AXIw I/F.

Block no.1 is the State machine that is the core engine to generate the write command request (AXIAwValid) to AXIAw I/F. The operation of the State machine is almost similar to the State machine inside AxiMtPRd. The busy flag (AxiMtPWrBusy) is asserted after the user request (AxiMtPWrReq) is asserted to '1'. The operation is done and AxiMtPWrBusy is de-asserted when all write responses are received via AXIB I/F. Block no.2 is the logic to calculate the transfer length (AXIAwLen) of each command request. This block uses the same logic as Block no.2 inside AxiMtPRd module. Three transfer sizes are supported – 1, 8, or 64, depending on the remaining transfer size (rAxiRemCnt) and the lower bit of the current address (AxiAwAddr[11:6]). Block no.3 - the address counter also uses the same logic as AxiMtPRd module. Block no.4 is the flow control logic to determine the amount of data that is stored in AxiRxFIFO. The actual remaining data size (rAxiFfAllCnt) is calculated by reading the current data count of AxiRxFIFO (AxiFfRdCnt) and then subtracted by the amount of data that is requested but does not transfer. The new command request can be generated when rAxiFfAllCnt is more than or equal to rAxiBurstSize. While AxiMtPRd uses Queue Counter, AxiMtPWr uses Resp Counter to check if the operation is done. The Resp Counter is incremented when the Write request is asserted and then decremented when the write response is received (AXIBValid='1'). If rAxiWtRespCnt = 0, the data of all command request is transferred completely.

As shown in Block no.5, small FWFT FIFO is integrated to store the transfer length of each Write request to AXIAw I/F. The data interface inside Block no.6 reads this value to control the transfer size of each data transfer loop. FIFO depth is 16, so the State machine can generate up to 16 write command requests (FIFO depth) without starting transferring data to AXIw I/F.

Block no.6 is the logic which loads the transfer length of each request from LenFifo and then reads the data from AxiRxFIFO for transferring to AXIw I/F. AxiRxFIFO is FWFT type, so the read enable is called AxiFfRdAck (read acknowledge). The core signal of this block is rAxiFfRdTrn which is asserted while transferring the data. The operation begins by asserting rAxiFfRdTrn to '1' when empty flag of LenFIFO is de-asserted and the data interface returns to Idle (AXIwValid='0' or the last data is sent). The operation is done by de-asserting rAxiFfRdTrn to '0' when the last data is read from AxiRxFIFO (RdLastDet is found). Burst Counter is designed to count the transfer size of each request. It loads the initial value from LenFIFO and then decreases the value when each data is read from AxiRxFIFO (AxiFfRdAck='1'). The last data is detected by monitoring rRdBurstCnt=0. When AXIw I/F is not ready to receive the data (AXIwReady='0'), AxiFfRdAck is de-asserted to pause reading the next data from AxiRxFIFO.

Lastly, Block no.7 is the output register to transfer the data to AXIw I/F. AXIwValid is always asserted to '1' from the first data to the final data of each request size. Therefore, it is asserted when detecting rising edge of rAxiFfRdTrn (the data of new request is started). Also, it is de-asserted to '0' after transferring the final data completely. AXIwLast is asserted to '1' when the last data is read from AxiRxFIFO. To synchronous with AXIwValid, the read data from AxiRxFIFO (AxiFfRdData) must store to Latch register before forwarding to AXIwData.

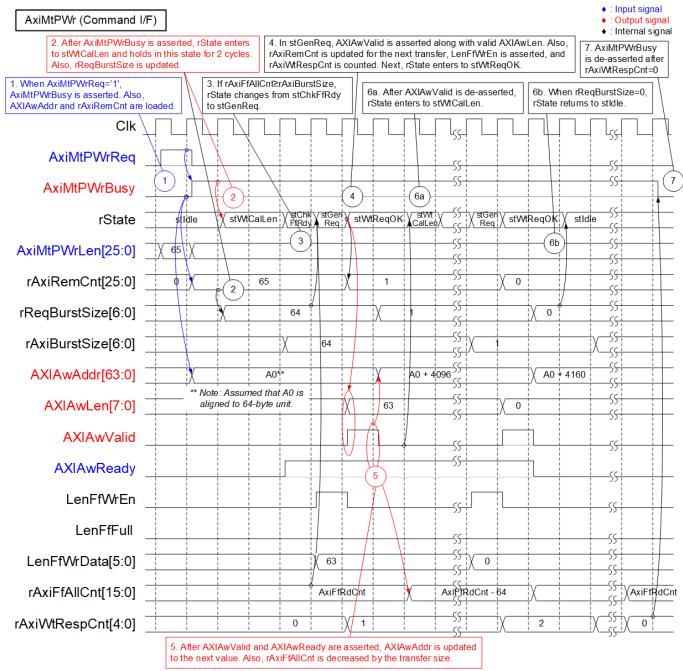

Figure 2-9 shows timing diagram of command interface (AXIAw I/F) which is controlled by the State machine. It shows the example when user sets transfer size to 65 and the start address (AxiMtPWrAddr) is aligned to 64-byte unit. Therefore, two write command requests are created – 64-beat transfer and 1-beat transfer, respectively.

Figure 2-9 Command I/F of AxiMtPWr Timing diagram

- 1) The new command request (AxiMtPWrReq) is asserted to '1' along with the valid AxiMtPWrAddr (the start address of Main memory) and AxiMtPWrLen (total transfer size in 64-byte unit). AxiMtPWr asserts AxiMtPWrBusy to '1' to accept the request. Meanwhile, AXIAwAddr loads the initial value from AxiMtPWrAddr and rAxiRemCnt loads the initial value from AxiMtPWrLen.

- 2) After AxiMtPWrBusy is asserted, rState enters to stWtCalLen to start calculating the transfer size of this command request to AXIAw I/F. If rAxiRemCnt is more than or equal to 64, rReqBurstSize (the maximum request size) is set to 64. Otherwise, it is set by rAxiRemCnt. rReqBurstSize and the lower bit of AxiAwAddr are read to calculate rAxiBurstSize. rAxiBurstSize may be less than rReqBurstSize if the lower bit of AxiArAddr is not aligned to rReqBurstSize. The state holds in stWtCalLen for two clock cycles to wait until rAxiBurstSize is valid before entering to stChkFfRdy.

- 3) In stChkFfRdy, it holds in this state to wait until the FIFO has enough data for this transfer (rAxiFfAllCnt≥rAxiBurstSize). After that, it enters to stGenReq.

- 4) The new command request is generated when rState enters to stGenReq which is one-cycle state. In the next clock, rState enters to stWtReqOK. AXIAwValid is asserted and AXIAwLen loads the value from the calculation unit. AXIAw I/F output signals hold the value until the request is accepted by asserting AXIAwReady to '1'. While rState=stGenReq, the transfer length (rAxiBurstSize-1) is written to LenFifo by asserting LenFfWrEn to '1'. Also, rAxiWtRespCnt is incremented.

- 5) When the command request is accepted (AXIAwValid='1' and AXIAwReady='1'), AXIAwAddr is updated to the next value and rAxiFfAllCnt is decreased by the current transfer size (64).

- Note: rAxiFfAllCnt is decreased when the request is sent to compensate the amount of the data that does not received from the latest request. After each data is received from AxiRxFIFO (AxiFfRdAck='1'), rAxiFfAllCnt is incremented to reduce the amount of compensated data.

- 6) After AXIAwValid is de-asserted to '0', rState reads the next request size (rReqBurstSize).

- a. If rReqBurstSize≠0, it returns to stWtCalLen and step 2) 6) are repeated for operating the next request.

- b. If rReqBurstSize=0, rState returns to stldle.

- 7) After all data are transferred completely and all responses are received, rAxiWtRespCnt is equal to 0 and then rAxiWrBusy is de-asserted to '0'. After that, MtMainCtrl can send the new command to AxiMtPWr.

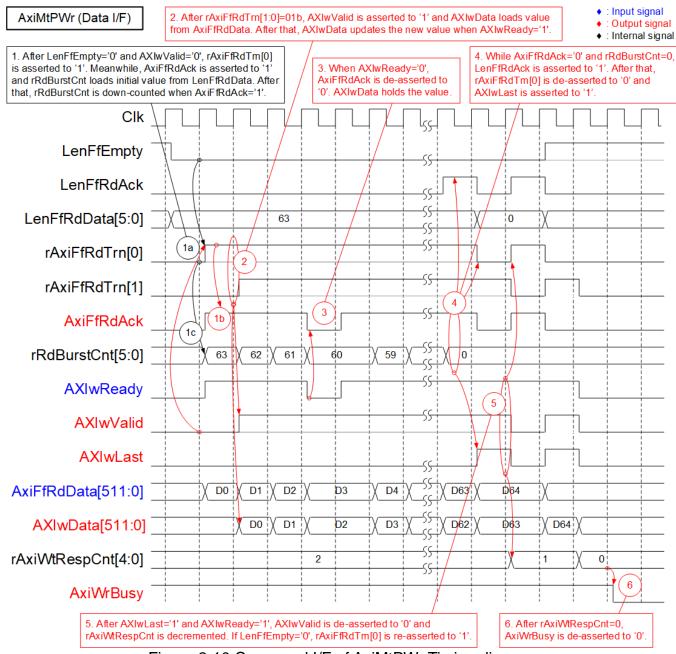

Figure 2-10 shows timing diagram of data interface (AXIw I/F) which is designed to transfer the data from AxiRxFIFO which is FWFT type to AXIw I/F. The example shows two data transfers, i.e., 64-beat transfer and 1-beat transfer, matched to Figure 2-9.

Figure 2-10 Command I/F of AxiMtPWr Timing diagram

- 1) After the new command request is generated to AXIAw I/F, the empty flag of LenFifo (LenFfEmpty) is de-asserted to '0'. The data interface starts the operation by asserting rAxiFfRdTrn[0] to '1'. Before asserting rAxiFfRdTrn[0], it needs to match one of two conditions. The data interface is Idle (AXIwValid='0', shown in this step) or the last data is completely transferred (AXIwValid='1' and AXIwLast='1', shown in step 5). At the same time as rAxiFfRdTrn[0] asserted, AxiFfRdAck is also asserted to '1' to read the next data from AxiRxFIFO. While there is no data transferring, rRdBurstCnt always loads the initial value from LenFfRdData. After that, rAxiFfRdTrn[0] is always asserted to '1' until reading the last data of this transfer (D63) from AxiRxFIFO. While rRdBurstCnt is down-counted when AxiFfRdAck='1' to show the amount of remaining data in this transfer.

- 2) Next, rAxiRdTrn[1] which is rAxiRdTrn[0] with one-clock latency is asserted to '1'. By detecting the rising edge of rAxiRdTrn[0], it mentions that the first data from AxiRxFIFO is ready. Therefore, AXIwValid is asserted to '1' and AXIwData loads the value from AxiFfRdData. After that, AXIwValid is always asserted to '1' until the last data is transferred. AXIwData loads the remaining data when the new data is read from AxiRxFIFO by checking AXIwReady='1' (AXIwReady='1' can be represented to AxiFfRdAck='1').

- 3) When AXIw I/F is not ready to receive the data by de-asserting AXIwReady to '0', the data interface must pause the transmission by de-asserting AxiFfRdAck to '0'. AXIwData and other AXIw I/F signals hold the same value until AXIwReady is re-asserted to '1'.

- 4) As the last data is read from AxiRxFIFO (AxiFfRdAck='1' and rRdBurstCnt=0), LenFfRdAck is asserted to '1' to flush the current data and read the next data from LenFifo. In the next clock, rAxiFfRdTrn[0] is de-asserted to '0' and the last data is transferred to AXIw I/F (AXIwLast='1' and AXIwData=D63).

- 5) After the last data is accepted by AXIw I/F (AXIwLast='1' and AXIwReady='1'), AXIwValid is de-asserted to '0' and rAxiWtRespCnt is decremented. Also, if LenFifo has more data (LenFfEmpty='0'), step 1 step 5 are repeated to start the next data transfer which is 1-beat transfer.

- 6) After all data is completely transferred, rAxiWtRespCnt is equal to zero. Next, AxiWrBusy is de-asserted to '0' to show user that the operation is done.

## 2.2 LAxi2Reg

AXI4-Lite is the interface of the hardware kernel for accessing the hardware registers. CPU uses this interface to set the parameters to the hardware and also monitor the hardware status while operating. 32-bit data bus size is applied. LAxi2Reg is run on application clock domain that is configured by the tool.

Figure 2-11 LAxi2Reg interface

LAxi2Reg consists of SAXIReg and UserReg. SAXIReg converts the AXI4-Lite signals to be the simple register interface which has 32-bit data bus size (similar to AXI4-Lite data bus size). UserReg includes the register file of the parameters and the status of the submodules. More details of SAXIReg and UserReg are described as follows.

: Register Write

### 2.2.1 SAXIReg

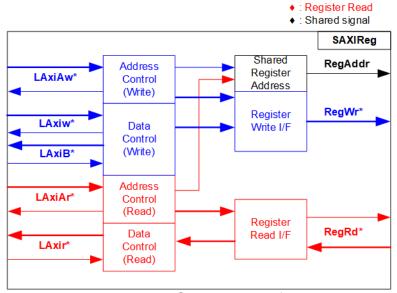

Figure 2-12 SAXIReg Interface

The signal on AXI4-Lite bus interface can be split into five groups, i.e., LAxiAw\* (Write address channel), LAxiw\* (Write data channel), LAxiB\* (Write response channel), LAxiAr\* (Read address channel), and LAxir\* (Read data channel). More details to build custom logic for AXI4-Lite bus is described in following document.

https://forums.xilinx.com/xlnx/attachments/xlnx/NewUser/34911/1/designing\_a\_custom\_axi\_slave\_rev1.pdf

According to AXI4-Lite standard, the write channel and the read channel are operated independently. Also, the control and data interface of each channel are run separately. The logic inside SAXIReg to interface with AXI4-Lite bus is split into four groups, i.e., Write control logic, Write data logic, Read control logic, and Read data logic as shown in the left side of Figure 2-12. Write control I/F and Write data I/F of AXI4-Lite bus are latched and transferred to be Write register interface. Similarly, Read control I/F of AXI4-Lite bus are latched and transferred to be Read register interface. While the returned data from Register Read I/F is transferred to AXI4-Lite bus. In register interface, RegAddr is shared signal for write and read access. Therefore, it loads the address from LAxiAw for write access or LAxiAr for read access.

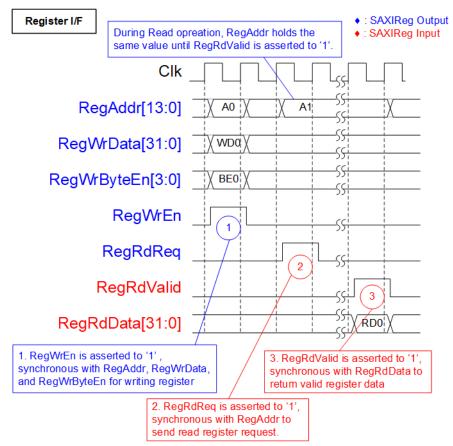

The simple register interface is compatible with single-port RAM interface for write transaction. The read transaction of the register interface is slightly modified from RAM interface by adding RdReq and RdValid signals for controlling read latency time. The address of register interface is shared for write and read transaction, so user cannot write and read the register at the same time. The timing diagram of the register interface is shown in Figure 2-13.

Figure 2-13 Register interface timing diagram

- 1) To write register, the timing diagram is similar to single-port RAM interface. RegWrEn is asserted to '1' with the valid signal of RegAddr (Register address in 32-bit unit), RegWrData (write data of the register), and RegWrByteEn (the write byte enable). Byte enable has four bits to be 4-byte data enable. Bit[0], [1], [2], and [3] are equal to '1' when RegWrData[7:0], [15:8], [23:16], and [31:24] are valid, respectively.

- 2) To read register, SAXIReg asserts RegRdReq to '1' with the valid value of RegAddr. 32-bit data must be returned after receiving the read request. The slave must monitor RegRdReq signal to start the read transaction. During read operation, the address value (RegAddr) does not change the value until RegRdValid is asserted to '1'. Therefore, the address can be used for selecting the returned data by using multiple multiplexers.

- 3) The read data is returned on RegRdData bus by the slave with asserting RegRdValid to '1'. After that, SAXIReg forwards the read value to LAxir\* interface.

## 2.2.2 UserReg

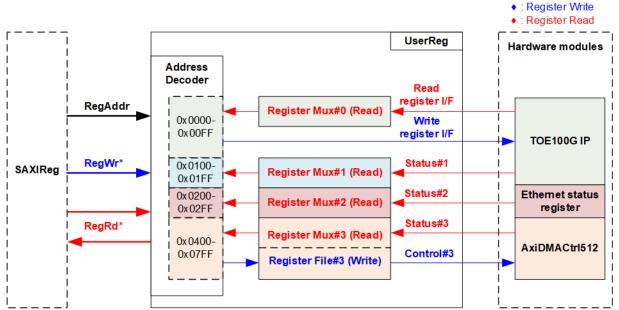

Figure 2-14 UserReg block diagram

UserReg consists of many registers for interfacing with the hardware submodules, i.e., TOE100G-IP, Ethernet system, and AxiDMACtrl512. The address for write or read access is decoded by Address decoder to select the active register. There are four addressing areas, as shown in Figure 2-14.

- 1) 0x0000 0x00FF: TOE100G-IP register interface area

- 2) 0x0100 0x01FF: TOE100G-IP status area

- 3) 0x0200 0x02FF: Ethernet system status area

- 4) 0x0400 0x07FF: AxiDMACtrl512 control and status area

Address decoder decodes the upper bits of RegAddr for selecting the active address area while the lower bits is applied to select the active register in each area. The register file inside UserReg is 32-bit data size and write byte enable (RegWrByteEn) is not used, so the CPU must use 32-bit pointer for writing these registers. There are many status registers in UserReg, so multi-level multiplexers are applied to return the read value. In this design, the latency time of read data is equal to four clock cycles, so RegRdValid is created by RegRdReq with asserting four D Flip-flops. More details of the address mapping within UserReg module are shown in Table 2-1.

## Table 2-1 Register map Definition

| Address               | Register Name                                                                                    |

|-----------------------|--------------------------------------------------------------------------------------------------|

| Wr/Rd                 | (Label in the TOE100DMATest.cpp)                                                                 |

|                       | Description                                                                                      |

|                       | BA+0x0000 – BA+0x00FF: TOE100GIP register interface (Write/Read access)                          |

| BA+0x0000             | DG_TOEIP_RST_INTREG_OFFSET                                                                       |

| <i>D,</i> 11 0×10000  | Mapped to RST register within TOE100G-IP.                                                        |

| BA+0x0004             | DG_TOEIP_CMD_INTREG_OFFSET                                                                       |

| <i>D,</i> ( ) 0,000 1 | Mapped to CMD register within TOE100G-IP.                                                        |

| BA+0x0008             | DG_TOEIP_SML_INTREG_OFFSET                                                                       |

|                       | Mapped to SML register within TOE100G-IP.                                                        |

| BA+0x000C             | DG_TOEIP_SMH_INTREG_OFFSET                                                                       |

|                       | Mapped to SMH register within TOE100G-IP.                                                        |

| BA+0x0010             | DG_TOEIP_DIP_INTREG_OFFSET                                                                       |

|                       | Mapped to DIP register within TOE100G-IP.                                                        |

| BA+0x0014             | DG_TOEIP_SIP_INTREG_OFFSET                                                                       |

|                       | Mapped to SIP register within TOE100G-IP.                                                        |

| BA+0x0018             | DG_TOEIP_DPN_INTREG_OFFSET                                                                       |

|                       | Mapped to DPN register within TOE100G-IP.                                                        |

| BA+0x001C             | DG_TOEIP_SPN_INTREG_OFFSET                                                                       |

|                       | Mapped to SPN register within TOE100G-IP.                                                        |

| BA+0x0020             | DG_TOEIP_TDL_INTREG_OFFSET                                                                       |

|                       | Mapped to TDL register within TOE100G-IP.                                                        |

| BA+0x0024             | DG_TOEIP_TMO_INTREG_OFFSET                                                                       |

|                       | Mapped to TMO register within TOE100G-IP.                                                        |

| BA+0x0028             | DG_TOEIP_PKL_INTREG_OFFSET                                                                       |

|                       | Mapped to PKL register within TOE100G-IP.                                                        |

| BA+0x002C             | DG_TOEIP_PSH_INTREG_OFFSET                                                                       |

|                       | Mapped to PSH register within TOE100G-IP.                                                        |

| BA+0x0030             | DG_TOEIP_WIN_INTREG_OFFSET                                                                       |

|                       | Mapped to WIN register within TOE100G-IP.                                                        |

| BA+0x0034             | DG_TOEIP_ETL_INTREG_OFFSET                                                                       |

|                       | Mapped to ETL register within TOE100G-IP.                                                        |

| BA+0x0038             | DG_TOEIP_SRV_INTREG_OFFSET                                                                       |

|                       | Mapped to SRV register within TOE100G-IP.                                                        |

| BA+0x003C             | DG_TOEIP_VER_INTREG_OFFSET                                                                       |

|                       | Mapped to VER register within TOE100G-IP.                                                        |

| BA+0x0040             | DG_TOEIP_DML_INTREG_OFFSET                                                                       |

|                       | Mapped to DML register within TOE100G-IP.                                                        |

| BA+0x0044             | DG_TOEIP_DMH_INTREG_OFFSET                                                                       |

|                       | Mapped to DMH register within TOE100G-IP.                                                        |

|                       | BA+0x0100 - BA+0x01FF: TOE100GIP status (Write/Read access)                                      |

| BA+0x0100             | TOE100G-IP status                                                                                |

|                       | DG_TOEIP_USERSTS_INTREG_OFFSET                                                                   |

|                       | Wr – [8]: Asserted to '1' to clear this bit which shows the latched value of TimerInt.           |

|                       | Rd – [0]: Mapped ConnOn from TOE100G-IP.                                                         |

|                       | Rd – [8]: Latched value of TimerInt output from IP ('0': Normal, '1': TimerInt='1' is detected). |

| BA+0x0110             | Connection interrupt                                                                             |

|                       | DG_TOEIP_USERINT_INTREG_OFFSET                                                                   |

|                       | Wr – [0]: Set '1' to clear the connection interrupt.                                             |

|                       | Rd – [0]: Interrupt from Connon edge detection.                                                  |

|                       | ('1': Detect edge of ConnOn signal from TOE100G-IP, '0': ConnOn does not change the value.)      |

|                       | Note: ConnOn value can be read from DG_TOEIP_CONNON_INTREG_OFFSET.                               |

| g_toe100gip_alveo_refdesign.doc |                                                                                                                |  |

|---------------------------------|----------------------------------------------------------------------------------------------------------------|--|

| Address Register Name           |                                                                                                                |  |

| Wr/Rd                           | (Label in the TOE100DMATest.cpp)                                                                               |  |

|                                 | Description                                                                                                    |  |

|                                 | BA+0x0200 – BA+0x02FF: Ethernet status (Read access only)                                                      |  |

| DA - 00000                      |                                                                                                                |  |

| BA+0x0200                       | Ethernet linkup status                                                                                         |  |

|                                 | DG_EMAC_USERSTS_INTREG_OFFSET                                                                                  |  |

|                                 | Rd – [0]: Ethernet linkup status from 100G Ethernet MAC ('0'- Not linkup, '1'- Linkup).                        |  |

| BA+0x0204                       | IP Version of DG EMAC-IP                                                                                       |  |

|                                 | DG_EMAC_USERVER_INTREG_OFFSET                                                                                  |  |

|                                 | Rd – [31:0]: Mapped to IPVersion of DG-EMAC. Not used when DG-EMAC is not implemented.                         |  |

|                                 | BA+0x0400 – BA+0x07FF: AxiDMACtrl512 control and status (Write/Read access)                                    |  |

|                                 | Note: BA+0x0600 – BA+0x06FF: Tx buffer parameters [Host -> Card]                                               |  |

|                                 | BA+0x0700 – BA+0x07FF: Rx buffer parameters [Card -> Host]                                                     |  |

| BA+0x0400                       | AxiDMACtrl512 reset                                                                                            |  |

|                                 | DG_DMA_RESET_OFFSET                                                                                            |  |

|                                 | Wr/Rd – [0]: Reset signal to AxiDMACtrl512 module ('1'-Reset, '0'-Clear).                                      |  |

| BA+0x0404                       | AxiDMACtrl512 command                                                                                          |  |

|                                 | DG_DMA_COMMAND_OFFSET                                                                                          |  |

|                                 | Wr – [0]: Start Tx transfer. Asserted to '1' to start Tx transfer on AxiDMACtrl512. This flag is auto-cleared. |  |

|                                 | Wr – [1]: Start Rx transfer. Asserted to '1' to start Rx transfer on AxiDMACtrl512. This flag is auto-cleared. |  |

| BA+0x0408                       | AxiDMACtrl512 status                                                                                           |  |

|                                 | DG_DMA_STATUS_OFFSET                                                                                           |  |

|                                 | Rd – [0]: Tx transfer busy flag. Asserted to '1' when AxiDMACtrl512 is operating Tx transfer.                  |  |

|                                 | Rd – [1]: Rx transfer busy flag. Asserted to '1' when AxiDMACtrl512 is operating Rx transfer.                  |  |

|                                 | Rd – [9:8]: The active area of Tx buffer that is in operating.                                                 |  |

|                                 | (00b-Tx buffer#0, 01b-Tx buffer#1, 10b-Tx buffer#2, 11b-Tx buffer#3)                                           |  |

|                                 | Rd – [17:16]: The active area of Rx buffer that is in operating.                                               |  |

|                                 | (00b-Rx buffer#0, 01b-Rx buffer#1, 10b-Rx buffer#2, 11b-Rx buffer#3)                                           |  |

| BA+0x0410                       | Total transmit length of AxiDMACtrl512                                                                         |  |

| D/(10X0+10                      | DG_DMA_TOTAL_TRANSMIT_LENGTH_OFFSET                                                                            |  |

|                                 | Wr – [31:0]: Total amount of data for Tx transfer in 512-bit unit. Valid range is 1-0xFFFFFFF.                 |  |

|                                 | Rd – [31:0]: Current amount of data that is completely transmitted in 512-bit unit. Valid while operating.     |  |

| BA+0x0414                       | Total receive length of AxiDMACtrl512                                                                          |  |

| Битохотт                        | DG_DMA_TOTAL_RECEIVE_LENGTH_OFFSET                                                                             |  |

|                                 | Wr – [31:0]: Total amount of data for Rx transfer in 512-bit unit. Valid range is 1-0xFFFFFFF.                 |  |

|                                 | Rd – [31:0]: Current amount of data that is completely received in 512-bit unit. Valid while operating.        |  |

| BA+0x0418                       | Tx buffer status of AxiDMACtrl512                                                                              |  |

| DA+0X0410                       | DG_DMA_TXBUFFER_VALID_OFFSET                                                                                   |  |

|                                 |                                                                                                                |  |

|                                 | Wr/Rd – [3:0]: Each bit is mapped to show the status of each area for Tx buffer.                               |  |

|                                 | Bit[0], [1], [2], and [3] show the status of Tx buffer#0, #1, #2, and #3, respectively.                        |  |

|                                 | Wr: Asserted to '1' when the data in Tx buffer#i is ready for Tx transfer.                                     |  |

|                                 | Rd: '0'-No data stored in Tx buffer#1, '1'-Has data stored in Tx buffer#i.                                     |  |

|                                 | In Tx transfer, this flag is asserted by CPU when the data is completely prepared.                             |  |

| DA - 00440                      | It is de-asserted by the hardware kernel when all data is completely read.                                     |  |

| BA+0x041C                       | Rx buffer valid of AxiDMACtrl512                                                                               |  |

|                                 | DG_DMA_RXBUFFER_VALID_OFFSET                                                                                   |  |

|                                 | Wr/Rd – [3:0]: Each bit is mapped to show the status of each area for Rx buffer.                               |  |

|                                 | Bit[0], [1], [2], and [3] show the status of Rx buffer#0, #1, #2, and #3, respectively.                        |  |

|                                 | Wr: Asserted to '1' to clear this bit which shows data ready status of Rx buffer#i.                            |  |

|                                 | Rd: '0'-No data stored in Rx buffer#1, '1'-Has data stored in Rx buffer#i.                                     |  |

|                                 | In Rx transfer, this flag is asserted by the hardware kernel when the data is completely prepared.             |  |

|                                 | It is de-asserted by CPU when all data is completely read.                                                     |  |

| BA+0x0480                       | Buffer size of AxiDMACtrl512                                                                                   |  |

|                                 | DG_DMA_BUFFER_SIZE_OFFSET                                                                                      |  |

|                                 | Wr/Rd – [31:0]: Mapped to the buffer size in byte unit. Maximum size is 4GB.                                   |  |

|                                 | Data bus size of DMA engine is 512 bits, so bit[5:0] of this register must be equal to 000000b.                |  |

|                                 | Note: The hardware kernel loads this register when the reset flag (DG_DMA_RESET_OFFSET) is asserted.           |  |

| Address     | Register Name                                                                                                                              |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| Wr/Rd       | (Label in the TOE100DMATest.cpp)                                                                                                           |

|             | Description                                                                                                                                |

|             | BA+0x0400 - BA+0x07FF: AxiDMACtrl512 control and status (Write/Read access)                                                                |

|             | Note: BA+0x0600 - BA+0x06FF: Tx buffer parameters [Host -> FPGA]                                                                           |

|             | BA+0x0700 - BA+0x07FF: Rx buffer parameters [FPGA -> Host]                                                                                 |

| BA-         | +0x0600 - BA+0x060F: Tx buffer#0 parameters, BA+0x0610 - BA+0x061F: Tx buffer#1 parameters,                                                |

| BA          | +0x0620 – BA+0x062F: Tx buffer#2 parameters, BA+0x0630 – BA+0x063F: Tx buffer#3 parameters                                                 |

| BA+0x0600   | 32-bit lower base address of Tx buffer#0 for AxiDMACtrl512                                                                                 |

|             | DG_DMA_TXBUFFER_LOW_ADDRESS_OFFSET(0)                                                                                                      |

|             | Wr/Rd - [31:0]: Mapped to the 32-bit lower address of Tx buffer#0 in the host memory.                                                      |

|             | Loaded while AxiDMACtrl512 reset is active.                                                                                                |

| BA+0x0604   | 32-bit higher base address of Tx buffer#0 for AxiDMACtrl512                                                                                |

|             | DG_DMA_TXBUFFER_HIGH_ADDRESS_OFFSET(0)                                                                                                     |

|             | Wr/Rd - [31:0]: Mapped to the 32-bit higher address of Tx buffer#0 in the host memory.                                                     |

|             | Loaded while AxiDMACtrl512 reset is active.                                                                                                |

| BA+0x0610 - | Tx buffer#1 parameters for AxiDMACtrl512                                                                                                   |

| BA+0x061F   | 0x0610: DG_DMA_TXBUFFER_LOW_ADDRESS_OFFSET(1)                                                                                              |

|             | 0x0614: DG_DMA_TXBUFFER_HIGH_ADDRESS_OFFSET(1)                                                                                             |

| BA+0x0620 - | Tx buffer#2 parameters for AxiDMACtrl512                                                                                                   |

| BA+0x062F   | 0x0620: DG_DMA_TXBUFFER_LOW_ADDRESS_OFFSET(2)                                                                                              |

| DA - 00000  | 0x0624: DG_DMA_TXBUFFER_HIGH_ADDRESS_OFFSET(2)                                                                                             |

| BA+0x0630 - | Tx buffer#3 parameters for AxiDMACtrl512                                                                                                   |

| BA+0x063F   | 0x0630: DG_DMA_TXBUFFER_LOW_ADDRESS_OFFSET(3)                                                                                              |

| DA.         | 0x0634: DG_DMA_TXBUFFER_HIGH_ADDRESS_OFFSET(3) -0x0700 – BA+0x070F: Rx buffer#0 parameters, BA+0x0710 – BA+0x071F: Rx buffer#1 parameters, |

|             | +0x0700 – BA+0x070F. Rx buffer#0 parameters, BA+0x0710 – BA+0x073F. Rx buffer#1 parameters                                                 |

| BA+0x0700   | 32-bit lower base address of Rx buffer#0 for AxiDMACtrl512                                                                                 |

| BA+0X0700   | DG_DMA_RXBUFFER_LOW_ADDRESS_OFFSET(0)                                                                                                      |

|             | Wr/Rd - [31:0]: Mapped to the 32-bit lower address of Rx buffer#0 in the host memory                                                       |

|             | Loaded while AxiDMACtrl512 is in reset phase.                                                                                              |

| BA+0x0704   | 32-bit higher base address of Rx buffer#0 for AxiDMACtrl512                                                                                |

|             | DG_DMA_RXBUFFER_HIGH_ADDRESS_OFFSET(0)                                                                                                     |

|             | Wr/Rd - [31:0]: Mapped to the 32-bit higher address of Rx buffer#0 in the host memory.                                                     |

|             | Loaded while AxiDMACtrl512 is in reset phase.                                                                                              |

| BA+0x0710 - | Rx buffer#1 parameters for AxiDMACtrl512                                                                                                   |

| BA+0x071F   | 0x0710: DG_DMA_RXBUFFER_LOW_ADDRESS_OFFSET(1)                                                                                              |

|             | 0x0714: DG_DMA_RXBUFFER_HIGH_ADDRESS_OFFSET(1)                                                                                             |

| BA+0x0720 - | Rx buffer#2 parameters for AxiDMACtrl512                                                                                                   |

| BA+0x072F   | 0x0720: DG_DMA_RXBUFFER_LOW_ADDRESS_OFFSET(2)                                                                                              |

|             | 0x0724: DG_DMA_RXBUFFER_HIGH_ADDRESS_OFFSET(2)                                                                                             |

| BA+0x0730 - | Rx buffer#3 parameters for AxiDMACtrl512                                                                                                   |

| BA+0x073F   | 0x0730: DG_DMA_RXBUFFER_LOW_ADDRESS_OFFSET(3)                                                                                              |

|             | 0x0734: DG_DMA_RXBUFFER_HIGH_ADDRESS_OFFSET(3)                                                                                             |

|             |                                                                                                                                            |

## 3 The host software

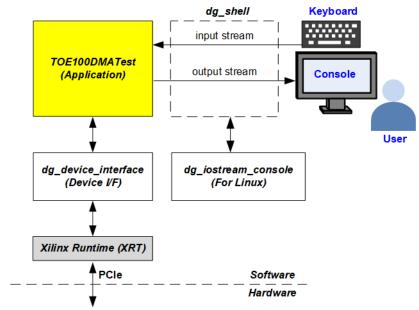

Figure 3-1 The software architecture in TOE100G-IP on Alveo card demo

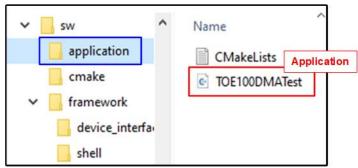

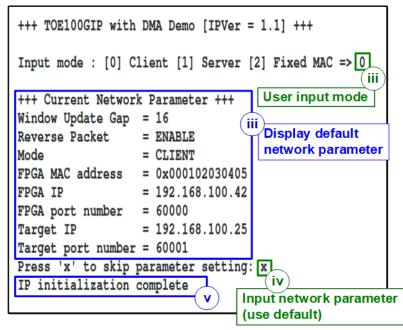

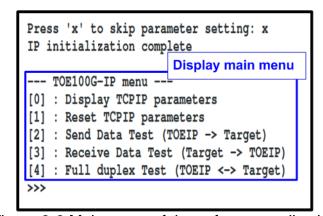

The host software for this demo consists of two software categories – the application and the framework. "TOE100DMATest" is the main application of this demo. While the framework has three source codes. First is "dg\_shell" which handles the user input (keyboard) and the output console (monitor). The input stream and the output stream on the Linux OS has its own control sequence, so the second framework – "dg\_iostream\_console" is designed by using specific command for Linux OS to handle the stream. Last is "dg\_device\_interface" which is applied to control the hardware interface on Alveo card by using Xilinx runtime (XRT). It includes the functions to write/read hardware registers and handle the process for memory allocation.

Xilinx Runtime Library (XRT) is the software interface for communicating between the application and the hardware kernels. When the hardware kernels are implemented on Alveo card, the interface is based on PCIe. More details about the Xilinx Runtime Library can be found from the following link.

https://www.xilinx.com/products/design-tools/vitis/xrt.html

More details of the software on the demo are describes as follows.

#### 3.1 Framework

There are two software frameworks that are designed for this demo, i.e., the device interface and the shell. The device interface framework makes a simple function of utilizing the Xilinx Runtime (XRT) for interfacing with the hardware kernels. While the shell framework handles the input and output of the console (Linux terminal) for user interface.

### 3.1.1 Device interface

Figure 3-2 Device interface framework

The device interface is used by the application for communicating with the hardware kernels through Xilinx Runtime Library (XRT). The application uses it to create a connection, to allocate the buffer, and to write/read the hardware registers. As shown in Figure 3-2, there are three source codes inside device\_interface directories.

- "dg\_device\_interface\_error\_codes.h": Define the returned value of the function for the device interface which may be "OK" status or error codes. The returned value of some functions in this class is referred to these definitions. The values are listed as follows

- DG OK

- DG\_DEV\_INTERFACE\_ERROR\_FAIL\_TO\_ASSOCIATE\_WITH\_XRT

- DG DEV INTERFACE ERROR DEVICE IS NOT OPENED

- DG\_DEV\_INTERFACE\_ERROR\_CANNOT\_OPEN\_DEVICE

- DG\_DEV\_INTERFACE\_ERROR\_CU\_NAME\_NOT\_FOUND

- DG\_DEV\_INTERFACE\_ERROR\_HOST\_MEMORY\_INTERFACE\_NOT\_FOUND

- DG DEV INTERFACE ERROR IP KERNEL AND HOST MEMORY MISMATCH

- DG DEV INTERFACE ERROR FAIL ALLOCATEBUFFER

- "dg\_device\_interface.h": Declare a class and functions which are defined in C++ source file (dg\_device\_interface.cpp). The header file determines which function can be or cannot be called from other class. Also, it declares variables in the class with the initial value if it is specified.

- "dg\_device\_interface.cpp": Design the general function for connecting the device, accessing the hardware register, and allocating/de-allocating the host memory. The function lists of the device interface framework are described as follows.

Note: The string of compute unit name (cu\_name) is defined as the constant in the software source code "TOE100DMATest:TOE100DMATest". This value must be updated if the user changes the hardware kernel name.

## **Device Connection**

| uint32_t CreateDeviceIF(void) |                                                                                                                                                                                                                                                                                                              |  |

|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Parameters                    | None                                                                                                                                                                                                                                                                                                         |  |

| Return value                  | DG_OK: Success, Error code: Error found                                                                                                                                                                                                                                                                      |  |

| Description                   | Use an XRT function to connect with the hardware platform to retrieve an information such as the CU (Compute Unit) address. The CU address is applied for writing/reading the hardware register. DG_OK is returned when CU name is correct (TOE100DMATest:TOE100DMATest). Otherwise, Error code is returned. |  |

| char* GetDeviceName(void) |                                                                     |  |

|---------------------------|---------------------------------------------------------------------|--|

| Parameters                | None                                                                |  |

| Return value              | Character pointer of the device name                                |  |

| Description               | Return a device name that is obtained while initializing the device |  |

|                           | interface from CreateDeviceIF function.                             |  |

| void Close(voi | void Close(void)                                                                                           |  |  |

|----------------|------------------------------------------------------------------------------------------------------------|--|--|

| Parameters     | None                                                                                                       |  |  |

| Return value   | None                                                                                                       |  |  |

| Description    | Use an XRT function to disconnect the software application from the hardware if the connection is created. |  |  |

## Write/Read Register

| uint32_t ReadIntReg(uint64_t offset) |                                                                                                                                                                                                                      |  |

|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Parameters                           | offset: The address offset of the hardware register to be read                                                                                                                                                       |  |

| Return value                         | Read value from the hardware register                                                                                                                                                                                |  |

| Description                          | Calculate the actual address by adding the CU address with the input offset. Next, use an XRT function and the actual address to read the data in the hardware register. Finally, return the read data back to user. |  |

| void WriteIntR | teg(uint64_t offset, uint32_t value)                                                                                                                                               |  |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Parameters     | offset: The address offset of the hardware register to be written                                                                                                                  |  |

|                | value: 32-bit unsigned value for writing to the register                                                                                                                           |  |

| Return value   | None                                                                                                                                                                               |  |

| Description    | Calculate the actual address by adding the CU address with the input offset. Next, use an XRT function and the actual address to write the input value into the hardware register. |  |

## Buffer Management

| uint32_t Alloca | uint32_t AllocateBuffer(uint32_t sizeInBytes, void*& HostAddr, uint64_t* HWAddr)                                                                                                                                                                                                                                                                                                                  |  |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Parameters      | sizeInBytes: The memory size for allocating in byte unit                                                                                                                                                                                                                                                                                                                                          |  |

|                 | HostAddr: The pointer of the virtual host base address                                                                                                                                                                                                                                                                                                                                            |  |

|                 | HWAddr: The pointer to the hardware base address.                                                                                                                                                                                                                                                                                                                                                 |  |

| Return value    | DG_OK: Success, Error code: Error found                                                                                                                                                                                                                                                                                                                                                           |  |

| Description     | Use an XRT function to retrieve an information of the hardware and then use this information to verify the connection between the hardware kernel and the host memory. After that, allocate the host memory via the XRT function (the memory size is set by the input). Finally, update the virtual host base address, hardware base address, and the local variables of the host memory details. |  |

| void FreeBuffe | void FreeBufferHostOnly(void)                                                                                                          |  |  |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Parameters     | None                                                                                                                                   |  |  |

| Return value   | None                                                                                                                                   |  |  |

| Description    | If the host memory is allocated, use an XRT function to free the host memory and clear the local variables of the host memory details. |  |  |

### 3.1.2 Shell

Figure 3-3 Shell framework

The shell framework (dg\_shell) handles the input and output stream on the Linux terminal (Console). It retrieves keyboard input, manages the input string, parses the input data type, and prints a string out to console. The shell framework uses an I/O stream console library (dg\_iostream\_console) to work with the Linux terminal, i.e., changing the terminal environment, getting the user keyboard input, and pushing the printed string output to terminal.

As shown in Figure 3-3, there are two source codes for handling I/O stream console.

- "dg\_iostream\_console.h": Declare a class and functions which are defined in C++ source file (dg\_iostream\_console.cpp). The header file determines which function can be or cannot be called from other class. Also, it declares variables in the class with the initial value if it is specified.

- "dg\_iostream\_console.cpp": Design the general function to manage the input and output stream on the Linux terminal environment such as writing a string on console, changing the terminal setting for utilizing by the shell, reverting the terminal setting to the original one, and getting the input character from the user through terminal. The function lists of the I/O stream classes are described as follows.

## Note:

- When constructing the "InStreamConsole" object, it requires the pointer of the output stream object.

- "KeyPressEnum" is a C++ enumeration declared in the header file (dg\_iostream\_console.h). It contains the keyboard input type for processing in the shell framework which are NORMAL, BACKSPACE, LEFTARROW, RIGHTARROW, DELETE, TAB, EOL, and CONTROL.

## OutStreamConsole class

| void write(const char* s, uint32_t numChars) |                                                                                                                                                              |

|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Parameters                                   | s: Pointer to the character for printing out on the console                                                                                                  |

|                                              | numChars: The character length of "s"                                                                                                                        |

| Return value                                 | None                                                                                                                                                         |

| Description                                  | Call function (fwrite) to write the output (stdout) by the character "s" which specifies the length from "numChars". Next, flush the output to the terminal. |

| void erase(uint32_t numChars) |                                                                          |

|-------------------------------|--------------------------------------------------------------------------|

| Parameters                    | numChars: The number of characters to delete from the terminal           |

| Return value                  | None                                                                     |

| Description                   | Delete the currently displayed character on the terminal which specifies |

| _                             | the length from "numChars".                                              |

## InStreamConsole class

| void NewSetting(void) |                                                                                                                                                                                                  |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Parameters            | None                                                                                                                                                                                             |

| Return value          | None                                                                                                                                                                                             |

| Description           | Change the Linux terminal setting to non-echo mode and to process an input from the terminal without endline character. The original setting is stored to a local variable for retrieving later. |

| void RestoreSetting(void) |                                                                                       |