## **Ultimate 10GbE network solution!**

19 February 2021

Design Gateway

Page 1

## Agenda

- 10GbE&TCP/IP Overview

- Advantage and Disadvantage of TCP on 10GbE

- TOE10G-IP core overview

- TOE10G-IP core description

- Initialization

- High-speed transmit

- High-speed reception

- User I/F, Buffer size parameterization

- Reference design

- Resource usage and real performance

## **10GbE Overview**

## What is 10GbE (10Giga-bit Ethernet)?

- Industrial standard high-speed network

- 10Gbps transfer speed

- Many connection type

TOE10G-IP is applicable to all 10GbE standard

| Connection Type       | Merit                                | Demerit                           | Note                            |  |

|-----------------------|--------------------------------------|-----------------------------------|---------------------------------|--|

| Optical Cable         | Low latency (100ns)<br>Long distance | Expensive                         | Needs optical module and cable  |  |

| Direct Attach         | Low cost                             | Short distance (5-<br>7m maximum) | Direct insertion to SFP+ socket |  |

| 10GBASE-T             | Low cost<br>Popular (RJ-45)          | High latency<br>(2us)             | Special coding<br>(LDPC)        |  |

| 100bC connection ture |                                      |                                   |                                 |  |

### 10GbE connection type

19 February 2021

Design Gateway

Page 3

## Advantage of TCP/IP on 10GbE

- Advantage of TCP/IP

- Standard Ethernet protocol

- Guaranteed data reliability

- Major OS provides protocol stack

- Disadvantage of TCP/IP

- Heavy CPU load due to complicated TCP process

- Difficult to raise performance(30-40% efficiency)

- Needs expensive high performance CPU

- **TOE10G-IP** core can provide ideal solution!

Design Gateway

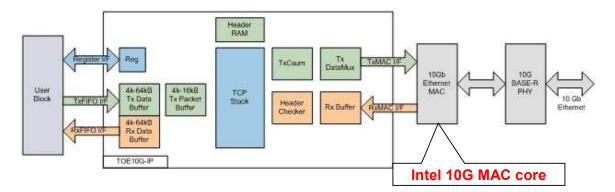

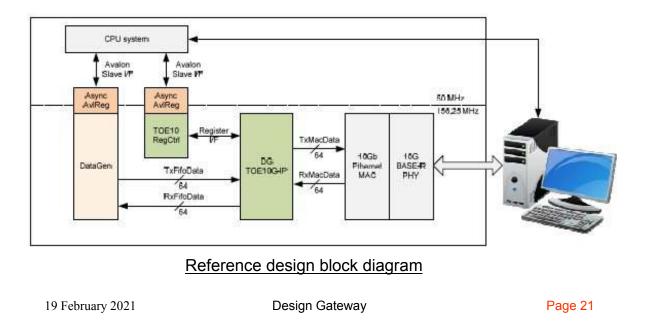

- TCP/IP off-loading engine for 10GbE

- Inserts between user logic and Intel 10G MAC module

- Fully hard-wired TCP control for both Tx and Rx

- Supports Full Duplex communication

### TOE10G-IP core block diagram

19 February 2021

Design Gateway

Page 5

Arria 10

## DG TOE10G-IP core Advantage 1

- Fully hard-wired TCP/IP protocol control

- Possible to build CPU-less network system

- Zero load for CPU

- Ultra high speed for both of Tx and Rx direction

- About 1200MByte/sec real transfer speed

- Guarantee transfer data reliability

- Tx: Automatic retry when No-ACK, Duplicate-ACK, timeout

- Rx: Automatic ACK control by Sequence number calculation

## TOE10G-IP core Advantage 2

### Selectable data buffer size

- Selectable buffer size of memory usage vs. performance

- Compatible with Intel MAC core (LL Ethernet 10G MAC)

- Also supports low cost 10GEMAC-IP from DesignGateway

- Many reference design on Intel evaluation board

- Full project for standard Intel board

- Free SOF-file for evaluation before purchase

- All source code (except IP-core) in design project

- Multiple Sessions design available for Server Application

- Supports 10GBASE-T as well as 10GBASE-R

- Applicable to low cost Cat6 cable and RJ45 connector

19 February 2021

Design Gateway

Page 7

# **TOE10G-IP core Operation**

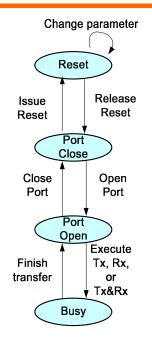

- Set parameter (IP-adr&MAC-adr, etc) during Reset

- Release Reset then initialize including ARP

- Idle state after initialization finish, wait command

- Port open by either of Active (Client) or Passive (Server) mode

- Tx and Rx operates individually (full-duplex)

- If want change parameter, move to Reset state (transfer/packet length can change except Busy)

### State Diagram

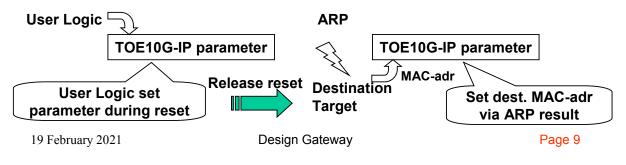

## • Set parameter to TOE10G-IP

- User logic can set parameter during TOE10G-IP reset

- Set IP address, MAC address, and Port number

- Release reset after parameter setting finish

- TOE10G-IP executes ARP after reset release

- Issue ARP to destination target

- Get MAC-adr of the target via ARP result

# High-Speed Tx

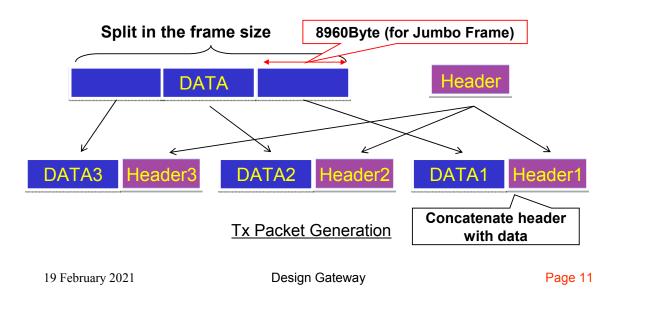

- Tx packet generation

- User Logic writes Tx data to TxFIFO

- Split Tx data in the frame size

- Split TX data in the frame size

Concatenate header with Tx data

- Automatic retransmit function

- Check ACK reply from destination

- Detect No-ACK, Duplicate-ACK, and Timeout

- Resend same packet by such ACK error detection

- Generate header and concatenate it with Tx data

- TOE10G-IP splits Tx data in the frame size

- Generate checksum and sequence number in TOE10G-IP

## D•G

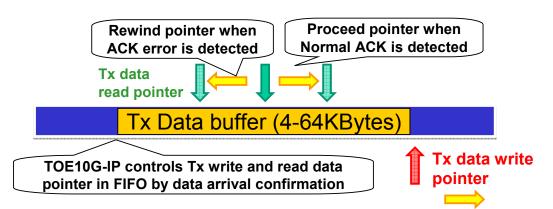

## **Automatic retransmit**

- Retransmit function by dedicated FIFO

- Proceed pointer by normal ACK reception

- Rewind pointer by illegal ACK reception

- TOE10G-IP controls pointer and retransmit operation

## **High-Speed Rx**

### Rx packet header check

Ignore packet if destination is not TOE10G-IP or if checksum is wrong

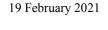

### Data reordering

- Reorder when sequence number skip is detected

- Avoid retransmit request for transfer efficiency

- If reordering is not possible, then send duplicate ACK

### Duplicate data management

- Check duplicate data in Rx packet

- Retrieve original data by trimming duplicate data part

**Design Gateway**

**Rx Packet Header Check**

Page 13

# Verify header check sum in Rx packet Also check following condition in TOE10G-IP

| Byte Offset | Protoco | Description             | Check condition                                            |

|-------------|---------|-------------------------|------------------------------------------------------------|

| 0-5         | ICMP    | Destination MAC adr     | Match with MAC adr set by SML/SMH register                 |

| 6-11        | ICMP    | Source MAC adr          | Match with target MAC adr set by ARP                       |

| 12-13       | ICMP    | Туре                    | = 0x0800 (IP packet)                                       |

| 14          | IP      | Version/Header          | = 0x45 (IPv4, IP header len=20)                            |

| 20          | IP      | Flag/Fragment OFS       | = b"000000" (no fragment)                                  |

| 23          | IP      | Protocol Number         | = 0x06(TCP packet )                                        |

| 26-29       | IP      | Source IP adr           | Match with IP adr set by DIP register                      |

| 30-33       | IP      | Destination IP adr      | Match with IP adr set by SIP register                      |

|             |         |                         | Match with DPN register or extracted target port number in |

| 34-35       | TCP     | Source port number      | Passive Open                                               |

| 36-37       | TCP     | Destination port number | Match with port number set by SPN register                 |

| 38-41       | TCP     | Sequence number         | Possible value within TOE2-IP core can process this packet |

**Design Gateway**

### Header check condition in Rx packet

## Function when SEQ number skip is detected

- Not accept any packet other than that can solve lost condition

### Data reordering function

- Recover data contiguous from lost-solved packet

- Keep performance by suppress resend request

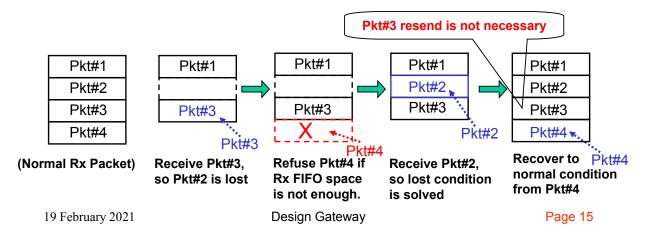

# Duplicate data trimming

- Detect data duplication and correct automatically

- Detect Rx data duplication by checking sequence number

- Trim duplicate block and retrieve contiguous data

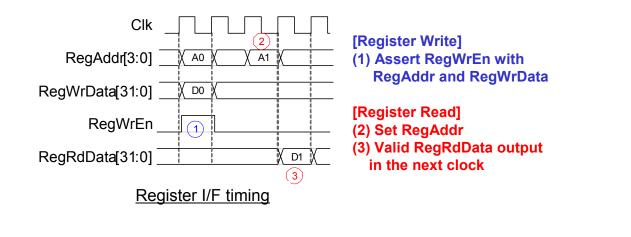

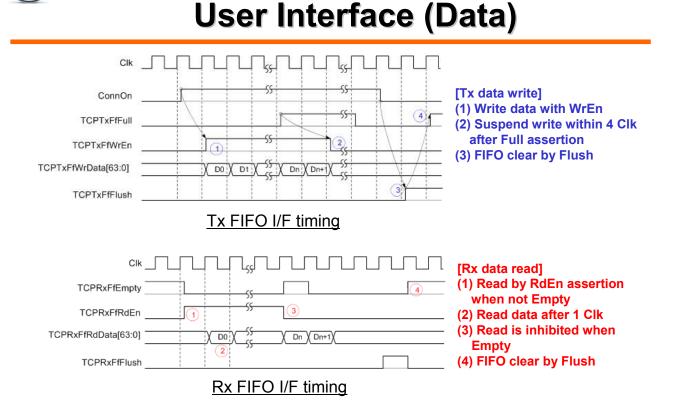

- 3 types of Register I/F, Tx FIFO I/F, and Rx FIFO I/F

- Register I/F for initial parameter setting and Tx/Rx command

- Tx FIFO I/F and Rx FIFO I/F is standard FIFO interface

**Design Gateway**

19 February 2021

TCP Officading Engine IP Core

Page 17

## **Buffer Capacity**

### • Parameterized 3 types of data buffer

- (1) Tx Data Buffer: 4KBytes 64KBytes

- (2) Tx Packet Buffer: 4KBytes 16KBytes

- (3) Rx Data Buffer: 4KBytes 64KBytes

### User can optimize resource usage and performance

| Generic Name  | Range | Description                                                    |

|---------------|-------|----------------------------------------------------------------|

| TxBufBitWidth | 9-13  | Set Tx data buffer size in address bit width                   |

|               |       | When set to 9, size is 4KBytes, when 13, 64Kbytes for example. |

| TxPacBitWidth | 9-11  | Set Tx packet buffer size in address bit width                 |

|               |       | When set to 9, size is 4Kbytes, when 11, 16KBytes for example  |

| RxBufBitWidth | 9-13  | Set Rx data buffer size in address bit width                   |

|               |       | When set to 9, size is 4KBytes, when 13, 64KBytes for example. |

Buffer size is selectable by parameterization

19 February 2021

Design Gateway

Page 19

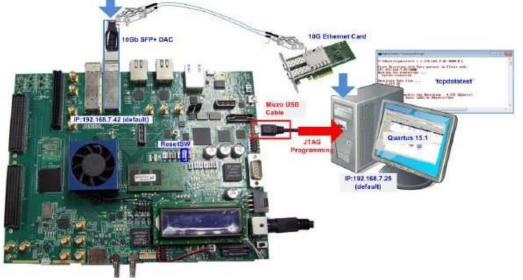

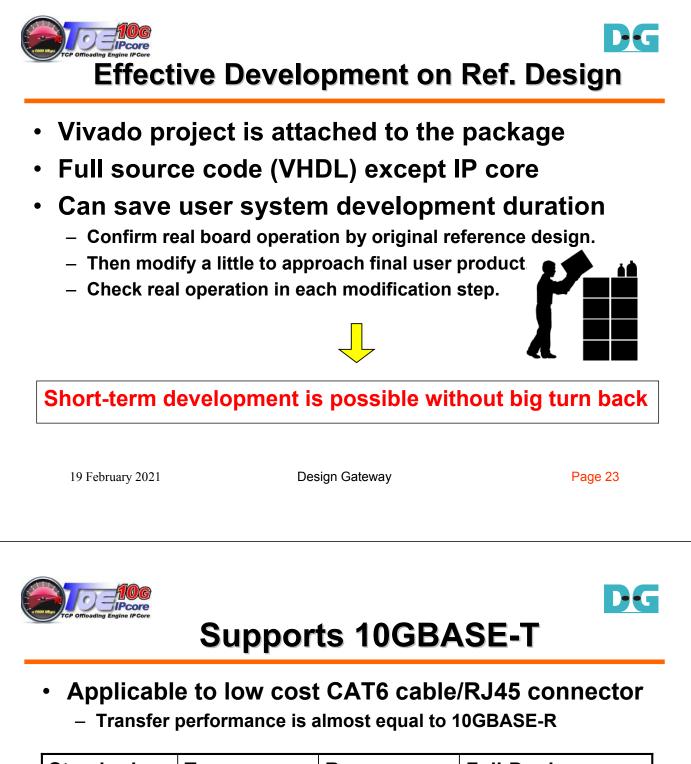

# Free SOF File for Evaluation

- Bit file for evaluation with Intel standard board

- Ready for A10SX,A10GX,C10GX,S10GX, IntelPAC board

- Measure transfer speed performance and data reliability

### QuartusII design project for real operation

- All source code (except IP-core) included in full project

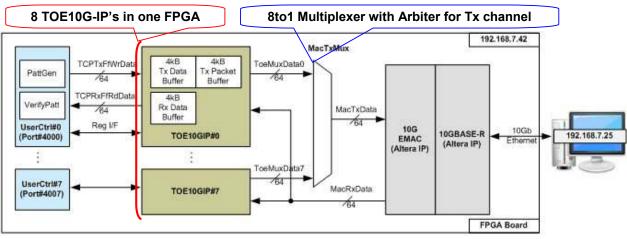

Reference design for Server Application

– 8 Instances in one FPGA to support 8 sessions operation

Multiple Sessions reference design block diagram

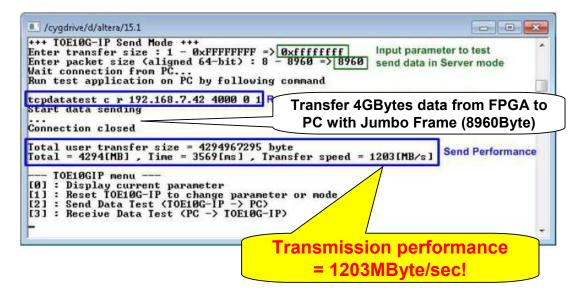

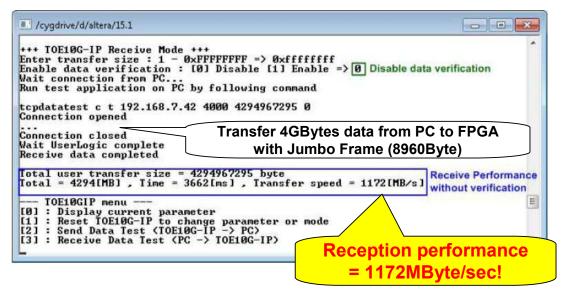

| Standard  | Тх          | Rx          | Full-Duplex     |

|-----------|-------------|-------------|-----------------|

| 10GBASE-R | 1219MByte/s | 1109MByte/s | 800-1000MByte/s |

| 10GBASE-T | 1205MByte/s | 1103MByte/s | 800-1000MByte/s |

#### TOE10G-IP core performance test result

Condition: reference design between PC and A10GX board

Packet size: 8960byte (Jumbo Frame)

Use "ASF-10G-T" from 10GTek for 10GBASE-T environment test

PC specification: CPU Inteli5-8500@3.00GHz, DDR4 16GB, Windows10Pro, NIC card: X550-T1(Intel) \* Performance result varies in the range of 800-1000MB/s with each trial for full-duplex test

## TOE10G-IP core standalone resource usage

### – Condition = Maximum buffer setting

(TxDataBuf=RxDataBuf=64KB, TxPacketBuf=16KB)

| Family        | Example Device         | Fmax<br>(MHz) | ALMs <sup>1</sup> | Registers <sup>1</sup> | Pin   | Block Memory bit <sup>2</sup> | Design<br>Tools |

|---------------|------------------------|---------------|-------------------|------------------------|-------|-------------------------------|-----------------|

| Arria 10 SX   | 10AS066N3F40E2SGE2     | 156.25        | 2,566             | 3,931                  | -     | 1,179,648                     | QuartusII16.0   |

| Arria 10 GX   | 10AX115S2F45I2SG       | 156.25        | 2,453             | 3,491                  |       | 1,179,648                     | QuartusII16.0   |

| Cyclone 10 GX | 10CX220Y7F80E5G        | 156.25        | 2,247             | 3,446                  | -     | 1,179,648                     | QuartusII18.0   |

| Stratix 10 GX | 1SG280HU2F50E2VGS1     | 156.25        | 2,928             | 3,523                  |       | 1,179,648                     | QuartusII18.0   |

|               | ING-IP CORD eta        | naalo         | na con            | nniistinn              | rocul | T /                           |                 |

| TUE           | <u>10G-IP core sta</u> | indalo        |                   | ipilation              |       |                               |                 |

19 February 2021

Design Gateway

Page 25

# **Transmission Performance**

Transmission (FPGA to PC) performance result using Arria10SoC Bd.

## **Reception Performance**

### Reception (PC to FPGA) performance result using Arria10SoC Bd.

19 February 2021

Design Gateway

Page 27

# **TOE10G-IP Application Market**

- Data transfer in FA market

- Medical video processing system

- Sensor data logger measurement instrument

- Storage system using TCP such as NAS, iSCSI

- TOE10G-IP replaces CPU for hard TCP processing

- Network product

- Network printer for high speed print data download

- Network camera for high speed video data upload

19 February 2021

Design Gateway

DGDESIGN

- Detailed documents available on the web site.

- http://www.dgway.com/TOE10G-IP\_A\_E.html

- Contact

- Design Gateway Co,. Ltd.

- E-mail : ip-sales@design-gateway.com

- FAX : +66-2-261-2290

19 February 2021

Of Real Property lies

## **Revision History**

| Rev. | Date              | Description                                                      |

|------|-------------------|------------------------------------------------------------------|

| 1.0E | August 1, 2016    | English version initial release                                  |

| 1.1E | February 8, 2017  | Added multiple sessions design for server application reference  |

| 1.2E | February 19, 2021 | Added 10GBASE-T support and A10GX,C10GX,S10GX family information |

|      |                   |                                                                  |

|      |                   |                                                                  |

|      |                   |                                                                  |

|      |                   |                                                                  |

|      |                   |                                                                  |

|      |                   |                                                                  |

|      |                   |                                                                  |

|      |                   |                                                                  |

|      |                   |                                                                  |

|      |                   |                                                                  |

|      |                   |                                                                  |