# TOE10G-IP 同時送受信デモ手順書(Altera 版)

Rev1.1J 2017/01/11

このドキュメントは TOE10G-IP コアを実装した Altera 製 FPGA 評価ボード(Arria10SoC 開発キット)を 10Gbit イーサネットで通信し、高速送信・受信を同時に行う全二重通信のコア実機動作を評価する具体的な手順を示したものです。本デモはジャンボ・フレームに対応した PC 環境のみで評価が可能です。送信あるいは受信の半二重通信機能を検証する標準デモについては別途 TOE10G-IP 標準デモ手順書(ファイル名:dg\_toe10gip\_instruction\_altera\_jp.pdf)を参照してください。

### 1 動作環境

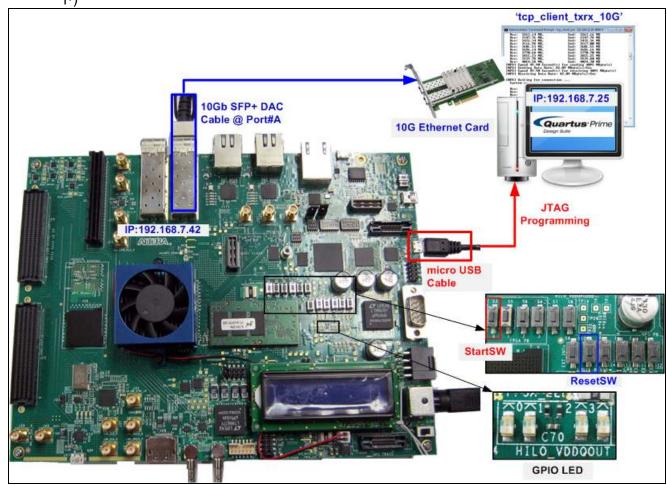

TOE10G-IP 同時送受信デモを実施するためには図 1-1 に示すように以下の部材を用意してください。なお、PC 側で実行するテスト・アプリケーション以外は TOE10G-IP 標準デモ(半二重通信デモ)の環境と同一です。

- 1) Altera 製 FPGA ボード (Arria10 SoC 開発キット)

- 2) 10Gbit イーサネットのポートを持つか、または 10 ギガビット・イーサネット・カードを装着した Windows PC

- 3) FPGA 開発ボードと PC 間を接続する 10Gbit SFP+光トランシーバおよび光ケーブル、または SFP+ダイレクト・アタッチ・ケーブル

- 4) FPGA ボード付属の JTAG 接続用 micro USB ケーブル

- 5) PC の Dos ウインドウで動作する"tcp\_client\_txrx\_10G.exe" (DesignGateway 社 Web ページからダウンロード)

図 1-1: Arria10SoC ボードでの TOE10G-IP 同時送受信デモ環境

注意: 本ドキュメントで例示された実機動作結果は以下のテスト環境にて実測されたものです。

[1] 10G ネットワーク・アダプタ: Intel X520-DA2

http://ark.intel.com/ja/products/39776/Intel-Ethernet-Converged-Network-Adapter-X520-DA2

[2] 10Gbit SFP+ ダイレクト・アタッチ・ケーブル (ケーブル長 1m)

http://www.netgear.com/business/products/switches/modules-accessories/axc761.aspx

[3] PC 仕様: マザボード ASUS H87M-E, メインメモリ 32 GB, 64-bit Windows7 OS

### 2 同時送受信デモの説明

本デモにおける FPGA の TOE10G-IP コアの検証用ロジックは入力と出力を接続したループバック接続となります。このため PC 側テスト・アプリケーションから送信されたデータは全てテスト・アプリケーションに戻され受信データをベリファイできます。 TCP コネクションは PC からオープンされます、つまり PC は TCP クライアントとして動作し FPGA は TCP サーバーとして動作します。

デモの状態は 4 ビットの LED (D25~D28)で図 2-1 のように表示されます。それぞれの LED の定義を表 2-1 に説明します。なお、標準デモと異なり DIP スイッチは使用しません。

図 2-1: 状態表示 LED(D25~D28)

図 2-2: スタート SW(S3)とリセット SW(S10)の位置

| FPGA<br>LED | ON/BLINK            | OFF                                                                       |

|-------------|---------------------|---------------------------------------------------------------------------|

| 0           | IPコアの初期化完了          | IPコアの初期化が未完了<br>スタート SW(S3)を押したことや、PC 側の IP アドレスが正しく<br>設定されているかを確認してください |

| 1           | LED 点滅:動作タイムアウト     | エラー無し、正常動作                                                                |

| 2           | (未使用)               | (未使用)                                                                     |

| 3           | LED ON:ポートのオープンを確立. | アイドル中(ポートはクローズ状態)                                                         |

表 2-1: LED 定義

## 3 デモ実施方法

#### 3.1 FPGAのプログラム

本同時送受信デモを実施するには以下の手順に従ってください。

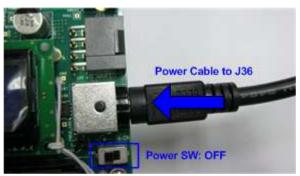

- FPGA ボード付属のマイクロ USB ケーブルを FPGA ボードと PC 間に接続し、 FPGA ボードの電源ケーブルも接続します。

図 3-1: マイクロ USB ケーブルの接続

図 3-2: 電源ケーブルの接続

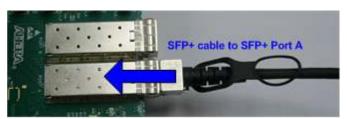

- 10Gbit SFP+ DAC(ダイレクト・アタッチ・ケーブル)または SFP+光トランシーバ&光ケーブルを SFP+のポート A と PC 間に接続します。

図 3-3: SFP+ケーブルの接続

- PC のネットワーク設定を TOE10G-IP 標準デモ手順書(Altera 版)の第3章に説明したようにセットします。

- FPGAボードの電源を投入します。

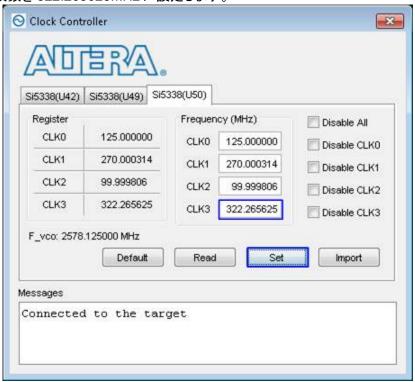

- Arria10SoC 開発キット内の"Clock Controller"アプリケーションを起動します。 図 3-4 に示すように Si5338(U50)タブを選択し、CLK3 の周波数値を"322.265625"MHz にセットします。"Set"ボタンを押下し発振クロック周波数を 322.265625MHz に設定します。

図 3-4: リファレンス・クロックの設

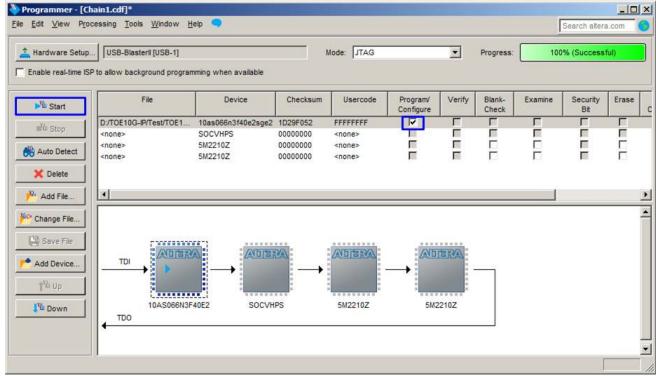

Quartus プログラマを起動し、デモ用の SOF ファイルを選択して図 3-5 のようにコンフィグレーションします。

図 3-5: SOF ファイルのコンフィグレーション

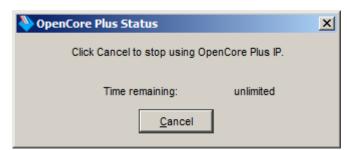

- リファレンス・デザインでは Altera から提供された 10G EMAC の評価用 IP コアを使っているため、図 4-6 のように 10G EMAC が評価用であることを示す注意メッセージが表示されます。 リファレンス・デザインではコンフィグレーション完了後大体 20 分程度の実機動作が可能なようです。 (Cancel ボタンを押すと直ちに動作が停止してしまうので動作中はこのボタンを押さないでください。)

図 3-6: OpenCore Plus IP の注意メッセージ

- 図 2-2 で図示していますが S3 位置のスタート SW を押下してシステムの初期化を実行します。 そして図 3-7 に示すように LED0 が点灯することを確認してください。

図 3-7: スタート SW 押下後の LED 状態

これでデモ・システムにてデータ同時送受信テストの準備が完了しました、テストの具体的な手順については次の章で説明します。

<u>ご注意</u>: 実機デモにおける転送パフォーマンスはテストPC のパフォーマンスに依存するため、10Gbit イーサネットの送受信を実行するに十分な能力を備えたPC を用意する必要があります。

#### 3.2 テスト・アプリケーションの起動

テスト・アプリケーションは同時に32Gバイト・データを送信/受信します。FPGAが全32Gバイト・データを受信しその全受信データをPCへ送信した後、ポートをクローズします。テスト・アプリケーションはこの動作を永遠に繰り返すデザインとなります。クローズした後、テスト・アプリケーションはテストを再実行するため新たなコネクションをオープンします。ユーザはテストを停止するためキャンセルを指示する必要があります。

本デモには2つの動作モードがあります、ひとつはパフォーマンス・テスト・モードでもうひとつはベリファイ・モードです。 その両モードの違いとしてテスト・アプリケーション内で有意なデータを生成するかダミーの同一データを生成するかの違いとなります。 FPGA 内部でのハードウエア動作は両モードで完全に同一です、それは PCからの受信データをそのまま PC へ送り返すデザインとなっているためです。

パフォーマンス・テスト・モードでは PC は常にオール・ゼロのデータを発生し、またアプリケーションのタスク負荷を削減するため FPGA からの返送データはベリファイしません。 つまりこのモードでは 10G ビット・イーサネットで最高のパフォーマンスが達成できます。

一方ベリファイ・モードにおいてはテスト・アプリケーションでは 32 ビットのインクリメンタル・データを生成し、また受信データは送信した期待データと一致するかのベリファイを実行します。このモードでは PC での CPU 時間をより消費するため転送パフォーマンスは低下します。このモードはネットワークのデータ信頼性を確認するために使われます。より詳細については以下に説明します。

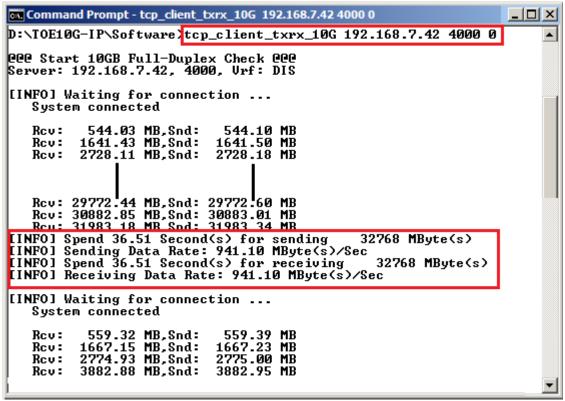

#### 3.2.1 パフォーマンス・テスト・モード

- PC の DOS 窓(コマンド・プロンプト)を開き"tcp\_client\_txrx\_10G"を実行します。 この DOS アプリケーション のコマンドラインは以下のフォーマットとなります。

- >> tcp\_client\_txrx\_10G <FPGA 側 IP アドレス> <ポート番号> <モード>

- 本デモは IP アドレスとポート番号は HDL コードを編集し再コンパイルしない限り変更できません。

- モード: '0'-オール・ゼロパターンを送信し受信時のベリファイは行いません。

- 本デモでは以下のコマンドラインとしてください。tcp\_client\_txrx\_10G 192.168.7.42 4000 0

- テスト・アプリケーションは現在の転送データ数を 1 秒毎に表示します。また下図 3-8 のように各ループの最後に所要時間とパフォーマンスが表示されます。

- テストを終了(キャンセル)しアイドル状態に戻すためには、"Ctrl + C"キーを押してください。

図 3-8: パフォーマンス・テスト・モードの実行表示例

図 3-9: パフォーマンス・テスト・モード実行時の LED 状態

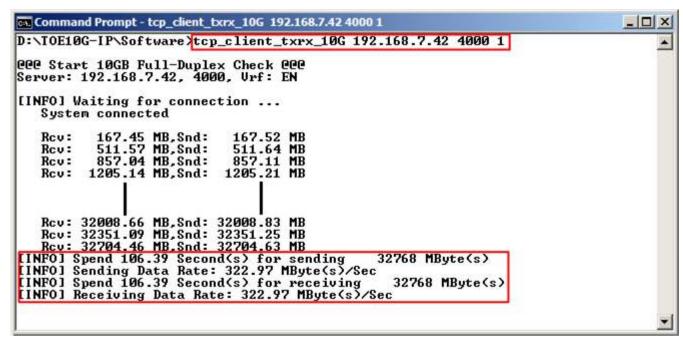

#### 3.2.2 ベリファイ・モード

- PC の DOS 窓(コマンド・プロンプト)を開き"tcp\_client\_txrx\_10G"を以下の引数で実行します。 >> tcp\_client\_txrx\_10G <FPGA 側 IP アドレス> <ポート番号> <モード>

- 本デモは IP アドレスとポート番号は HDL コードを編集し再コンパイルしない限り変更できません。

- モード: '1-32 ビットのインクリメンタル・パターンを送信し受信時にベリファイを行います。

- 本デモでは以下のコマンドラインとしてください。 tcp\_client\_txrx\_10G 192.168.7.42 4000 1

- テスト・アプリケーションは現在の転送データ数を 1 秒毎に表示します。また下図 3-10 うに各ループの最後に所要時間とパフォーマンスが表示されます。

- テストを終了(キャンセル)しアイドル状態に戻すためには、"Ctrl + C"キーを押してください。

図 3-10: ベリファイ・モードの実行表示例

# 4 更新履歴

| リビジョン | 日付         | 内容                      |

|-------|------------|-------------------------|

| 1.0   | 23-May-16  | Initial version release |

| 1.0J  | 2016/10/18 | 日本語版の初版発行               |

| 1.1J  | 2017/01/11 | 図1の更新                   |