# USB3.0 (Device) IP Protocol & Link Layer Core

13-May-2015

**Product Specification**

Rev 1.4E

#### Design Gateway Co.,Ltd

54 BB Building 13th Fl., Room No.1302 Sukhumvit 21 Rd. (Asoke), Klongtoey-Nua, Wattana, Bangkok 10110, Thailand Phone: (+66) 02-261-2277 Fax: (+66) 02-261-2290 E-mail: sales@design-gateway.com URL: www.design-gateway.com

| Core Facts              |                                |  |  |  |  |  |  |  |

|-------------------------|--------------------------------|--|--|--|--|--|--|--|

| Provided with Core      |                                |  |  |  |  |  |  |  |

| Documentation           | Reference design manual        |  |  |  |  |  |  |  |

| Design File Formats     | Encrypted hdl File             |  |  |  |  |  |  |  |

| Instantiation Templates | VHDL                           |  |  |  |  |  |  |  |

| Reference Designs &     | QuartusII Project,             |  |  |  |  |  |  |  |

| Application Notes       | See Reference Design Manual    |  |  |  |  |  |  |  |

| Additional Items        | Demo on Altera Development Kit |  |  |  |  |  |  |  |

|                         | (Requires AB08-USB3HSMC)       |  |  |  |  |  |  |  |

| Support                 |                                |  |  |  |  |  |  |  |

| Support Provided by De  | sign Gateway Co., Ltd.         |  |  |  |  |  |  |  |

### **Features**

- Compliant with the USB 3.0 specification revision 1.0

- USB3.0 Device Contoroller

- Imprement link layer and protocol layer

- Physical layer interfaces to PHY chip by TI (TUSB1310A)

- IP core clocks are adjustable (250MHz for PIPE I/F, more than 125MHz for internal)

- Support 16bit PIPE interface

- Support IN/OUT end point up to 15 points

- 1 point for control

- 7 points each for IN/OUT

- Support All transmission taps (Control, Bulk, Isochronous and Interruput transmission)

- Simple transaction interface with Host processor or DMA interface

- Free demo SOF file for evaluation on Altera board.

- Reference design available on CyclonelV GX, CycloneVE, ArriaV GX Development Kit with Design GateWay AB08-USB3HSMC Card

| Family       | Example Device  | Fmax<br>(MHz) | Combinational<br>ALUTs <sup>1</sup> /<br>Logic Elements | Registers <sup>1</sup> | Pin² | Block Memori<br>bit | PLL | Design<br>Tools |

|--------------|-----------------|---------------|---------------------------------------------------------|------------------------|------|---------------------|-----|-----------------|

| CycloneIV GX | EP4CGX150DF31C7 | 135           | 8,910                                                   | 3,864                  | 68   | 135,168             | 2   | QuartusII 13.1  |

| Arria II GX  | EP2AGX125EF35C4 | 149           | 5,793                                                   | 3,864                  | 68   | 135,168             | 2   | QuartusII 10.1  |

| CycloneV E   | 5CEFA7F31I7     | 140           | 5,907                                                   | 4,389                  | 68   | 135,168             | 2   | QuartusII 14.0  |

| ArriaV GX    | 5AGXFB3H4F35C4  | 138           | 5,905                                                   | 4,266                  | 68   | 135,168             | 2   | QuartusII 14.0  |

### Table 1: Example Implementation Statistics (Control x1, IN x2, OUT x2)

Notes:

1) Actual logic count dependent on percentage of unrelated logic.

2) Assuming all core I/Os, I/Os for TI\_PHY and clocks are routed off-chip and internal signals are enclosed by FF.

3) The number of end port of the core is variable. In case of Bulk transmission, FIFO size can be reduced to one.

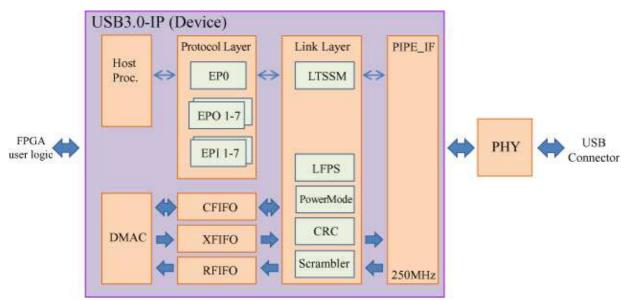

\* LTSSM: Link Training and Status State Machine, LFPS : Low Frequency Periodic Signaling

Figure 1: USB3.0 (Device) IP Block Diagram

# **Applications**

USB3.0 (Device) IP Core is ideal for use in a USB3.0 supported device system which require high bandwidth up to 5.0Gbps. This IP Core will process almost all USB3.0 protocols (some part of chapter 6, chapter 7 and 8 of the USB3.0 specification) by hardware. It achieves processing by low-end CPU. By setting parameter, this IP Core flexibly supports both a device achieved by minimum end point such as mass storage class and a high-end device which need multiple end points. This IP Core is optimized for saving FPGA internal logic resource by eliminating legacy USB protocol of USB2.0 (480Mbps) or earlier, so that it provides most cost-effective solution for 5Gbps super speed implementation.

# **General Description**

The USB3.0 (Device) IP Core implements link layer and protocol layer. Only setting data address on memory prepared by Host processor, transmission length and other parameter to the register in the IP Core, IP Core will process dividing into packets, adding CRC & Scramble and flow control on USB bus, and return processing result to the register. Data receive process is also same flow.

Host interface of the IP Core consist of simple register access interface, provide simple DMA access interface for memory and able to connect to NIOS II processor or ALTMEMDDR easily.

For connection with PHY chip, it is compliant with standard PIPE interface. So it is just able to connect through Flip-Flop for timing adjustment with FPGA port.

Internal clock in the IP Core is more than 125MHz (125M x 4bytes = 500MB/s) and clock for connection with PHY chip is fixed to 250MHz (500MHz x 2 bytes). However Host interface and DMA interface are able to connect by low frequency clock after synchronization.

# **Functional Description**

The USB3.0 (Device) IP Core is structured by 3 blocks.

#### Protocol Layer

Protocol Layer manages data on memory assigned by register from Host processor, and divides to USB3.0 packet and sends to Link layer. Receiving is opposite process. This layer manages End-to-End sequence number with host (host bus adaptor auch as PC) and credit process.

- EP0(End point 0)

Process control transmession specified by USB3.0.

It includes setup packet receiving, data transmission for control (In/Out) and status transmission.

- EPO(End point Out 1~7) Process BULK-OUT transmission, INTERRUPT-OUT transmission and ISOCHRONOUS-OUT transmission.

- EPI(End point In 1~7) Process BULK-IN transmission, INTERRUPT- IN transmission and ISOCHRONOUS-IN transmission.

#### • MPP(Multi-purpose point)

It is used for transmission/receiving process of Port-Capabilities / Port-Configuration/Response after changing to U0 status and used for transmission/receiving process of Isochronous Time Stamp(ITS) and Link Management Packet(LMP).

• FIFO

CFIFO is data sending/receiving FIFO for EP0. XFIFO is data transmission FIFO (up to 2pcs/automatic assignment) which is shared at EPI. RFIFO is data receiving FIFO (up to 2pcs/automatic assignment) which is shared at EPO.

### • DMAC, Arbiters

DMA request from each end points and packet send/receive request are adjusted and sequencially processed in Protocol Layer.

#### Link Layer

Link Layer adds CRC (CRC-5 or16 or 32) to packet from Protocol Layer, scrambles it and send it with 8B(x4) symbol to PIPE\_IF. Sending and receiving between links and flow management are also processed by this layer.

LTSSM block

Manage link status specified by USB3.0, initialize and do sequential processing of power status.

FLOW block

Flow control between links. Manage transmission status (normal or abnormal), retry and credit process between links.

LFPS block

Send and receive LFPS(Low Frequecncy Periodic Signaling) when initialization or returning from power mode.

Power Mode block

Process send / receive Link Command when switching to power mode.

Transmission/Receiving process block

Add/check CRC, add/cancel scramble and add/check Link Control word.

#### **PIPE Interface**

PIPE interface sends/receives data and signal from/to Link Layer to/from PHY, synchronized with PIPE clock.

### Transmission block

It converts 8B(x4) symbol to 8B(x2) symbol, executes Elastic process for the symbol and adds SKIP order set. (In case that internal is 125MHz operation, transceiver side also need Elastic procass because of frequency differential with PHY clock.)

Receiving block

It is reverse process of Transmission block.

Control block

Send necessary signal synchronized with PIPE clock, according to state transition of LinkLayer. And It sends signal from PHY to Link Layer synchronized with internal clock.

### **FPGA Controller**

Normally host processor which executes application software is used as FPGA internal controller, and it manages control which is upper than USB device framework (Specification chapter 9 and after) by register access of USB 3.0 Device IP Core. System controller consists of Host processor, DMA interface, memory and so on.

### USB3.0 PHY

Use external chip supported USB3.0, such as TUSB1310A by TI which has PIPE\_IF.

# Core I/O Signals

Core I/O signals are not fixed with specified device and any pins to able to connect to user logic flexibly.All core I/O signals are shown as following table 2. Logic of these signals are active high if no specified.

### Table 2: Core I/O Signals.

| Signal         | Signa<br>Directi        | Description                                                                                  |  |  |  |  |  |  |  |  |

|----------------|-------------------------|----------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

|                | Common Interface Signal |                                                                                              |  |  |  |  |  |  |  |  |

| RST_N          | In                      | Reset USB3.0 (device) IP core. Active low.                                                   |  |  |  |  |  |  |  |  |

| CLK            | In                      | IP Core operating frequency output (125MHz).                                                 |  |  |  |  |  |  |  |  |

| PCLK           | In                      | PIPE clock (250MHz).                                                                         |  |  |  |  |  |  |  |  |

|                |                         | Input same frequency (phase is able to adjust by DCM) with PIPE clock generated by PHY chip. |  |  |  |  |  |  |  |  |

|                |                         | Able to switch to the constant operating clocks (such as CLK) during PCLK stop.              |  |  |  |  |  |  |  |  |

| I_EPO_ENB[7:1] | In                      | Define implementation/un-implementation of End Point Out(EPO).                               |  |  |  |  |  |  |  |  |

|                |                         | Able to implement up to 7 points. [1] EPO1, [7] EPO7. 1=Implement                            |  |  |  |  |  |  |  |  |

| I_EPI_ENB[7:1] | In                      | Define implementation/un-implementation of End Point In(EPI).                                |  |  |  |  |  |  |  |  |

|                |                         | Able to implement up to 7 points. [1] EPI1, [7] EPI7. 1=Implement                            |  |  |  |  |  |  |  |  |

| Signal             | Signal<br>Direction   |                                                              | Description                                                                             |  |  |  |  |  |

|--------------------|-----------------------|--------------------------------------------------------------|-----------------------------------------------------------------------------------------|--|--|--|--|--|

|                    | PIPE Interface Signal |                                                              |                                                                                         |  |  |  |  |  |

| O_PIPE_READY       | Out                   | PIPE                                                         | clock (PCLK) is operating.                                                              |  |  |  |  |  |

|                    |                       | After                                                        | changing to other state except P3, detect rising of I_PHY_STATUS_ASYN and assert.       |  |  |  |  |  |

| O_RX_TERMINATION   | Out                   | Cont                                                         | rol RX termination existence (yes or no). 1 = yes, 0 = no.                              |  |  |  |  |  |

|                    |                       | Char                                                         | ge asynchronizing with PCLK (change even though during PCLK stop)                       |  |  |  |  |  |

| O_TX_DETRX_ASYN    | Out                   | Cont                                                         | rol detecting RX termination existence of opposite side.                                |  |  |  |  |  |

|                    |                       | Char                                                         | ge asynchronizing with PCLK, Use it at near P3 state(O_PIPE_READY negate).              |  |  |  |  |  |

| O_TX_EIDLE_ASYN    | Out                   | Cont                                                         | rol TX signal(SSTXP/SSTXN) to electrical idle state.                                    |  |  |  |  |  |

|                    |                       | Char                                                         | nge asynchronizing with PCLK, Use it at near P3 state(O_PIPE_READY negate).             |  |  |  |  |  |

| O_PWR_DOWN_ASYN[   | Out                   | Cont                                                         | rol power state of PHY. 00:P0, 01:P2, 10:P3, 11:P3                                      |  |  |  |  |  |

| 1:0]               |                       | Char                                                         | nge asynchronizing with PCLK, Use it at near P3 state(O_PIPE_READY negate).             |  |  |  |  |  |

| O_TX_DETRX_LPBK    | Out                   | Control detecting RX termination existence of opposite side. |                                                                                         |  |  |  |  |  |

|                    |                       | Char                                                         | nge synchronizing with PCLK, Use it at except near P3 state(O_PIPE_READY assert).       |  |  |  |  |  |

| O_TX_ELECIDLE      | Out                   | Control TX signal(SSTXP/SSTXN) to electrical idle state.     |                                                                                         |  |  |  |  |  |

|                    |                       | Char                                                         | nge synchronizing with PCLK, Use it at except near P3 state(O_PIPE_READY assert).       |  |  |  |  |  |

| O_POWER_DOWN [1:0] | Out                   | Cont                                                         | rol power state of PHY. 00:P0, 01:P2, 10:P3, 11:P3                                      |  |  |  |  |  |

|                    |                       | Char                                                         | nge synchronizing with PCLK, Use it at except near P3 state(O_PIPE_READY assert).       |  |  |  |  |  |

| I_PWRPRESENT       | In                    | Input                                                        | the state of power supplying to VBUS. Asynchronizing with PCLK.                         |  |  |  |  |  |

| I_RX_ELECIDLE      | In                    | Input                                                        | electrical idle state of RX signal (SSRXP/SSRXN). Asynchronizing with PCLK.             |  |  |  |  |  |

| I_PHY_STATUS_ASYN  | In                    | Input                                                        | the signal which control to input PHY status. Asynchronizing with PCLK.                 |  |  |  |  |  |

|                    |                       | After                                                        | changing from P3 state, it is used for detecting PCLK operation start.                  |  |  |  |  |  |

| I_RX_STATUS011_ASY | In Inpu               |                                                              | detected result of RX termination existence of opposite side. Asynchronizing with PCLK. |  |  |  |  |  |

| Ν                  | 1                     |                                                              | es.                                                                                     |  |  |  |  |  |

| I_PHY_STATUS       | In                    | Input                                                        | Input the signal which control to input PHY status.Synchronizing with PCLK.             |  |  |  |  |  |

|                    |                       | Durir                                                        | ng O_PIPE_READY is asserted, it displays detecting completion of RX terminal existence. |  |  |  |  |  |

| I_RX_STATUS011     | In                    | Input                                                        | detected result of RX termination existence of opposite side.Synchronizing with PCLK.   |  |  |  |  |  |

|                    |                       | Valid                                                        | when I_PHY_STATUS = 1. 1=yes.                                                           |  |  |  |  |  |

13-May-2015

#### USB3.0 IP Device side Prototol and Link layer Core

| O_TX_DATAK[1:0] | Out | TX symbol (8B code). K code (1) or D code (0). Synchronizing with PCLK.  |

|-----------------|-----|--------------------------------------------------------------------------|

| O_TX_DATA[15:0] | Out | Twice of TX symbol (8B code). Synchronizing with PCLK.                   |

| I_RX_VALID      | In  | The timing which RX symbol is valid. 1 = valid. Synchronizing with PCLK. |

| I_RX_DATAK[1:0] | In  | RXsymbol (8B code). K code (1) or D code (0). Synchronizing with PCLK.   |

| I_RX_DATA[15:0] | In  | Twice of RX symbol (8B code). Synchronizing with PCLK.                   |

| Signal              | Signal Signa<br>Directio       |                                                                                             | Description                                                                                    |  |  |  |  |  |

|---------------------|--------------------------------|---------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|--|--|--|--|--|

|                     | Host Register Interface Signal |                                                                                             |                                                                                                |  |  |  |  |  |

| I_LINK_REG_RE[15:0] | In                             | Rea                                                                                         | d signal of control register of link layer.                                                    |  |  |  |  |  |

|                     |                                | Not                                                                                         | all 16 lines are implemented. 1 line is 4bytes. Assert 1 cycle synchronized with CLK.          |  |  |  |  |  |

| I_LINK_REG_WE[15:0] | In                             | Writ                                                                                        | e signal of control register of link layer.                                                    |  |  |  |  |  |

|                     |                                | Not                                                                                         | all 16 lines are implemented. 1 line is 4bytes. Assert 1 cycle synchronized with CLK.          |  |  |  |  |  |

| I_PRTE_REG_RE[15:0] | In                             | Rea                                                                                         | d signal of control register of protocol layer.                                                |  |  |  |  |  |

|                     |                                | Not                                                                                         | all 16 lines are implemented. 1 line is 4bytes. Assert 1 cycle synchronized with CLK.          |  |  |  |  |  |

| I_PRTE_REG_WE[15:0] | In                             | Writ                                                                                        | e signal of control register of protocol layer.                                                |  |  |  |  |  |

|                     |                                | Not                                                                                         | all 16 lines are implemented. 1 line is 4bytes. Assert 1 cycle synchronized with CLK.          |  |  |  |  |  |

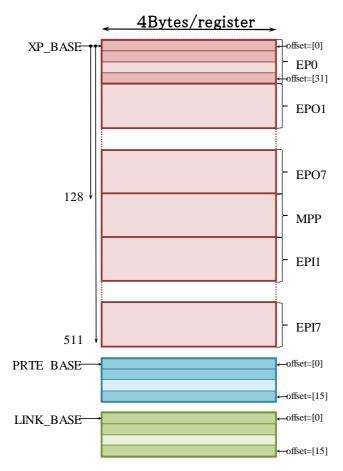

| I_XPP_REG_RE[511:0] | In                             | Rea                                                                                         | d signal of control register of each end point.                                                |  |  |  |  |  |

|                     |                                | Eac                                                                                         | h end point has 32 lines, however not all 32 lines are implemented. 1 line is 4bytes. Assert 1 |  |  |  |  |  |

|                     |                                | cycl                                                                                        | e synchronized with CLK.                                                                       |  |  |  |  |  |

| I_XPP_REG_WE[511:0] | In                             | Writ                                                                                        | e signal of control register of each end point.                                                |  |  |  |  |  |

|                     |                                | Eac                                                                                         | h end point has 32 lines, however not all 32 lines are implemented. 1 line is 4bytes. Assert 1 |  |  |  |  |  |

|                     |                                | cycl                                                                                        | e synchronized with CLK.                                                                       |  |  |  |  |  |

| O_EP_REG_RD[31:0]   | Out                            | Rea                                                                                         | d data of all control register. Valid at the next cycle when any _RE is asserted.              |  |  |  |  |  |

| I_EP_REG_WD0[31:0]  | In                             | Inpu                                                                                        | t write data to control register. Valid at the timing when any _WE is asserted.                |  |  |  |  |  |

| I_EP_REG_WD1[31:0]  | In                             | Inpu                                                                                        | t write data to control register. Valid at the timing when any _WE is asserted.                |  |  |  |  |  |

|                     |                                | In case of using EPI4~7, EPO4~7, you have to connect to the signal which is same logic with |                                                                                                |  |  |  |  |  |

|                     |                                | I_EF                                                                                        | P_REG_WD0. Connecting to different FF is better for load balancing.                            |  |  |  |  |  |

| O_EP_IRQ            | Out                            | Inter                                                                                       | rupt signal from USB core. 1= Interrupt. Level signal.                                         |  |  |  |  |  |

| O_EXT_CNTL [1:0]    | Out                            | USE                                                                                         | core external control signal.Control register of link layer can switch ON/OFF.                 |  |  |  |  |  |

| O_LANE_POL          | Out                            | RX I                                                                                        | ane Porarity Inversion. 1: Invert , 0: Not Invert.                                             |  |  |  |  |  |

| I_USB20_RESET       | In                             | Inpu                                                                                        | t reset from USB2.0. 1 = reset. In case of no USB2.0 core, fix to 0.                           |  |  |  |  |  |

| Signal              | Signa<br>Directi | Description                                                                                       |  |  |

|---------------------|------------------|---------------------------------------------------------------------------------------------------|--|--|

|                     |                  | DMA Access Interface Signal                                                                       |  |  |

| I_DMAC_IDLE         | In               | Next DMA access start enables.                                                                    |  |  |

| O_DMAC_REQ          | Out              | DMA access start. Synchronize with CLK. Assert for 1cycle.                                        |  |  |

| O_DMAC_ADR [31:0]   | Out              | DMA start address. Valid at O_DMAC_REQ asserted.                                                  |  |  |

| O_DMAC_U2M          | Out              | DMA direction. Valid at O_DMAC_REQ asserted.                                                      |  |  |

|                     |                  | 0: Memory to USB, 1: USB to Memory.                                                               |  |  |

| O_DMAC_LEN[8:0] Out |                  | DMA length. Valid at O_DMAC_REQ asserted.                                                         |  |  |

|                     |                  | 0x100: 256words(4K bytes), 0x001: 1word(4bytes)                                                   |  |  |

| O_DMAC_BE [3:0]     | Out              | Valid / Invalid of each bytes.                                                                    |  |  |

| O_DMAC_DONE         | Out              | Data transmission completed. Assert 1 cycle after several cycle after sending end data completed. |  |  |

| I_DMAC_M2U_VLD In   |                  | Valid timing of I_DMAC_M2U_DATA in case of DMA from Memory to USB.                                |  |  |

| [ I_DMAC_M2U_DATA[31<br>:0] or [63:0] | In  | Input data from memory in case of DMA from Memory to USB.<br>Data width can adjust by "DMA64_MODE" paramerter ot top module.<br>4(or 8) bytes transmission complete (no wait) in the timing I_DMAC_M2U_VLD=1'b1. |

|---------------------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I_DMAC_U2M_WAIT                       | In  | Timing which memory cannot accept data in case of DMA from USB to Memory.                                                                                                                                        |

| O_DMAC_U2M_OUT                        | Out | Valid timing of O_DMAC_U2M_DATA in case of DMA from USB to Memory.                                                                                                                                               |

| O_DMAC_U2M_DATA[3                     | Out | Output data to memory in case of DMA from USB to Memory.                                                                                                                                                         |

| 1:0] or [63:0]                        |     | Data width can adjust by "DMA64_MODE" paramerter ot top module                                                                                                                                                   |

|                                       |     | 4(or 8) bytes transmission complete in the timing O_DMAC_U2M_OUT=1'b1,                                                                                                                                           |

|                                       |     | I_DMAC_U2M_WAIT=1'b0                                                                                                                                                                                             |

# Notes of PIPE interface

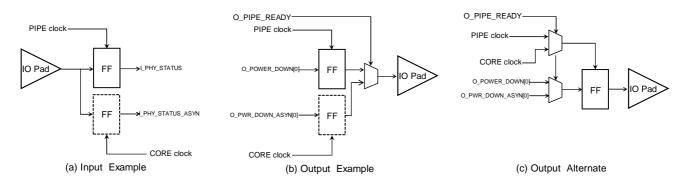

This is general PIPE interface, but must be careful to synchronous/asynchronous of signal when it connects with external PHY chip (see figure 2).

Input signals have signal which references at PIPE clock (PCLK) from PHY is stopping. These signals is direct to pin or the re-synchronized signal (with \_ASYN) by FF operated by core internal clock. In case that there is reference signal synchronized PIPE clock during PIPE clock is operating, it must be separate to 2 lines.

Some output signals are also changed even though PIPE clock (PCLK) is stopping. These signals is direct to pin or output with re-synchronized (with \_ASYN) by FF operated by core internal clock. In case that there is the output signal synchronized PIPE clock during PIPE clock is operating, multiplex in front of a pin or output by synchronized with FF operated by switching clock.

Figure 2: PIPE interface connection example

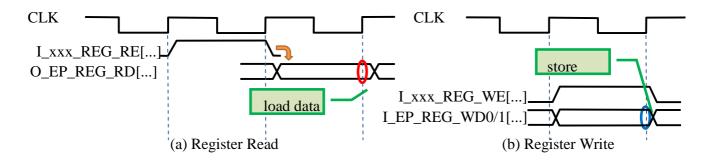

# **Timing Diagram of Host register interface**

Register access is shown at Figure 3. 1cycle asserting I\_xxx\_REG\_RE to output read value of the register to O\_EP\_REG\_RD. And write when write value is input to I\_EP\_REG\_WD with 1 cycle asserting I\_xxx\_REG\_WE.

Figure 3 : Signal waveform of host register interface

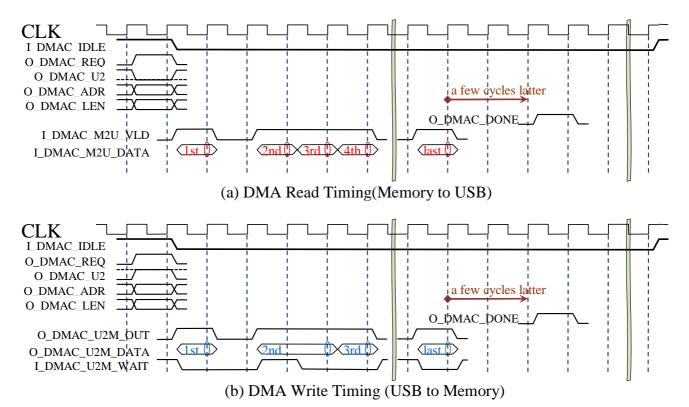

### **Timing Diagram of DMA access interface**

When I\_DMAC\_IDLE is asserted, O\_DMAC\_REQ is also asserted for 1 cycle as shown at Figure 4. In the same time, access address, direction and length are specified.

Data is transferred with flow control by VLD or WAIT signal depend on direction.

When the transmission completed and after several cycles, O\_DMAC\_DONE is asserted for 1 cycle then DMA access completed.

Figure 4 : Signal waveform of DMA access interface

# **IP Core control register**

IP Core Control register which Host processor can access are shown as following Table 4.

|       | gister                                                    | R/W   | Offset  | Description                                                                                      |  |  |  |  |  |

|-------|-----------------------------------------------------------|-------|---------|--------------------------------------------------------------------------------------------------|--|--|--|--|--|

|       | ame                                                       | • .   |         |                                                                                                  |  |  |  |  |  |

|       | Link Layer Register [ADDRESS=C_BASEADDR+LINK_BASE+OFFSET] |       |         |                                                                                                  |  |  |  |  |  |

| LINK_ | CNFG                                                      | R/W   | 0h      | Link Layer Configuration Register                                                                |  |  |  |  |  |

|       | USB_                                                      | VALID | [0]     | Enable USB bus (LTSSM) state transition except to SS_Disable (Operation enable state)            |  |  |  |  |  |

|       |                                                           | D_ENB | [1]     | Enable to receive Power Mode transition request from Host.                                       |  |  |  |  |  |

|       | SCR                                                       | B_DIS | [2]     | Disbale scramble. For debugging.                                                                 |  |  |  |  |  |

|       | EX                                                        | T_CNT | [5:4]   | ON/OFF O_EXT_CNTL [1:0] (refering I/O signal).                                                   |  |  |  |  |  |

|       | U2_INA                                                    | ACT_C | [15:8]  | Set the count time (U2_Inactive_timer) transiting from U1 to U2.                                 |  |  |  |  |  |

|       |                                                           | NT    |         | Value=Actual time/(USB_CLKx 0x10000)                                                             |  |  |  |  |  |

| LINK_ | CNTL                                                      | W     | 1h      | Link Layer Control Register. Instructed if "1" is written. Set 1-bit only(one-hot) at same time. |  |  |  |  |  |

|       |                                                           |       |         | No described bits should be written "0".                                                         |  |  |  |  |  |

|       | GO_F                                                      | RXDET | [0]     | Make USB bus state (LTSSM) transit from SS_Disable to Rx_Detect_Active (Operation start).        |  |  |  |  |  |

|       |                                                           |       |         | LINK_CNFG[USB_VALID] must be ON before.                                                          |  |  |  |  |  |

|       | GO_                                                       | RCOV  | [3]     | Transit from Active_U0 state to Recovery state.                                                  |  |  |  |  |  |

|       | GO_PM                                                     | D_NU  | [9:8]   | Set Power Mode level for transiting by GO_PMD. 01:U1, 10:U2, 11;U3                               |  |  |  |  |  |

|       | М                                                         |       |         |                                                                                                  |  |  |  |  |  |

|       | GC                                                        | _PMD  | [10]    | Request transition to Power Mode. Success or Not are depend on Host side status.                 |  |  |  |  |  |

|       | C                                                         | GO_U0 | [11]    | Order to return from Power Mode (Active_U1/U2/U3).                                               |  |  |  |  |  |

| LINK  | IRQE                                                      | R/W   | 2h      | Link Layer Interrupt Register.                                                                   |  |  |  |  |  |

|       |                                                           | IRQ   | [0]     | Interruption requesting. Read Only.                                                              |  |  |  |  |  |

|       |                                                           | ENB   | [1]     | When IRQ=1, Interrupt signal to external (referring O_EP_IRQ <sub>o</sub> I/O signal) is ON.     |  |  |  |  |  |

| LINK_ | LTSSM                                                     | R     | 3h      | Link Layer Status Register.                                                                      |  |  |  |  |  |

|       |                                                           | RCOV  | [6:0]   | The reason why Link Layer transit to Recovery state. Kept during LINK_LTSSM[7] is ON.            |  |  |  |  |  |

|       | IRQ FA                                                    | CTOR  | [15:7]  | Cause of Link Laver interruption. State of Link Laver is possible to change without command from |  |  |  |  |  |

|       |                                                           |       |         | CPU. When any bit is ON, LINK_IRQE[IRQ] is also ON. Clear by 1 write to the bit.                 |  |  |  |  |  |

|       | LTSSM                                                     |       | [28:24] | Current state of Link Layer. The states are compliant with USB3.0 specification.                 |  |  |  |  |  |

|       |                                                           |       |         | Code allocation, which is implementation specific, is not disclosed in here                      |  |  |  |  |  |

|       | DEV_AD                                                    | DR_OF | [30]    | USB device address is 0 (un-setting). The device address will be cleared by hardware when Link   |  |  |  |  |  |

|       |                                                           | F     |         | Layer status transits to SS_Disable,Rx_Detect_Reset.                                             |  |  |  |  |  |

|       | VBUS                                                      | S_OFF | [31]    | Current VBUS is OFF.                                                                             |  |  |  |  |  |

### Table 4: IP Core control register

|       | gister<br>ame | R/W     | Offset     | Description                                                                                                                                  |

|-------|---------------|---------|------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| Proto | ocol Lay      | er Regi | ster [ADDF | RESS=C_BASEADDR+PRTE_BASE+OFFSET]                                                                                                            |

| PRTE  | _CNFG         | R/W     | 0h         | Protocol Layer Configuration Register                                                                                                        |

|       | DE            | /_ADR   | [6:0]      | Set device address of USB bus. The device address will be cleared by hardware when Link Layer status transits to SS_Disable,Rx_Detect_Reset. |

| PRTE  | _CNTL         | W       | 1h         | Protocol control register. Instructed if "1" is written. Set 1-bit only(one-hot) at same time.<br>No described bits should be written "0"    |

|       | ARBT_F        | RESET   | [0]        | Arbiter reset of Protocol Layer. For debugging.                                                                                              |

| PRTE  | _IRQE         | R/W     | 2h         | Protocol Layer Interrupt Enable Register.                                                                                                    |

|      |      | EP0  | [0]     | Enable interruption from EP.                                                                         |

|------|------|------|---------|------------------------------------------------------------------------------------------------------|

|      |      | EPO  | [7:1]   | Enable interruption from EPO1~7. [17]: EPO1, [23]:EPO7                                               |

|      |      | MPP  | [16]    | Enable interruption from MPP.                                                                        |

|      |      | EPI  | [23:17] | Enable interruption from EPI1~7. [1]: EPI1, [7]:EPI7                                                 |

| PRTE | _IRQ | R    | 3h      | Protocol Layer interrupt Register.                                                                   |

|      |      | EP0  | [0]     | Under requesting interruption from EP. When applicable IRQE bit is 1, interrupt signal for external  |

|      |      |      |         | will be ON.                                                                                          |

|      |      | EPO  | [7:1]   | Under requesting interruption from EPO1~7. When applicable IRQE bit is 1, interrupt signal for       |

|      |      |      |         | external will be ON. [1]: EPO1, [7]:EPO7                                                             |

|      |      | MPP  | [16]    | Under requesting interruption from MPP. When applicable IRQE bit is 1, interrupt signal for external |

|      |      |      |         | will be ON.                                                                                          |

|      |      | EPI  | [23:17] | Under requesting interruption from EPI1~7. When applicable IRQE bit is 1, interrupt signal for       |

|      |      |      |         | external will be ON. [1]: EPI1, [7]:EPI7                                                             |

| DMA_ | BASE | R/W  | 4h      | DMA Base Register.                                                                                   |

|      |      | BASE | [31:28] | Upper bit of memory address for DMA.                                                                 |

|      | gister<br>ame                 | R/W   | Offset     | Description                                                                                        |

|------|-------------------------------|-------|------------|----------------------------------------------------------------------------------------------------|

| End  | End Point Zero (EP0) Register |       | ) Register | [ADDRESS=C_BASEADDR+XP_BASE+(0x80×0)+0x000+OFFSET]                                                 |

|      | CNFG                          | R/W   | 00h        | EP0 Configuration Register.                                                                        |

|      |                               | VALID | [0]        | EP operation enables. Even it is not enable, Setup Data will be received correctly, transit        |

|      |                               |       |            | to "SETUP_IP" state and INVALID is ON when receiving Setup DP packet.                              |

|      |                               |       |            | When clearing SETU_IP" state, WRDY packet will be received.                                        |

|      | AUTO_S                        | SETUP | [1]        | If this bit is ON,                                                                                 |

| -    |                               |       |            | Transit from SETUP without Software instruction and return SETUP acknowledge to Host.              |

|      | AUTO_F                        | RESUL | [2]        | If this bit is ON,                                                                                 |

|      |                               | Т     |            | Transit from RESULT without Software instruction and return to IDLE state.                         |

|      | AUTO_                         | STALL | [3]        | If this bit is ON,                                                                                 |

|      |                               | ED    |            | Transit from STALLED without Software instruction and return STALL acknowledge to Host.            |

| EP0_ | CNTL                          | R/W   | 01h        | EP0 control register. Show status and update all bits of [31:16].                                  |

|      |                               |       |            | Requesting interrupt if any bit in [13:0] is ON. [23:16] show detected events. [31:24] show        |

|      |                               |       |            | transitional events.                                                                               |

| EP0_ | CLR                           | W     | 02h        | EP0 control register clear. Clear applicable bit by 1 writing.                                     |

| EP0_ | SET                           | W     | 03h        | EP0 control register set. Set applicable bit by 1 writing.                                         |

|      | R                             | ESULT | [0]        | RESULT state. When clearing it, final ACK packet will be received. And then return to IDLE.        |

|      |                               |       |            | When STALL is ON, STALL packet will be returned. When VALID is OFF, NRDY packet will be            |

|      |                               |       |            | returned.                                                                                          |

|      | S                             | SETUP | [1]        | SETUP in progress state. Setup DP packet is received. SETUP0/1 register store 8 bytes contents.    |

|      |                               |       |            | ACK packet (NumP=1) will be returned when clearing.                                                |

|      |                               |       |            | However, when RETRY is ON (Setup DP packet receiving error), retry is attached. When INVALID       |

|      |                               |       |            | is ON (VALID reference), NumP=0 will be returned. After that, it will transit to specified state   |

|      |                               |       | 101        | following INRDY/OUTRDY etc.                                                                        |

|      |                               | ALLED | [8]        | STALLED state. STALL packet will be returned when clear.                                           |

|      | DEFFERED [9]                  |       | [9]        | DEFFERED state. Transit to this state when the packet attaching Deffered bit is received. ERDY     |

|      |                               |       | [40]       | packet will be returned and transit to specified state when clearing.                              |

|      |                               | WRDY  | [10]       | WRDY state. (waiting ERDY) After sending NRDY packet etc. (flow state), become to the status.      |

|      | \A/A ! <del>T</del>           |       | [4 4]      | ERDY packet will be returned and transit to specified state when clearing.                         |

|      |                               |       | [14]       | Waiting for any packet. Valid when BUSY is ON.                                                     |

|      |                               | BUSY  | [15]       | It is ON except (IDLE state or [13:0] state). When WAIT_RECV is ON, Clearing this bit to return to |

### USB3.0 IP Device side Prototol and Link layer Core

|           |       |        | IDLE. And return to IDLE state when both this bit and [14] are cleared at same time. |

|-----------|-------|--------|--------------------------------------------------------------------------------------|

|           | STALL | [16]   | STALL packet is received or some abnormal is detected.                               |

|           | OVER  | [17]   | Traffic of Host is larger than specified in EP0_DLEN. (Device side is fewer.)        |

| U         | NDER  | [18]   | Traffic of Host is fewer than specified in EP0_DLE. (Device side is more.)           |

| SEND_S    | STALL | [19]   | Send STALL at STALLED state automatically if AUTO_STALLED is enable.                 |

| R         | ETRY  | [24]   | Error exists in received DP packet (include SetupDP packet).                         |

| IN        | VALID | [25]   | Receive Setup DP packet when VALID is OFF.                                           |

|           | NRDY  | [27]   | Send NRDY from RESULT state.                                                         |

| EP0_DLEN  | R/W   | 04h    | EP0 data length setting register.                                                    |

|           | DLEN  | [20:0] | Data length.                                                                         |

|           | EOB   | [29]   | Add EOB (End Of Burst) bit to end of packet when IN transmission.                    |

| OU        | TRDY  | [30]   | OUT transmission (from Host to Device) ready.                                        |

| I         | NRDY  | [31]   | IN transmission (from Device to Host) ready.                                         |

| EP0_PLEN  | R     | 05h    | EP0 data length result register                                                      |

|           | PLEN  | [20:0] | Length of actual transferred data.                                                   |

| OU        | TRDY  | [30]   | OUT transmission (from Host to Device) ready.(copy of DLEN register)                 |

|           | NRDY  | [31]   | IN transmission (from Device to Host) ready.(copy of DLEN register)                  |

| EP0_BFFR  | R/W   | 06h    | EP0 data length buffer (memory address) register                                     |

| B         | ADDR  | [27:8] | Start address of the memory for data input/output.                                   |

| EP0_SEQN  | R/W   | 07h    | EP0 sequence number register                                                         |

|           | SEQN  | [4:0]  | Current sequence number of packet. Writable, but normally no need.                   |

| EP0_SETUS | R/W   | 09h    | EP0 setup data register 0                                                            |

| 0         |       |        |                                                                                      |

|           |       |        |                                                                                      |

| EP0_SETUS | R/W   | 0Ah    | EP0 setup data register 1                                                            |

| EP0_SETUS | R/W   | 0Ah    | EPU setup data register 1                                                            |

| Re   | gister   | R/W     | Offset     | Description                                                                                   |

|------|----------|---------|------------|-----------------------------------------------------------------------------------------------|

| N    | Name     |         |            |                                                                                               |

| End  | Point Ou | it (EPO | ) Register | [ADDRESS=C_BASEADDR+XP_BASE+(0x80xN)+0x000+OFFSET]                                            |

| EPO_ | CNFG     | R/W     | 00h        | EPO Configuration Register.                                                                   |

|      |          | VALID   | [0]        | EP operation valid. When invalid and DPpacket is received, NRDY packet will be sent and then  |

|      |          |         |            | WRDY state.                                                                                   |

|      | IS       | OCHR    | [1]        | Isochronous mode transmission                                                                 |

|      |          | AGGR    | [2]        | Special mode that immediately sends ACK packet before IP core completes received DP packet    |

|      |          |         |            | data transfer to the main memory.                                                             |

|      | AUTO_    | STALL   | [3]        | If this bit is ON,                                                                            |

|      |          | ED      |            | Transit from STALLED without Software instruction and return STALL acknowledge to Host.       |

|      | E        | BURST   | [18:16]    | Set burst length.4~1. Normally "4", other setting for debug.                                  |

|      | FIFC     | D_REQ   | [30]       | Arbitration request of receiving FIFO of EPO. For debugging. Read only.                       |

|      | FIFC     | D_LOC   | [31]       | The mode which EPO occupies FIFO. For debugging.                                              |

| EPO_ | CNTL     | R/W     | 01h        | EPO control register. Show status and update all bits of [31:16].                             |

|      |          |         |            | Requesting interrupt if any bit in [13:0] is ON. [23:16] show detected events. [31:24] show   |

|      |          |         |            | transitional events.                                                                          |

| EPO_ | CLR      | W       | 02h        | EPO control register clear. Clear applicable bit by 1 writing.                                |

| EPO_ | SET      | W       | 03h        | EPO control register set. Set applicable bit by 1 writing.                                    |

|      |          | COMP    | [0]        | COMP state (transmission completed). Clear it to return to IDLE. OUTRDY will be cleared. When |

|      |          |         |            | extra DP packet is received, transit to NRDY.                                                 |

| EPO_DLEN       R/W       04h       EPO data length setting register         DLEN       [20:0]       Data length.         OUTRDY       [30]       OUT transmission (from Host to Device). Cleared by COMP state (passing NRDY,ERDY state).         EPO_PLEN       R       05h       EPO data length result register         PLEN       [20:0]       Actual transferred data length. Except 0 means a data is received.         OUTRDY       [31]       OUT transmission (from Host to Device). (Copy of DLENregister)         EPO_BFFR       R/W       06h       EPO data length buffer (memory address) register         BADDR       [27:8]       Start address of the memory for data input/output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |      |           |         |                                                                                                    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----------|---------|----------------------------------------------------------------------------------------------------|

| wRDY       [10]       wRDY state. After sending NRDY packet etc (flow state), become to the status. ERDY packet will be returned and transit to specified state when clearing.         NRDY       [11]       NRDY state. Under sending NRDYpacket. After a while, transit to WRDY state.         WAIT_RECV       [14]       Waiting for any packet. Valid when BUSY is ON.         BUSY       [15]       It is ON except (IDLE state or [13:0] state). When WAIT_RECV is ON, Clearing this bit to return to IDLE. And return to IDLE state when both this bit and [14] are cleared at same time.         STALL       [16]       STALL packet is received or some abnormal is detected.         OVER       [17]       Traffic of Host is a lot than DLEN. (Device side is fewer.)         UNDER       [18]       Traffic of Host is a few than DLEN. (Device side is more.)         RETRY       [24]       Error exists in received DP packet (include SetupDP packet).         INVALID       [25]       When IDLE state, ACKpacket is received at the state that DPpacket cannot be received. (VALID or OTRDY is OFF)         EPO_DLEN       RW       04h       EPO data length setting register         DLEN       [20:0]       Data length.       OUTRDY         OUTRDY       [30]       OUT transmission (from Host to Device). Cleared by COMP state (passing NRDY,ERDY state).         EPO_PLEN       R       05h       EPO data length. Except 0 means a data is received.  |      | STALLED   | [8]     | STALLED state. Return STALLpacket when clearing.                                                   |

| WRDY       [10]       WRDY state. After sending NRDY packet etc (flow state), become to the status. ERDY packet will be returned and transit to specified state when clearing.         NRDY       [11]       NRDY state. Under sending NRDYpacket. After a while, transit to WRDY state.         WAIT_RECV       [14]       Waiting for any packet. Valid when BUSY is ON.         BUSY       [15]       It is ON except (IDLE state or [13:0] state). When WAIT_RECV is ON, Clearing this bit to return to IDLE. And return to IDLE state when both this bit and [14] are cleared at same time.         STALL       [16]       STALL packet is received or some abnormal is detected.         OVER       [17]       Traffic of Host is a lot than DLEN. (Device side is fewer.)         UNDER       [18]       Traffic of Host is a few than DLEN. (Device side is more.)         RETRY       [24]       Error exists in received DP packet (include SetupDP packet).         INVALID       [25]       When IDLE state, ACKpacket is received at the state that DPpacket cannot be received. (VALID or OTRDY is OFF)         EPO_DLEN       R/W       04h       EPO data length setting register         DLEN       [20:0]       Data length.       OUTRDY         OUTRDY       [30]       OUT transmission (from Host to Device). Cleared by COMP state (passing NRDY,ERDY state).         EPO_PLEN       R       05h       EPO data length. Except 0 means a data is received. |      | DEFFERED  | [9]     | DEFFERED state. Transit to this state when the packet attaching Deffered bit is received. ERDY     |

| be returned and transit to specified state when clearing.         NRDY       [11]       NRDY state. Under sending NRDYpacket. After a while, transit to WRDY state.         WAIT_RECV       [14]       Waiting for any packet. Valid when BUSY is ON.         BUSY       [15]       It is ON except (IDLE state or [13:0] state). When WAIT_RECV is ON, Clearing this bit to return to IDLE. And return to IDLE state when both this bit and [14] are cleared at same time.         STALL       [16]       STALL packet is received or some abnormal is detected.         OVER       [17]       Traffic of Host is a lot than DLEN. (Device side is fewer.)         UNDER       [18]       Traffic of Host is a few than DLEN. (Device side is more.)         RETRY       [24]       Error exists in received DP packet (include SetupDP packet).         INVALID       [25]       When IDLE state, ACKpacket is received at the state that DPpacket cannot be received. (VALID or OTRDY is OFF)         EPO_DLEN       R/W       04h       EPO data length setting register         OUTRDY       [30]       OUT transmission (from Host to Device). Cleared by COMP state (passing NRDY,ERDY state).         EPO_PLEN       R       05h       EPO data length result register         OUTRDY       [31]       OUT transmission (from Host to Device). (Copy of DLENregister)         EPO_BFFR       R/W       06h       EPO data length buffer (memory address) registe          |      |           |         | packet will be returned and transit to specified state when clearing.                              |

| NRDY       [11]       NRDY state. Under sending NRDYpacket. After a while, transit to WRDY state.         WAIT_RECV       [14]       Waiting for any packet. Valid when BUSY is ON.         BUSY       [15]       It is ON except (IDLE state or [13:0] state). When WAIT_RECV is ON, Clearing this bit to return to IDLE. And return to IDLE state when both this bit and [14] are cleared at same time.         STALL       [16]       STALL packet is received or some abnormal is detected.         OVER       [17]       Traffic of Host is a lot than DLEN. (Device side is fewer.)         UNDER       [18]       Traffic of Host is a few than DLEN. (Device side is fewer.)         NVALID       [25]       Error exists in received DP packet (include SetupDP packet).         INVALID       [25]       When IDLE state, ACKpacket is received at the state that DPpacket cannot be received. (VALID or OTRDY is OFF)         EPO_DLEN       R/W       04h       EPO data length setting register         DLEN       [20:0]       Data length.         OUTRDY       [30]       OUT transmission (from Host to Device). Cleared by COMP state (passing NRDY,ERDY state).         EPO_PLEN       R       05h       EPO data length. Except 0 means a data is received.         OUTRDY       [31]       OUT transmission (from Host to Device). (Copy of DLENregister)         EPO_BFFR       R/W       06h       EPO data length buffer (memo                            |      | WRDY      | [10]    | WRDY state. After sending NRDY packet etc (flow state), become to the status. ERDY packet will     |

| WAIT_RECV       [14]       Waiting for any packet. Valid when BUSY is ON.         BUSY       [15]       It is ON except (IDLE state or [13:0] state). When WAIT_RECV is ON, Clearing this bit to return to IDLE. And return to IDLE state when both this bit and [14] are cleared at same time.         STALL       [16]       STALL packet is received or some abnormal is detected.         OVER       [17]       Traffic of Host is a lot than DLEN. (Device side is fewer.)         UNDER       [18]       Traffic of Host is a few than DLEN. (Device side is more.)         RETRY       [24]       Error exists in received DP packet (include SetupDP packet).         INVALID       [25]       When IDLE state, ACKpacket is received at the state that DPpacket cannot be received. (VALID or OTRDY is OFF)         EPO_DLEN       R/W       04h       EPO data length setting register         DLEN       [20:0]       Data length.         OUTRDY       [30]       OUT transmission (from Host to Device). Cleared by COMP state (passing NRDY,ERDY state).         EPO_PLEN       R       05h       EPO data length. Except 0 means a data is received.         OUTRDY       [31]       OUT transmission (from Host to Device). (Copy of DLENregister)         EPO_BFFR       R/W       06h       EPO data length buffer (memory address) register         BADDR       [27:8]       Stat address of the memory for data input/output.                                 |      |           |         | be returned and transit to specified state when clearing.                                          |

| BUSY       [15]       It is ON except (IDLE state or [13:0] state). When WAIT_RECV is ON, Clearing this bit to return to IDLE. And return to IDLE state when both this bit and [14] are cleared at same time.         STALL       [16]       STALL packet is received or some abnormal is detected.         OVER       [17]       Traffic of Host is a lot than DLEN. (Device side is fewer.)         UNDER       [18]       Traffic of Host is a lot than DLEN. (Device side is more.)         RETRY       [24]       Error exists in received DP packet (include SetupDP packet).         INVALID       [25]       When IDLE state, ACKpacket is received at the state that DPpacket cannot be received. (VALID or OTRDY is OFF)         EPO_DLEN       R/W       04h       EPO data length setting register         DLEN       [20:0]       Data length.         OUTRDY       [30]       OUT transmission (from Host to Device). Cleared by COMP state (passing NRDY,ERDY state).         EPO_PLEN       R       05h       EPO data length result register         PLEN       [20:0]       Actual transferred data length. Except 0 means a data is received.         OUTRDY       [31]       OUT transmission (from Host to Device). (Copy of DLENregister)         EPO_BFFR       R/W       06h       EPO data length buffer (memory address) register                                                                                                                       |      | NRDY      | [11]    | NRDY state. Under sending NRDYpacket. After a while, transit to WRDY state.                        |

| IDLE. And return to IDLE state when both this bit and [14] are cleared at same time.         STALL       [16]       STALL packet is received or some abnormal is detected.         OVER       [17]       Traffic of Host is a lot than DLEN. (Device side is fewer.)         UNDER       [18]       Traffic of Host is a few than DLEN. (Device side is more.)         RETRY       [24]       Error exists in received DP packet (include SetupDP packet).         INVALID       [25]       When IDLE state, ACKpacket is received at the state that DPpacket cannot be received. (VALID or OTRDY is OFF)         EPO_DLEN       R/W       04h       EPO data length setting register         DLEN       [20:0]       Data length.         OUTRDY       [30]       OUT transmission (from Host to Device). Cleared by COMP state (passing NRDY,ERDY state).         EPO_PLEN       R       05h       EPO data length. Except 0 means a data is received.         OUTRDY       [31]       OUT transmission (from Host to Device). Cleared by COMP state (passing NRDY,ERDY state).         EPO_BFFR       R/W       06h       EPO data length transferred data length. Except 0 means a data is received.         OUTRDY       [31]       OUT transmission (from Host to Device). (Copy of DLENregister)         EPO_BFFR       R/W       06h       EPO data length buffer (memory address) register         BADDR       [27:                                                      |      | WAIT_RECV | [14]    | Waiting for any packet. Valid when BUSY is ON.                                                     |

| STALL       [16]       STALL packet is received or some abnormal is detected.         OVER       [17]       Traffic of Host is a lot than DLEN. (Device side is fewer.)         UNDER       [18]       Traffic of Host is a few than DLEN. (Device side is more.)         RETRY       [24]       Error exists in received DP packet (include SetupDP packet).         INVALID       [25]       When IDLE state, ACKpacket is received at the state that DPpacket cannot be received. (VALID or OTRDY is OFF)         EPO_DLEN       R/W       04h       EPO data length setting register         DLEN       [20:0]       Data length.         OUTRDY       [30]       OUT transmission (from Host to Device). Cleared by COMP state (passing NRDY,ERDY state).         EPO_PLEN       R       05h       EPO data length. Except 0 means a data is received.         OUTRDY       [31]       OUT transmission (from Host to Device). Cleared by COMP state (passing NRDY,ERDY state).         EPO_BFFR       R/W       06h       EPO data length. Except 0 means a data is received.         OUTRDY       [31]       OUT transmission (from Host to Device). (Copy of DLENregister)         EPO_BFFR       R/W       06h       EPO data length buffer (memory address) register         BADDR       [27:8]       Start address of the memory for data input/output.                                                                                                                |      | BUSY      | [15]    | It is ON except (IDLE state or [13:0] state). When WAIT_RECV is ON, Clearing this bit to return to |

| OVER         [17]         Traffic of Host is a lot than DLEN. (Device side is fewer.)           UNDER         [18]         Traffic of Host is a few than DLEN. (Device side is more.)           RETRY         [24]         Error exists in received DP packet (include SetupDP packet).           INVALID         [25]         When IDLE state, ACKpacket is received at the state that DPpacket cannot be received. (VALID or OTRDY is OFF)           EPO_DLEN         R/W         04h         EPO data length setting register           DLEN         [20:0]         Data length.           OUTRDY         [30]         OUT transmission (from Host to Device). Cleared by COMP state (passing NRDY,ERDY state).           EPO_PLEN         R         05h         EPO data length. Except 0 means a data is received.           OUTRDY         [31]         OUT transmission (from Host to Device). (Copy of DLENregister)           EPO_BFFR         R/W         06h         EPO data length buffer (memory address) register                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      |           |         | IDLE. And return to IDLE state when both this bit and [14] are cleared at same time.               |

| UNDER       [18]       Traffic of Host is a few than DLEN. (Device side is more.)         RETRY       [24]       Error exists in received DP packet (include SetupDP packet).         INVALID       [25]       When IDLE state, ACKpacket is received at the state that DPpacket cannot be received. (VALID or OTRDY is OFF)         EPO_DLEN       R/W       04h       EPO data length setting register         DLEN       [20:0]       Data length.         OUTRDY       [30]       OUT transmission (from Host to Device). Cleared by COMP state (passing NRDY,ERDY state).         EPO_PLEN       R       05h       EPO data length. Except 0 means a data is received.         OUTRDY       [31]       OUT transmission (from Host to Device). (Copy of DLENregister)         EPO_BFFR       R/W       06h       EPO data length buffer (memory address) register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      | STALL     | [16]    | STALL packet is received or some abnormal is detected.                                             |

| RETRY       [24]       Error exists in received DP packet (include SetupDP packet).         INVALID       [25]       When IDLE state, ACKpacket is received at the state that DPpacket cannot be received. (VALID or OTRDY is OFF)         EPO_DLEN       R/W       04h       EPO data length setting register         DLEN       [20:0]       Data length.         OUTRDY       [30]       OUT transmission (from Host to Device). Cleared by COMP state (passing NRDY,ERDY state).         EPO_PLEN       R       05h       EPO data length result register         PLEN       [20:0]       Actual transferred data length. Except 0 means a data is received.         OUTRDY       [31]       OUT transmission (from Host to Device). (Copy of DLENregister)         EPO_BFFR       R/W       06h       EPO data length buffer (memory address) register         BADDR       [27:8]       Start address of the memory for data input/output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      | OVER      | [17]    | Traffic of Host is a lot than DLEN. (Device side is fewer.)                                        |

| INVALID       [25]       When IDLE state, ACKpacket is received at the state that DPpacket cannot be received. (VALID or OTRDY is OFF)         EPO_DLEN       R/W       04h       EPO data length setting register         DLEN       [20:0]       Data length.         OUTRDY       [30]       OUT transmission (from Host to Device). Cleared by COMP state (passing NRDY,ERDY state).         EPO_PLEN       R       05h       EPO data length result register         PLEN       [20:0]       Actual transferred data length. Except 0 means a data is received.         OUTRDY       [31]       OUT transmission (from Host to Device). (Copy of DLENregister)         EPO_BFFR       R/W       06h       EPO data length buffer (memory address) register         BADDR       [27:8]       Start address of the memory for data input/output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      | UNDER     | [18]    | Traffic of Host is a few than DLEN. (Device side is more.)                                         |

| OTRDY is OFF)         EPO_DLEN       R/W       04h       EPO data length setting register         DLEN       [20:0]       Data length.         OUTRDY       [30]       OUT transmission (from Host to Device). Cleared by COMP state (passing NRDY,ERDY state).         EPO_PLEN       R       05h       EPO data length result register         PLEN       [20:0]       Actual transferred data length. Except 0 means a data is received.         OUTRDY       [31]       OUT transmission (from Host to Device). (Copy of DLENregister)         EPO_BFFR       R/W       06h       EPO data length buffer (memory address) register         BADDR       [27:8]       Start address of the memory for data input/output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      | RETRY     | [24]    | Error exists in received DP packet (include SetupDP packet).                                       |

| EPO_DLEN       R/W       04h       EPO data length setting register         DLEN       [20:0]       Data length.         OUTRDY       [30]       OUT transmission (from Host to Device). Cleared by COMP state (passing NRDY,ERDY state).         EPO_PLEN       R       05h       EPO data length result register         PLEN       [20:0]       Actual transferred data length. Except 0 means a data is received.         OUTRDY       [31]       OUT transmission (from Host to Device). (Copy of DLENregister)         EPO_BFFR       R/W       06h       EPO data length buffer (memory address) register         BADDR       [27:8]       Start address of the memory for data input/output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |      | INVALID   | [25]    | When IDLE state, ACKpacket is received at the state that DPpacket cannot be received. (VALID or    |