IPLockで FPGAロジックセキュリティ・システムをかんたんに実装

| FPGAの大規模化に伴い、回路データの価値が非常に高くなっています。この貴重な設計資産がコピーされてしまうと、その被害は甚大です。この重要なIP資産を不正な複製からプロテクトするために、IPLockが非常に有効です。 |

動作原理

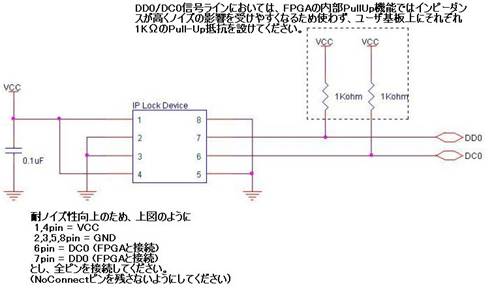

FPGAとの接続はわずか2ピン

基板パターン検討段階で、IPLock用SOIC-8パターンの追加がおすすめです。

実機動作例

試作時・量産時に適した製品ラインナップ

「ラボラトリーズ・パック」は、チップにユニークID書き込み済みで、少量試作用に最適です。

「ライタ・セット」はブランク・チップに任意のIDを書き込むタイプで、量産用に最適です。

詳しくは、YouTubeビデオを御覧ください。

IPLock デモビデオ(日本語)

IPLock デモビデオ(英語・最新版)

IPLockについて、詳しくはこちら

IPLockについて、お気軽にお問い合わせください