デザイン・ゲートウェイ Hot!ニュース

2023年4月号(2)

|

ウェブで開く デザイン・ゲートウェイ Hot!ニュース 2023年4月号(2) |

| FPGA バリューアテッド・ソリューション |

|

| デザイン・ゲートウェイは、FPGA搭載製品の柔軟なアップグレードやセキュリティー強化を実現する製品を提供しております。Mouser から短納期での入手が可能です。 |

|

FPGAコンフィグ・モジュール「SDLink」 |

FPGAロジック保護・コピー防止「IPLock」 |

| デザイン・ゲートウェイのmicroSDカード採用、超高速コンフィグ・モジュールSDLinkは、標準ROMとの混在&切り替えが可能のため、短納期のSDLinkを先行してFPGA製品に搭載することにより、標準ROM入手までの期間を待たずに、製品開発および早期の製品リリースが可能になります。 | IPLockは、信頼性の極めて高いAES暗号技術を採用したFPGAロジックセキュリティ・システムです。FPGA接続は2ピンのみで取り扱いは超簡単、安心安全にFPGA製品の貸出/提供が可能になります。 |

標準ROMとの混在回路が可能 標準ROMとの混在回路が可能基板デザイン・ガイド 回路図チェックサポート お問い合わせはこちらから |

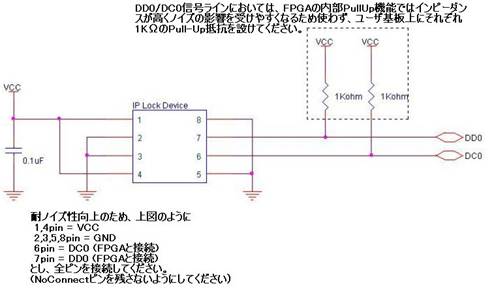

1.8V駆動「IPL-CHP1.8V」は、1.8V/2.5V/3.3Vいずれの電圧にも対応しており、使用 I/Oバンクの制約を気にせず設計の自由度が向上します。 1.8V駆動「IPL-CHP1.8V」は、1.8V/2.5V/3.3Vいずれの電圧にも対応しており、使用 I/Oバンクの制約を気にせず設計の自由度が向上します。 |

| SDLinkで回路データを即時アップデート |

|

[開発時] 色々なパターンの回路を即評価可能! | |

| microSDカードを複数使用して、再プログラミングによる中断なしに色々なパターンの回路データを試すことができるので、開発や評価のスピードが飛躍的に向上します。SDLinkについて詳しくはこちら | ||

|

|

||

|

[出荷後] 量産品のアップデートを迅速に対応可能! | |

| microSDカードの差し替えだけで回路をかんたんアップデートします。 ボードへの直接プログラミングが不要になるため、納品後の回路データの修正、システムに組み込まれた後のアップデート対応、頻繁に回路データの入れ替えが必要なシステムへの迅速な対応を可能にします。SDLinkについて詳しくはこちら |

||

| IPLockで設計資産を保護 |

|

簡単にIPコアプロテクトを実現! | |

|

||

|

|

||

|

堅牢プロテクトのヒミツ | |

|

||

| YouTube最新動画 |

| DG IP コア YouTube チャンネルに登録する |

|

Part1: NVMeTCP25G-IP 4 セッション・デモ紹介 |

Part2: NVMeTCP25G-IP 4 セッション評価デモ |

| 株式会社デザイン・ゲートウェイ | 会社概要 | 個人情報保護 | 配信停止 | お問い合わせ | (c) 2023 Design Gateway Co., Ltd. |