デザイン・ゲートウェイ Hot!ニュース

2024年6月号

|

ウェブで開く デザイン・ゲートウェイ Hot!ニュース 2024年6月号 |

| ナノ秒レベルのレイテンシーで金融市場取引での利益を最大化する ネットワーク・ソリューション .png) |

|

AMD (Xilinx)向け 超低遅延ソリューション | Altera (Intel)向け 超低遅延ソリューション |

|

競争が激化している金融市場でのアルゴリズム取引において、ナノ秒レベルのレイテンシーの実現は極めて重要になっています。高位合成(HLS)とデザイン・ゲートウェイのTOE10GLL-IPコアにより、超低遅延、高信頼、市場環境の変化にリアルタイムに対応した取引アルゴリズムの運用が可能となります。 |

|

|

高位合成(HLS)による迅速なイノベーションとアクセラレーション

シンプルなC/C++ で高度な取引アルゴリズムの開発が可能です。HLS により、ソフトウェア開発者は FPGA にアルゴリズムを簡単に実装することができ、従来のソフトウェア手法では達成できなかった超低レイテンシーを実現することができます。このアプローチにより、開発プロセスを簡素化するだけでなく、市場投入までの時間を大幅に短縮します。 |

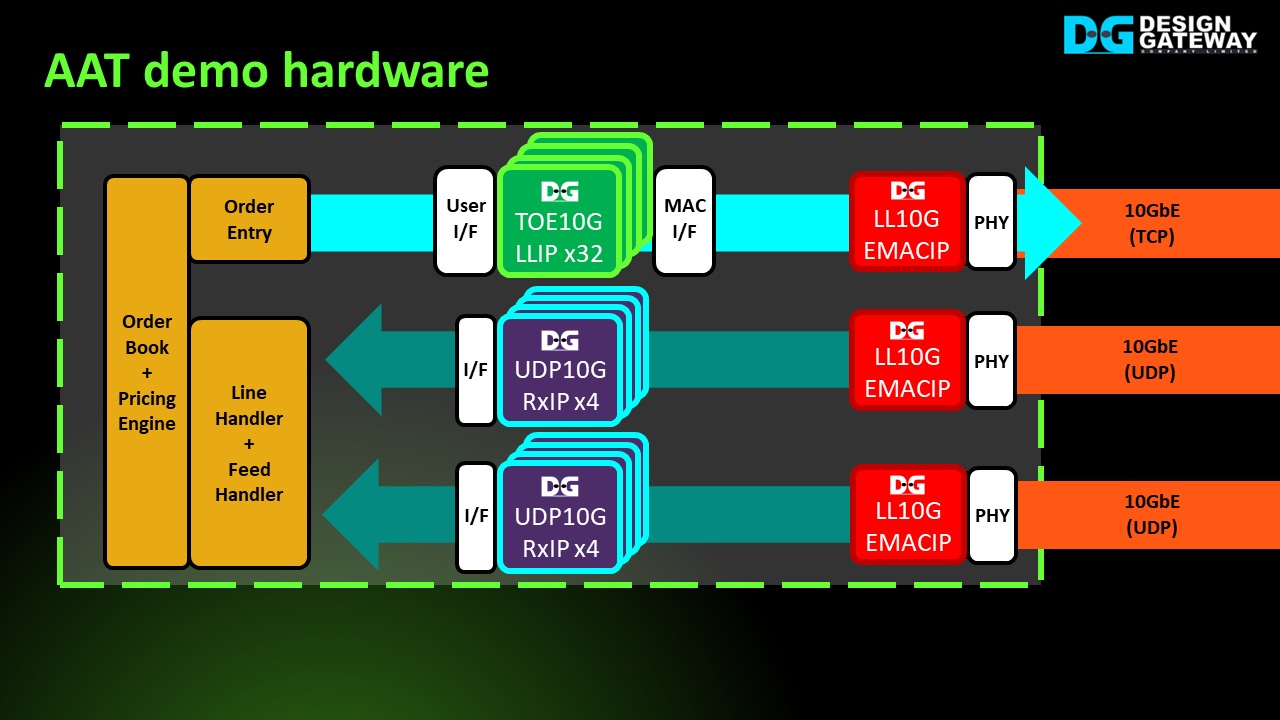

| AMD Xilinx の無償AAT デモで始めよう

FPGAベースでのトレーディングを初めて体験される方には、AMD Xilinxの AAT (Accelerated Algorithmic Trading) デモが最適です。この無償デモでは、FPGA アクセラレーションの利点を低コスト、低リスクの環境で試すことができ、PoC段階に最適です。 AATデモについて詳しくはこちら |

TOE10GLL-IP で超低遅延化、市場に投入

概念実証が検証されたら、いよいよ製品化です。当社のTOE10GLL-IPは完璧なソリューションを提供します。超低レイテンシーと高い安定性を実現するTOE10GLL-IPは、専用TCP/IPオフロード・エンジンを持たない他のFPGAソリューションと比較しさらに多くのアドバンテージがあります。 TOE10GLL-IPについて詳しくはこちら |

| TCP HLS | TOE10GLL-IP | |

| 種類 | オープンソース | 商用 |

| レイテンシー | 250 - 300 ns | 34.3 ns (IPコア + AXIアダプタ込み) |

| 安定性 | 潜在的な問題の可能性 | 実証済み |

| 技術サポート | 限定的 | 安心の国内サポート |

| 記述言語 | C/C++ | HDL |

| コスト | デモは無償 | 高費用対効果 |

| アプリケーション例 | |

|

リアルタイム取引: FPGA上で直接アルゴリズムを実行し、取引実行までの時間を極限まで最短化します。

パフォーマンスを損なうことなく、複数の取引戦略と高頻度データ・フィードを同時に管理します。 |

|

HLSのメリットを初期開発において活用し、TOE10GLL-IPで製品版環境にシームレスに移行します。この組み合わせにより、最速かつ高信頼性の取引執行を実現し、アルゴリズム取引における優位性を保つことが可能になります。 TOE10GLL-IPおよびAATデモの詳細情報は弊社ウェブサイトをご覧いただくか、お問い合わせください。 |

|

| 超低遅延ネットワークIPコア & AAT デモ YouTube動画 |

Breaking Latency Barriers in Stock Trading with AMD Xilinx AAT & DG Low Latency IP cores ブログ記事を読む |

Design Gateway Low Latency 10G EMAC-IP with Xilinx AAT demo |

| イベント情報 |

| 画像センシング展2024 日 時 : 2024/6/12-14, 会 場 : パシフィコ横浜 詳 細 Interop Tokyo 2024 日 時 : 2024/6/12-14, 会 場 : 幕張メッセ 詳 細 日本 ものづくり ワールド 2023 ものづくりAI/IoT展 日 時 : 2024/6/19-21, 会 場 : 東京ビッグサイト 詳 細 電子機器2024 トータルソリューション展 日 時 : 2024/6/12-14, 会 場 : 東京ビッグサイト 詳 細 Computex Taipei 2024 日 時 : 2024/6/4-7, 会 場 : Taipei Nangang Exhibition Center, Taipei 詳 細 NEPCON THAILAND 2024 日 時 : 2024/6/19-22, 会 場 : BITEC, Bangkok, Thailand 詳 細 |

| 株式会社デザイン・ゲートウェイ | 会社概要 | 個人情報保護 | 配信停止 | お問い合わせ | (c) 2024 Design Gateway Co., Ltd. |