Super Low Latency Networking IPfor fintech

Design Gateway’s Low Latency Networking IP is designed from the ground

up for very low latency requirements. Especially, FinTech applications

such as high-frequency trading (HFT), high speed trading (HST), Market

Data Processing and Tick-to-Trade (T2T) systems. We can provide total solutions

for low latency Networking IP cores and FPGA logic customization for application

specific requirements. Contact Us

Design Gateway’s Low Latency Networking IP is designed from the ground

up for very low latency requirements. Especially, FinTech applications

such as high-frequency trading (HFT), high speed trading (HST), Market

Data Processing and Tick-to-Trade (T2T) systems. We can provide total solutions

for low latency Networking IP cores and FPGA logic customization for application

specific requirements. Contact UsAccelerated High Frequency Trading (HFT) reference design with Alveo X3 Card

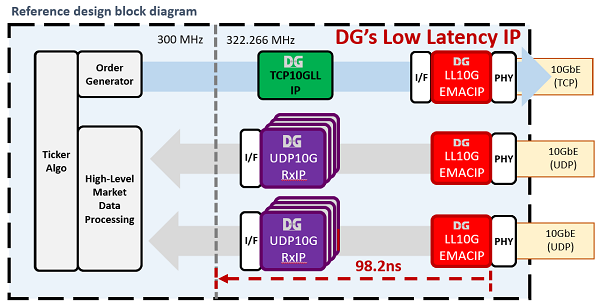

Supercharge your trading strategies with the Accelerated Algorithmic Trading (AAT) Accelerator & System — a cutting-edge turnkey solution engineered to meet the relentless demands of today's financial markets. Powered by FPGA acceleration and ultra-low-latency IP core technology, the AAT System is the ultimate tool for Brokers, Exchanges, Market Data Vendors, Sell-Side Vendors, and Proprietary Traders seeking a definitive competitive edge.

DG's Low latency IP Cores (TOE, UDP and EMAC) demo together with Accelerated Algorithmic Trading (AAT) reference design based on HLS(C/C++) example code is now available on Alveo X3552PV Card and also standard alone AMD FPGA Boards.click for demo

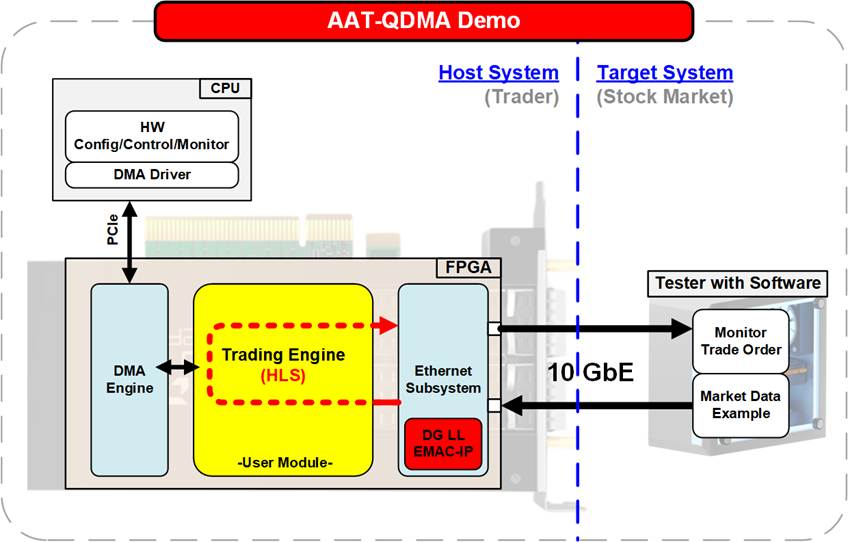

The Accelerated Algorithmic Trading with QDMA (AAT-QDMA) demo is the latest reference design demonstrates a high-performance trading system over 10G Ethernet based on best in class cost effective and super low latency, Alveo X3552PV Card and HLS(C/C++) based reference design for High Frequency Trading application by FPGA hardware. More detail

Features

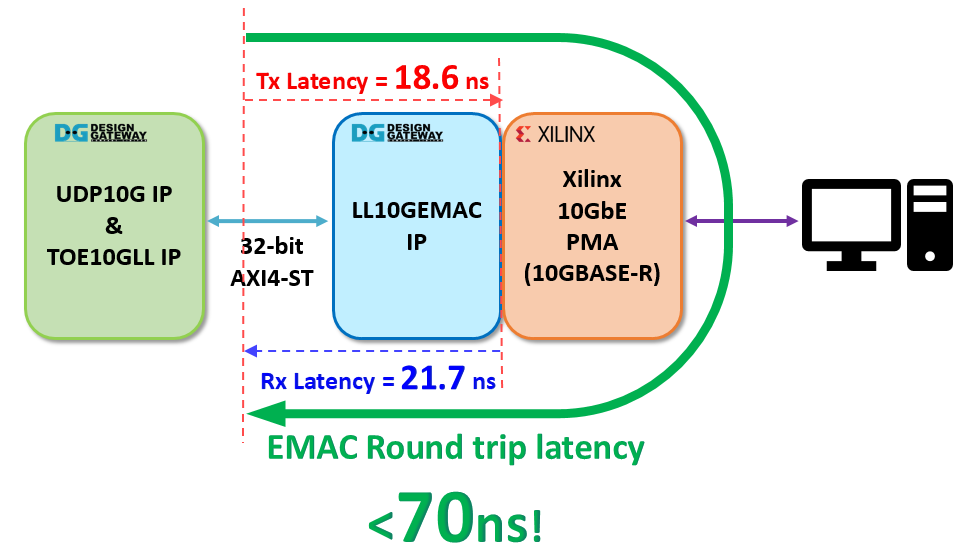

Low Latency 10GEMAC-IP (LL10GEMAC-IP)

|

DG LL 10G EMAC-IP + AAT QDMA Demo |

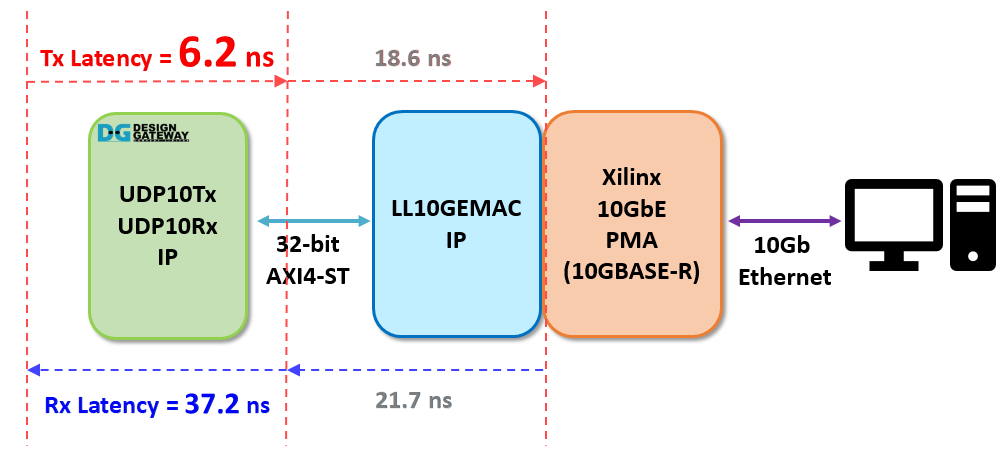

Low Latency UDP10G Rx/Tx-IP

|

DG LL UDP10GRx-IP 16 Sessions demo for FinTech |

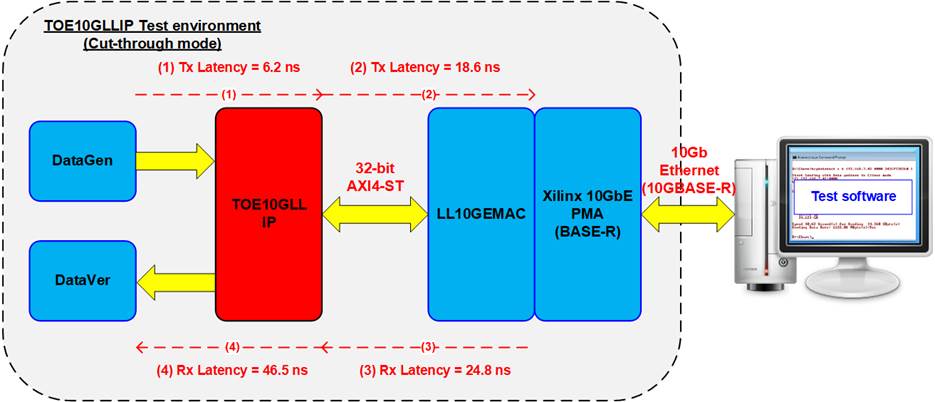

Low Latency TOE10G-IP (TOE10GLL-IP)

|

DG TOE10GLL-IP 32 Sessions demo |

Document download

| Document name | Update (Revision) |

| Presentation | 1.0E |

| Brochure | 2.6EX |

| IP core & Option | Datasheet | Reference Design Document | Demo Instruction Document | FPGA Board Setup | Free Evaluation demo file | |

| Accelerated Algorithmic Trading (AAT) Demo |

Rev2.0 | Rev1.1 | U50 U250 |

|

||

|

|

||||||

| LL 10GEMAC-IP | Rev1.04 | Rev1.1 | Rev1.1 | Rev1.0 | ZCU102 | |

| Accelerated Algorithmic Trading (AAT) QDMA Demo |

Rev1.00 | Rev1.01 | X3522 U50 U55C U250 |

|

||

| Accelerated Algorithmic Trading (AAT) Demo |

Rev1.1 | Rev1.03 | U50 U250 |

|

||

|

|

||||||

| LL UDP10GRx-IP | Rev2.0 | Rev1.2 | Rev1.2 | Rev1.1 | ZCU102 KCU116 |

|

| 16 Session Demo | Rev1.0 | Rev1.0 | ZCU102 KCU116 |

|

||

|

|

||||||

| TOE10GLL-IP | Rev2.0 | Rev1.2 | Rev1.1 | ZCU102 ZCU106 |

||

| 32 Session Demo | Rev1.0 | Rev1.0 | ZCU102 ZCU106 |

|

||

For more detail, please Contact Us

Alliance Partner

Design Gateway Co., Ltd.

Head Office3-23-17 Naka-cho, Koganei, Tokyo, JAPAN

R&D

89/26 Amornpan 205 Tower1, 18th floor, Ratchadapisek7 (Nathong) Alley, Ratchadapisek Road, Din Daeng, Bangkok, 10400 THAILAND

AI Lab

Faculty of Engineering, Chulalongkorn University, 12th floor, Engineering 4 Building (Charoenvidsavakham), Phayathai Rd., Wang Mai, Pathumwan, Bangkok, 10330 THAILAND