デザイン・ゲートウェイ Hot!ニュース

2023年10月号(1)

|

ウェブで開く デザイン・ゲートウェイ Hot!ニュース 2023年10月号(1) |

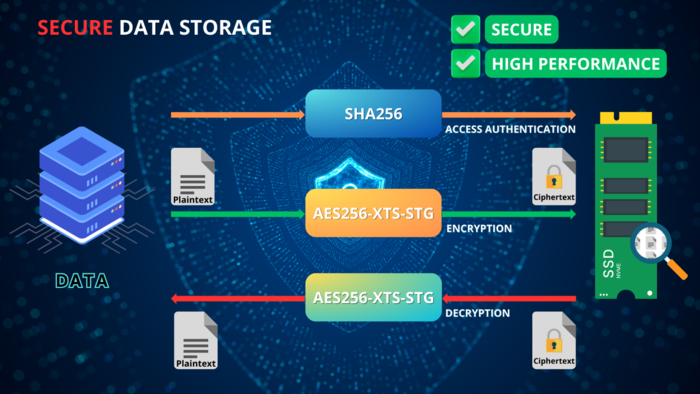

| 完全ハードウェアで実現 SHA-256 & AES-XTS 暗号化による、セキュアなストレージ・システム |

|

CPUレス 完全ハードウェア セキュリティ・ソリューションについて詳しく |

|

| 多くのアプリケーションにおいてデータ・ストレージが必須となっていますが、データの完全性、機密性、信頼性といったセキュリティ上の重要な課題も抱えています。データ・ストレージを不正アクセスや改ざん保護するためにSHA-256 や AES-XTSといった暗号アルゴリズムが広く使用されています。 SHA-256は、ファイルの破壊や改ざんがないかを保証するために有効です。1GBを超えるような大きなデータサイズの場合、CPU負荷が大きくなります。 AES-XTSは、保存時にデータの機密性を保証するのに有効です。AES-XTSの秘密鍵は、AES暗号化と、XTSでランダム性を付加する部分で構成されます。NVMe SSDへリアルタイムのAES-XTS暗号化を実現するには、暗号化性能がPCIe Gen3(4GB/s)、Gen4(8GB/s)、Gen5(16GB/s)の速度についてゆく必要があり、高速暗号化処理をCPUで実行するのは困難です。  デザイン・ゲートウェイのセキュリティIPコアは、暗号アルゴリズム・アクセラレーションの最適なソリューションです。CPU/GPUと比較し下記のアドバンテージがあります。

|

|

|

| SHA256 IP は、FIPS 180-4 準拠の セキュア・ハッシュ・アルゴリズム SHA-256 を搭載したIPコアです。本IPコアは、わずか65クロックの超低レンテンシで512ビットのデータ・ブロックを処理し、200MHz動作周波数で

1.575Gbps のスループットを実現します。 SHA256 IP について詳しく |

AES256-XTS-STG IPは、XEX(XOR Encrypt XOR)可変ブロック暗号を伴う高度な暗号化規格(AES)を実装し、NVMeやSATAストレージ・デバイス上の機密性の高いデータを保護する必要のあるアプリケーションに最適です。NVMe

PCIe Gen4 に最適な「2X」、およびGen5に対応した「4X」をラインナップしております。 AES256-XTS-STG IP について詳しく |

| AES256-XTS-STG IP コア YouTube動画 |

Enhancing NVMe SSD Security with AES256-XTS-STG Encryption ブログ記事で読む |

PCIe Gen5の超高速転送速度を損なわずにAES-XTS 暗号化による NVMe SSD データ・セキュリティを強化することが可能です。 CPUおよび外部メモリ不要のため、ユーザー・フレンドリーで実装が簡単です。 AES256-XTS-STG-4X IP & NVMe Gen5 SSDデモを Intel® Agilex™ 7 I-Series FPGAボードにて評価可能です。SSDの性能をフルに引き出す 10,000MB/秒超のセキュア・データ転送を実現しました。 |

| 株式会社デザイン・ゲートウェイ | 会社概要 | 個人情報保護 | 配信停止 | お問い合わせ | (c) 2023 Design Gateway Co., Ltd. |