Security & Search IP Coreshigh-throughput & minimum latency

Design Gateway provides security IP cores and search IP core that are highly compatible with DG's ultra-high-speed storage and network IP cores. By implementing highly reliable security features for ultra-high-speed data transfer, it becomes possible to develop even higher value-added applications.

| for Mission-critical Applications | Secure authentication | AEAD for Secure Network Application |

for Secure Storage Application |

High throughput Encryption IP | High throughput Hash IP | 400M SPS Search Engine |

|

TLS1.3 IP |

ECDSA256 IP |

AES256-GCM IP |

ChaCha20-Poly1305 IP |

AES256-XTS IP |

AES256/128 IP |

SHA2/256 IP |

tCAM IP |

Introduction VideoSecurity IPs Introduction Video Blogs [Security] |

Features of Security IPs

|

Product Brochuresfor AMD (Rev2025Q4EX) | for Altera (Rev2026Q1)Technical UpdatesTechnical & Marketing Document Updates |

Security IP core series Design Guide |

CPU-less TLS1.3 Offload IP core for FPGA Acceleration [TLS1.3 IP]

for Altera | for AMD |

TLS1.3 IP (Transport Layer Security IP) is the CPU-less & High-performance TLS v1.3 protocol engine for FPGA Acceleration with no CPU and external memory required. Providing maximum Gigabit Ethernet throughput for highly secure data transmission over 1G/10G/25G/100G network. Protect your valuable data from potential security breaches by using TLS secure transmission now! Especially, in Industrial IoT & Automation, Aerospace & Defense Applications. Our TLS 1.3 IP core demo can successfully demonstrate very high throughput HTTPS Upload and Download with standard web server by pure hardware logic on FPGA. |

YouTube Video TLS1.3 Server 10G IP Introduction & Performance Demo |

Key Features

|

Security for Authentication Applications [ECDSA256V-IP]

|

Hardware-Accelerated Digital Signature Verification for High-Security SystemsThe ECDSA256V-IP core implements Elliptic Curve Digital Signature Algorithm (ECDSA) verification on the NIST P-256 curve, providing a high-performance, hardware-only solution for secure authentication in modern communication and IoT systems. It eliminates CPU load by performing full signature verification entirely in hardware, without requiring software or external memory. This IP is compliant with FIPS 186-4 and validated with official NIST test vectors, ensuring accuracy and standard compliance. |

YouTube Video NIST-Compliant ECDSA P-256 Verification on FPGA Secure Hardware Demo |

Key Features

|

Technical Documents

| IP core | Document Name | Altera | AMD |

| ECDSA256V-IP | Datasheet | Contact us | Rev1.00 |

| Reference Design Document | Rev1.00 | ||

| Demo Instruction Document | Rev1.00 | ||

| Free Evaluation Demo file | KR260 |

Security for Networking Applications [AES256-GCM IP]

|

High throughput & Super Low Latency for secure communication applications.The AES256-GCM IP core implements the Advanced Encryption Standard (AES) with a 256-bit key in Galois/Counter Mode (GCM), which is widely used for Authenticated Encryption with Associated Data (AEAD) applications. This IP has been verified against the official NIST (National Institute of Standards and Technology) test vectors, as defined in SP 800-38D, ensuring standards compliance. It is well-suited for high-performance, low-latency, and secure communication applications. |

YouTube Video Validating DG’s AES256GCM IP with NIST Test Vectors  AES256-GCM100G IP Introduction & Demo |

Features

|

Technical Documents

| IP core | Document Name | Altera | AMD |

| AES256-GCM 100G IP |

Datasheet | Rev1.00 | Rev1.00 |

| Reference Design Document | Rev1.00 | Rev1.00 | |

| Demo Instruction Document | Rev1.00 | Rev1.01 | |

| Free Evaluation Demo file | Agilex™ F-series Arria® 10 SX |

ZCU106 KCU116 |

|

| Free Evaluation Project | Github |

||

|

|

|||

| AES256-GCM 10G 25G IP |

Datasheet | Rev2.02 | Rev2.02 |

| Reference Design Document | Rev2.01 | Rev2.02 | |

| Demo Instruction Document | Rev2.02 | Rev2.02 Rev1.00 (KR260-Ubuntu) |

|

| Free Evaluation Demo file | Agilex™ 7 F-series Agilex™ 5 E-series Arria® 10 SX |

KCU116 ZCU106 ZCU102 KR260-no OS KR260-Ubuntu |

|

| Free Evaluation Project | Github |

||

|

|

|||

| AES256-GCM 1G IP |

Datasheet | Rev1.00 | Rev1.00 |

| Reference Design Document | Rev1.00 | Rev1.00 | |

| Demo Instruction Document | Rev1.00 | Rev1.00 | |

| Free Evaluation Demo file | Agilex™ 5 E-series | ZCU106 | |

|

|

|||

| Common | AES-IP core series Design Guide | Rev1.00 | |

High-Performance & Highly Secure AEAD Encryption Engine [ChaCha20-Poly1305 IP ]

|

The ChaCha20-Poly1305 IP core implements the ChaCha20 stream cipher together with the Poly1305 message authentication code (MAC), following the IETF standard for Authenticated Encryption with Associated Data (AEAD). ChaCha20 provides high-speed encryption and decryption with strong resistance against timing attacks, while Poly1305 ensures message authentication and integrity. Together, they form a widely adopted AEAD construction. The core supports a 256-bit key size and a 96-bit IV size. It also supports zero-length Additional Authenticated Data (AAD) or plaintext input, making it flexible for a wide range of secure applications. |

YouTube Video ChaCha20-Poly1305 IP Introduction & Demo |

Features

|

Technical Documents

| IP core | Document Name | Altera | AMD |

| ChaCha20-Poly1305 IP | Datasheet | Contact us | Rev1.00 |

| Reference Design Document | Rev1.00 | ||

| Demo Instruction Document | Rev1.00 | ||

| Free Evaluation Demo file | ZCU106 |

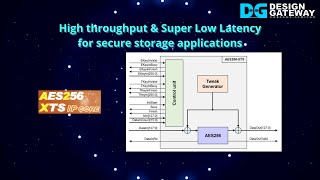

Security for Storage Applications [AES256-XTS IP]

High throughput & Super Low Latency for secure storage applicationsAES256-XTS-STG IP implement the advanced encryption standard (AES) with XEX (XOR Encrypt XOR) tweakable block cipher which operates sequences of complete blocks and is widely used in protecting the confidentiality of data on various storage devices with interfaces such as NVMe and SATA. We also have a lineup of "2X" ideal for NVMe PCIe Gen4, and "4X", supported Gen5. |

|

Features

YouTube Video Enhancing NVMe SSD Security with AES256-XTS-STG Encryption |

|

Technical Documents

| Document Name | Altera | AMD |

| AES256-XTS-STG IP Datasheet | Rev1.00 | Rev1.01 |

| AES256-XTS-STG IP Reference Design Document |

Rev1.00 | Rev1.00 |

| AES256-XTS-STG IP with NVMe-IP Reference Design Document |

Rev1.01 | Rev1.03 |

| Demo Instruction Document | Rev1.00 | Rev1.01 |

|

|

||

| Free Evaluation Demo file | ||

| AES256-XTS-STG IP (for NVMe Gen3) | Arria® 10 SX | |

| AES256-XTS-STG-2X IP (for NVMe Gen4) | VCK190 | |

| AES256-XTS-STG-4X IP (for NVMe Gen5) | Agilex™ I-series | VPK120 |

| AES256-XTS-STG IP (with NVMe Gen3 IP) | Arria® 10 SX | |

| AES256-XTS-STG-2X IP (with NVMe Gen4 IP) | VCK190 | |

| AES256-XTS-STG-4X IP (with NVMe Gen5 IP) | Agilex™ I-series | VHK158 |

|

|

||

| Free Evaluation Project | ||

| AES256-XTS-STG IP (for NVMe Gen3) | Github |

|

| AES256-XTS-STG-2X IP (for NVMe Gen4) | Github |

|

| AES256-XTS-STG-4X IP (for NVMe Gen5) | Github |

|

AES256-XTS IP Core (AES256XTSIP) implement the advanced encryption standard (AES) with XEX Tweakable Block Cipher with Ciphertext Stealing (XTS) which is widely used in protecting the confidentiality of data on storage devices.

YouTube Video AES256-XTS IP Introduction & Demo |

Features

|

Technical Documents

| Document Name | Altera | AMD |

| Datasheet | Rev1.01 | Rev1.01 |

| Reference Design Document | Rev1.00 | Rev1.00 |

| AES-IP core series Design Guide | Rev1.00 | Rev1.00 |

| Demo Instruction Document | Rev1.00 | Rev1.00 |

| Free Evaluation Demo file | Agilex™ F-series Arria® 10 SX |

ZCU106 |

High Throughput Encryption [AES-256SS IP | AES-256 IP | AES-128 IP]

AES-256SS IP specializes in ultra-high throughput and ultra-low latency. IP computes 128-bit data blocks in every 1 clock cycle. Delivering 128Mbps throughput per 1MHz such as 51.2 Gbps @ 400MHz.

AES-128 IP is 1st member of Advanced Encryption Standard (FIPS-197) IP Series, designed to support ECB mode for both encryption and decryption. AES128-IP computes 128-bit data blocks within constant 11 clock cycles. Delivering 11.6Mbps throughput per 1MHz such as 5.8 Gbps @ 500MHz. AES Encryption IP Series is designed to enhance security features of existing Data Storage and Networking IP Cores. Enabling more opportunity for inventing the secure, efficient and high performance applications. |

|

Features |

YouTube Video |

|

AES-128 IP Introduction |

Technical Documents

| IP core | Document Name | Altera | AMD |

AES-256SS IP |

Datasheet | Rev1.03 | Rev1.04 |

| Reference Design Document | Rev1.02 | Rev1.02 | |

| Demo Instruction | Rev1.02 | Rev1.02 | |

| Free Evaluation Demo file | Agilex™ F-series Arria® 10 SX |

ZCU106 | |

AES-256 IP |

Datasheet | Rev1.03 | Rev1.04 |

| Reference Design Document | Rev1.03 | Rev1.02 | |

| Demo Instruction | Rev1.03 | Rev1.02 | |

| Free Evaluation Demo file | Agilex™ F-series Arria® 10 SX |

ZCU106 | |

AES-128 IP |

Datasheet | Rev1.03 | Rev1.03 |

| Reference Design Document | Rev1.03 | Rev1.03 | |

| Demo Instruction | Rev1.02 | Rev1.02 | |

| Free Evaluation Demo file | Agilex™ F-series Arria® 10 SX |

ZCU106 | |

|

|

|||

| Common | AES-IP core series Design Guide | Rev1.00 | |

High Throughput Security [SHA2-IP / SHA-256 IP]

The SHA2 IP Core supports SHA-224, SHA-256, SHA-384, SHA-512, SHA-512/224, and SHA-512/256 secure hash algorithms. The core is fully compliant with the FIPS PUB 180-4 (Federal Information Processing Standard) specification. Suitable for applications such as secure communication, password authentication, and blockchain data integrity.

Features |

|

Technical Documents |

| Document Name | Altera | AMD |

| Datasheet | Rev1.00 | Rev1.00 |

| Referrence Design Document | Rev1.00 | Rev1.00 |

| Demo Instruction | Rev1.00 | Rev1.00 |

| Evaluation Demo file | Agilex 7 I-series Arria 10 SX |

KCU116 |

SHA-256 IP is an optimized and efficient implementation of a secure hash algorithm SHA-256 specified in FIPS 180-4 standard. SHA256-IP can process 512-bit data blocks in just 65 clock cycles. Delivering 7.875Mbps throughput per 1MHz clock such as 2.362 Gbps throughput @ 300MHz. * tentative

SHA-256 is one of the most secure and practically unbreakable hashing functions which is most popular to use in various applications such as secure password hashing, digital signature, SSL/TLS certificate and Bitcoin cryptocurrency.

Together with Design Gateway's data storage and networking IP, SHA256-IP enables more opportunity for inventing the secure, efficient and high performance applications.

Features |

YouTube Video |

|

SHA-256 IP introduction |

Technical Documents |

| Document Name | Altera | AMD |

| Datasheet | Rev1.00 | Rev1.00 |

| Demo Instruction | Rev1.00 | Rev1.00 |

| Evaluation Demo file | Arria 10 SX | KCU105 |

HIgh-speed & Low latency Search Engine [tCAM IP]

tCAM-IP is a high-performance, extremely low-latency, and highly configurable ternary content-addressable memory IP. tCAM-IP can make continuous deterministic search at 400 MSPS with constant latency of 7 clock cycles. It can achieve matching/filtering performance of 400,000,000 packets per second over Gigabit Ethernet. It is ideal for various applications such as network packet filtering/forwarding, intelligent switch/router, deep packet inspection, and network security applications. We can provide tCAM-IP custom reference designs together with TOE-IP core series, UDP-IP core series, and EMAC-IP based on customer requirements. Contact Us |

|||

| Altera | AMD | ||

| tCAM IP for Altera | tCAM IP for AMD | ||

YouTube Video |

|||

UDP Packet Filtering & Switching Demo |

tCAM-IP introduction |

tCAM-IP performance demo on Arria 10 SX |

tCAM-IP performance demo on KCU116 |

Blogs

- What's TCAM?

- TCAM Accelerator for FPGA Based Systems: A High-Performance and Flexible Solution for Various Applications

- Boost Network Efficiency: How tCAM-based packet switching enhances data flow

Alliance Partner

Design Gateway Co., Ltd.

Head Office3-23-17 Naka-cho, Koganei, Tokyo, JAPAN

R&D

89/26 Amornpan 205 Tower1, 18th floor, Ratchadapisek7 (Nathong) Alley, Ratchadapisek Road, Din Daeng, Bangkok, 10400 THAILAND

AI Lab

Faculty of Engineering, Chulalongkorn University, 12th floor, Engineering 4 Building (Charoenvidsavakham), Phayathai Rd., Wang Mai, Pathumwan, Bangkok, 10330 THAILAND