セキュリティIPコアSecurity & Search IPs

| ミッション クリティカル アプリケーション向け |

ストレージ・ アプリケーション向け 暗号&認証処理 |

ネットワーク・ アプリケーション向け 暗号&認証処理 |

超高スループット 51.2Gbps 暗号化IP | 超高スループット セキュリティIP |

超高速200M SPS &低遅延検索IP |

TLS1.3 IP TLS1.3 IP |

AES256-XTS IP AES256-XTS IP |

AES256-GCM IP AES256-GCM IP |

AES256/128 IP AES256/128 IP |

SHA2/256 IP SHA2/256 IP |

tCAM IP tCAM IP |

紹介ビデオセキュリティ IP 紹介・アプリ例 1分でわかる ブログ記事を読む |

セキュリティIP コア 共通コンセプト & 特長

|

総合カタログAMD版 (Rev2025Q1JX) | Altera版 (Rev2025Q1JA)最新技術情報技術&営業資料 アップデート情報 |

セキュリティIPコアシリーズ デザインガイド |

高度なTLS1.3 セキュリティをCPUレスで実現 [TLS1.3 IP]

|

TLS1.3 IP (Transport Layer Security IP)は、CPUおよび外部メモリ不要の、高性能TLS v1.3プロトコル・エンジンです。1G/10G/25G/100G各ネットワーク上での高度で安全なデータ伝送のため最速のギガビット・イーサネット・スループットを提供します。TLSによるセキュアな転送により、データを潜在的なセキュリティ侵害から保護し、特に産業用IoT&自動化、航空宇宙関連のアプリケーションにおいて最適なソリューションです。 TLS 1.3 IPコアデモでは、ネットワーク上のクライアントとサーバー間の安全な接続を確保するための暗号化プロトコルを実装し、純ハードウェア・ロジックによる標準的なウェブサーバーとの非常に高いスループットのHTTPSのアップロードとダウンロードの実機評価が可能です。 |

YouTube ビデオ TLS1.3 IPコア KR260 エッジ-クラウド間セキュア通信デモ |

特 長

|

技術資料

| 対応デバイス | Zynq UltraScale+ ZCU106 | Altera製デバイスについてはお問い合わせ下さい | ||||

| IPコア | データシート | リファレンス・デザイン ドキュメント | デモ手順書 | 無償評価デモ | |

| TLS 1.3 Server 10G IP |

Rev1.00 | Rev1.00 | Rev1.00 | ZCU102 |  |

|

|

|||||

| TLS 1.3 Client 10G IP |

Rev1.04 | Rev1.03 | Rev1.03 | ZCU106 KCU116 |

|

| KR260 | KR260 | Github |

|

||

|

|

|||||

| TLS 1.3 Client 1G IP |

Rev1.01 | AC701 |  |

||

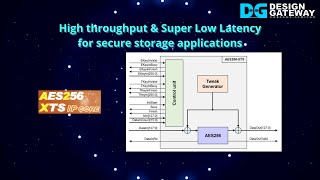

ストレージ・アプリケーション向け セキュリティIP [AES256-XTS IP]

|

超高スループット・低レイテンシーで、セキュアな暗号&認証処理を実現AES256-XTS IP は、XEX Tweakable Block Cipher with Ciphertext Stealing (XTS) を使用した、高度な暗号化規格 (AES) を実装します。ストレージ・デバイス上の機密性の高いデータを保護する必要のあるアプリケーションに最適です。 |

YouTube ビデオ AES256-XTS IP 紹介&デモ動画 |

特 長

|

技術資料

| 資料 | Altera | AMD |

| データシート | Rev1.01 | Rev1.01 |

| リファレンス・デザイン ドキュメント | Rev1.00 | Rev1.00 |

| デザインガイド | Rev1.00 | Rev1.00 |

| デモ手順書 | Rev1.00 | Rev1.00 |

| 無償評価デモファイル | Agilex™ F-series Arria® 10 SX |

ZCU106 |

| AES256-XTS-STG IP は、XEX(XOR Encrypt XOR)可変ブロック暗号を伴う高度な暗号化規格(AES)を実装し、NVMeやSATAストレージ・デバイス上の機密性の高いデータを保護する必要のあるアプリケーションに最適です。NVMe PCIe Gen4 に最適な「2X」、およびGen5に対応した「4X」をラインナップしております。 | |

特 長

YouTube ビデオ AES256-XTS-STG IP 紹介&デモ動画 |

|

技術資料

| 資料 | Altera | AMD |

| AES256-XTS-STG IPデータシート | Rev1.00 | Rev1.01 |

| AES256-XTS-STG IP リファレンス・デザイン ドキュメント |

Rev1.00 | Rev1.00 |

| AES256-XTS-STG IP with NVMe-IP リファレンス・デザイン ドキュメント |

Rev1.01 | Rev1.03 |

| デモ手順書 | Rev1.00 | Rev1.01 |

|

|

||

| 無償評価デモファイル | ||

| AES256-XTS-STG IP (NVMe Gen3 対応) | Arria® 10 SX | |

| AES256-XTS-STG-2X IP (NVMe Gen4 対応) | VCK190 | |

| AES256-XTS-STG-4X IP (NVMe Gen5 対応) | Agilex™ I-series | VPK120 |

| AES256-XTS-STG IP (with NVMe Gen3 IP) | Arria® 10 SX | |

| AES256-XTS-STG-2X IP (with NVMe Gen4 IP) | VCK190 | |

| AES256-XTS-STG-4X IP (with NVMe Gen5 IP) | Agilex™ I-series | VHK158 |

|

|

||

| 無償評価プロジェクト | ||

| AES256-XTS-STG IP (NVMe Gen3 対応) | Github |

|

| AES256-XTS-STG-2X IP (NVMe Gen4 対応) | Github |

|

| AES256-XTS-STG-4X IP (NVMe Gen5 対応) | Github |

|

ネットワーク・アプリケーション向け セキュリティIP [AES256-GCM IP]

|

超高スループット・低レイテンシーで、セキュアな暗号&認証処理を実現AES256-GCM IP コアは、ガロア/カウンター・モード(GCM)をサポートし、256ビット・キー AES暗号処理を実装します。本IPコアは、デザイン・ゲートウェイが提供する、超低遅延TOE10G IP コアと組み合わせて、高性能、低遅延および安全なネットワーク通信を要求するアプリケーションに最適です。 |

YouTube ビデオ AES256-GCM100G IP 紹介&デモ動画 |

特 長

|

技術資料

| IPコア | 資料 | Altera | AMD |

| AES256-GCM 100G IP |

データシート | Rev1.00 | Rev1.00 |

| リファレンス・デザイン ドキュメント | Rev1.00 | Rev1.00 | |

| デモ手順書 | Rev1.00 | Rev1.01 | |

| 無償評価デモファイル | Agilex™ F-series Arria® 10 SX |

ZCU106 KCU116 |

|

| 無償評価プロジェクト | Github |

||

|

|

|||

| AES256-GCM 10G25G IP |

データシート | Rev2.01 | Rev2.01 |

| リファレンス・デザイン ドキュメント | Rev2.01 | Rev2.01 | |

| デモ手順書 | Rev2.01 | Rev2.01 Rev1.00 (KR260) |

|

| 無償評価デモファイル | Agilex™ F-series Arria® 10 SX |

KCU116 ZCU106 KR260 |

|

| 無償評価プロジェクト | Github |

||

|

|

|||

| AES256-GCM 1G IP |

データシート | Rev1.00 | |

| リファレンス・デザイン ドキュメント | Rev1.00 | ||

| デモ手順書 | Rev1.00 | ||

| 無償評価デモファイル | ZCU106 | ||

|

|

|||

| AES-IP共通 | デザインガイド | Rev1.00 | |

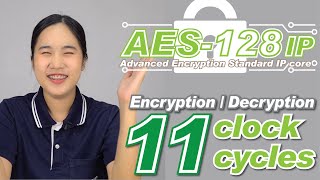

超高スループット 暗号化IP [AES-256SS IP | AES-256 IP | AES-128 IP]

AES-256SS IPは、超高速スループット・超低レイテンシーに特化しており、1クロック・サイクルごとに128ビット・データブロックを計算し、 400MHzで51.2Gbps(1MHzクロックあたり128Mbps)のスループットを提供します。  AES-128 IPは、FIPS-197に準拠し、暗号化と復号化の両方でECBモードをサポートするように設計されています。 AES128-IPは、わずか11クロック・サイクルで128ビット・データブロックを計算し、 500MHzで5.8Gbps(1MHzクロックあたり11.6Mbps)のスループットを提供します。 AES-IPシリーズは、デザイン・ゲートウェイのストレージIPまたネットワークIPとの親和性が高く、超高速データ転送に信頼性の高いセキュリティ機能を実装することで、さらに付加価値の高いアプリケーション開発が可能になります。 |

|

特 長 |

YouTube ビデオ |

|

AES-128 IP 紹介動画 1分でわかる ブログ記事を読む |

技術資料

| IPコア | 資料 | Altera | AMD |

AES-256SS IP |

データシート | Rev1.03 | Rev1.04 |

| リファレンス・デザイン ドキュメント | Rev1.02 | Rev1.02 | |

| 無償評価デモ 手順書 | Rev1.02 | Rev1.02 | |

| 無償評価デモファイル | Agilex™ F-series Arria® 10 SX |

ZCU106 | |

AES-256 IP |

データシート | Rev1.03 | Rev1.04 |

| リファレンス・デザイン ドキュメント | Rev1.03 | Rev1.02 | |

| 無償評価デモ 手順書 | Rev1.03 | Rev1.02 | |

| 無償評価デモファイル | Agilex™ F-series Arria® 10 SX |

ZCU106 | |

AES-128 IP |

データシート | Rev1.03 | Rev1.03 |

| リファレンス・デザイン ドキュメント | Rev1.03 | Rev1.03 | |

| 無償評価デモ 手順書 | Rev1.02 | Rev1.02 | |

| 無償評価デモファイル | Agilex™ F-series Arria® 10 SX |

ZCU106 | |

|

|

|||

| AES-IP共通 | デザインガイド | Rev1.00 | |

超高スループット セキュリティIP [SHA2-IP / SHA-256 IP]

SHA2 IPコアは、SHA-224、SHA-256、SHA-384、SHA-512、SHA-512/224、SHA-512/256のセキュアハッシュアルゴリズムをサポートしています。このコアは、FIPS PUB 180-4 (Federal Information Processing Standard) 仕様に完全準拠しており、安全な通信、パスワード認証、ブロックチェーンのデータ整合性確保などの用途に最適です。

Features |

|

Technical Documents |

| Document Name | Altera | AMD |

| Datasheet | Rev1.00 | Rev1.00 |

| Referrence Design Document | Rev1.00 | Rev1.00 |

| Demo Instruction | Rev1.00 | Rev1.00 |

| Evaluation Demo file | Agilex 7 I-series Arria 10 SX |

KCU116 |

SHA-256 IP は、FIPS 180-4 準拠の セキュア・ハッシュ・アルゴリズム SHA-256 を搭載したIPコアです。本IPコアは、わずか65クロックの超低レンテンシで512ビットのデータ・ブロックを処理し、300MHz動作周波数で 2.362Gbps のスループットを実現します。*暫定値

デザイン・ゲートウェイのストレージIPまたネットワークIPとの親和性が高いため、超高速データ転送に信頼性の高いセキュリティ機能を実装することで、さらに付加価値の高いアプリケーション開発が可能になります。

SHA-256 について

SHA-256は、安全なパスワード・ハッシュ、デジタル署名、SSL / TLS証明書、ビットコイン暗号通貨などのさまざまなアプリケーションで使用されており、最も安全で実質的に解読不可能なハッシュ関数の1つです。

特 長 |

YouTube ビデオ |

|

SHA-256 IP 紹介動画 |

技術資料 |

| 資料 | Altera | AMD |

| データシート | Rev1.00 | Rev1.00 |

| デモ手順書 | Rev1.00 | Rev1.00 |

| 無償評価デモファイル | Arria 10 SX | KCU105 |

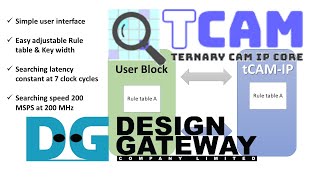

超高速・低遅延検索IP [tCAM IP]

tCAM-IP は超低レイテンシを実現した、高パフォーマンスで柔軟性の高いtCAM(3値連想メモリIPコア)です。tCAM-IP は、わずか7クロックの超低レンテンシで、300 MSPS の超高速連続検索を実行し、40G/100Gイーサネット上では毎秒300,000,000パケットのマッチング/フィルタリングパフォーマンスを実現します。本IPコアは、ネットワークパケットフィルタリング/転送、インテリジェントスイッチ/ルーター、ディープ・パケット・インスペクション(DPI)などの、ネットワークセキュリティアプリケーションに最適です。デザイン・ゲートウェイ製TOE-IPを使用したリファレンス・デザインおよび無償デモファイルを提供致します(お問い合わせ下さい)。 tCAM-IP は超低レイテンシを実現した、高パフォーマンスで柔軟性の高いtCAM(3値連想メモリIPコア)です。tCAM-IP は、わずか7クロックの超低レンテンシで、300 MSPS の超高速連続検索を実行し、40G/100Gイーサネット上では毎秒300,000,000パケットのマッチング/フィルタリングパフォーマンスを実現します。本IPコアは、ネットワークパケットフィルタリング/転送、インテリジェントスイッチ/ルーター、ディープ・パケット・インスペクション(DPI)などの、ネットワークセキュリティアプリケーションに最適です。デザイン・ゲートウェイ製TOE-IPを使用したリファレンス・デザインおよび無償デモファイルを提供致します(お問い合わせ下さい)。 |

|||

| Altera | AMD | ||

| Altera版 tCAM-IPページへ | AMD版 tCAM-IPページへ | ||

YouTube ビデオ |

|||

UDP Packet Filtering & Switching Demo |

tCAM-IP 紹介動画 |

tCAM-IP パフォーマンスデモ (Arria 10 SX) |

tCAM-IP パフォーマンスデモ (KCU116) |

ブログ記事

- What's TCAM?

- TCAM Accelerator for FPGA Based Systems: A High-Performance and Flexible Solution for Various Applications

- Boost Network Efficiency: How tCAM-based packet switching enhances data flow

Alliance Partner

株式会社デザイン・ゲートウェイ

本社東京都小金井市中町3-23-17

R&D

89/26 Amornpan 205 Tower1, 18th floor, Ratchadapisek7 (Nathong) Alley, Ratchadapisek Road, Din Daeng, Bangkok, 10400 THAILAND

AI Lab

Faculty of Engineering, Chulalongkorn University, 12th floor, Engineering 4 Building (Charoenvidsavakham), Phayathai Rd., Wang Mai, Pathumwan, Bangkok, 10330 THAILAND