AES: HW(RTL) vs SW(HLS) comparison

As in the previous article that we talked about AES, you know about how AES works, type of AES and the benefits of using it. This article shows the comparison between using AES Hardware development which is pure logic or Register-Transfer-Level (RTL) and AES Software development on ALVEO card, which is based on High-Level-Synthesis (HLS) Language, in 3 aspects. Flexibility of ip core, base development and size of ip core.

Flexibility of AES Core

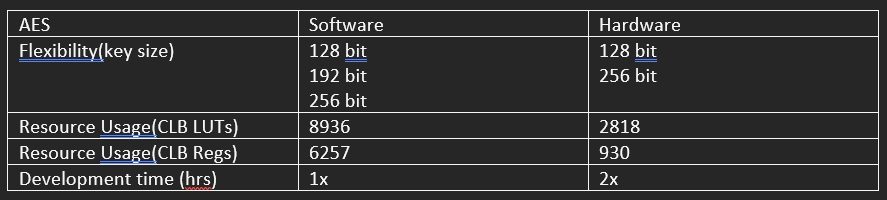

Most AES RTL IP cores are designed and optimized for a specific purpose. For example, the AES256 RTL IP core is designed to support 256 bits key only, meanwhile the AES IP Core running on ALVEO card can be customized to support 128-bit, 192-bit and 256-bit keys.

Implementation: RTL vs HLS

RTL or pure hardware logic is a traditional way to implement logic on FPGA. However, as the growth of the market has pushed manufacturers to improve the methodology to implement FPGA from hardware perspective to software aspect. As a result, AES on ALVEO card is easy to use and friendly to software engineers who just started to work on FPGA. Furthermore, new users do not have to worry about FPGA settings because the software already handles those parameters.

In addition, software engineers would be familiar with the language used in developing projects due to it being based on C/C++ and script languages. Therefore, it helps reduce time of development.

Anyway, RTL implemetation can achieve higher performance than HLS.

Resource usage / Size of IP core

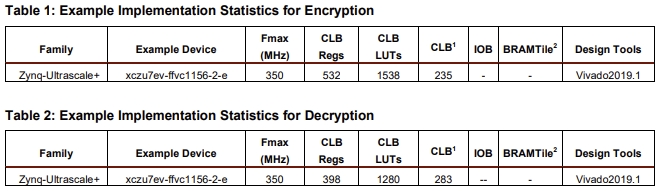

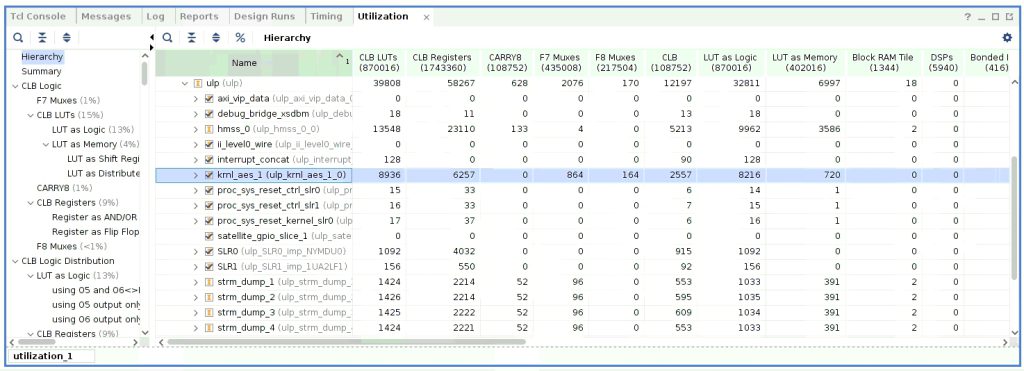

In general, the pure logic ip core is smaller than the ip core generated from the manufacturer, it is also in this case. For example, The AES pure logic from Design Gateway has 128 bit inputs, the same as the AES in the previous article. Even Though, the architecture of the FPGA, a Zynq-Ultrascale+, from pure logic AES of Design Gateway is old. It shows a smaller size than the new architecture, the Alveo card. If the AES pure logic is compiled on the new architecture. It can be smaller than what it is on the old architecture.

Summary

The benefit of using AES over Alveo card is the various types of configuration of AES on Alveocard. Furthermore, the time spent on the development phase might be shorter than developing projects on pure logic design due to the languages used in development. However, the pure logic has its own strong point which is the size. Therefore, users can add more features due to spare spaces from AES. The table below is shown the comparison between AES sw and AES hw from design gateway.

if you are interested in AES hw from design gateway. please visit https://dgway.com/ASIP_E.html