Fully CPU offload for TCP/IP transmission for 10G/25G/40G and up to 100G

TCP Offloading Engine IP Core provides the full hardware TCP/IP protocol stack engine which is the epochal solution implemented without CPU. TCP/IP function is enable by just controlling simple FIFO interfaces. You can choose suitable line rates from 1G-100Gbps. The latest generation of DG’s TOE100G-IP is capable of full TCP/IP offload and able to achieve 12GB/s without CPU required.

Check out our TOE IP Core & see its incredible performance. Watch the performance on YouTube

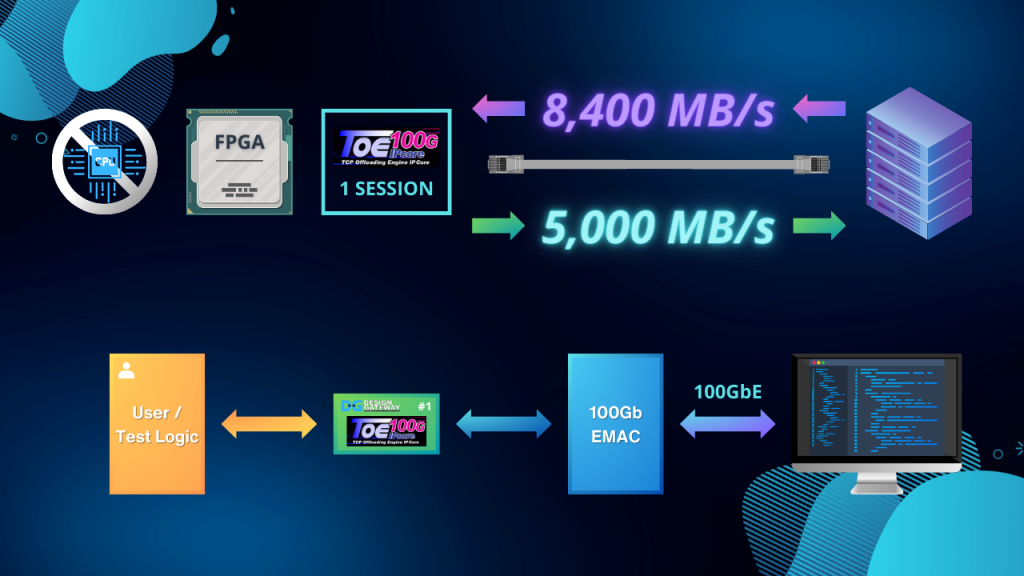

Overcoming the 100G performance bottleneck with TOE100G-IP

To overcome the CPU and main memory bottleneck on host processor systems that limits TCP performance, we propose a solution that uses pure hardware logic TOE IP cores. Our solution can handle single or multiple TCP sessions and achieve near-optimal TCP throughput of almost 10GB/s over 100G bandwidth. Our solution is ideal for applications that require FPGA acceleration for very high data rates over 100G without CPU intervention.

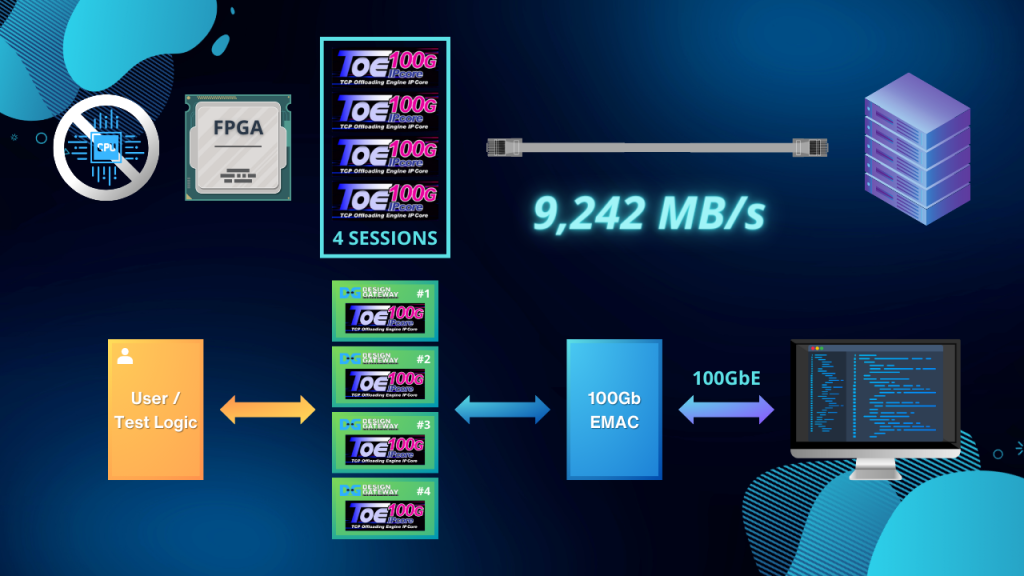

Breaking performance limitation with multi-session TOE100G-IP

TCP performance limitation for single TCP session on Host systems can be overcome by implementing multiple TCP sessions. We provide the multi-sessions TOE100G-IP reference design that can utilize 100G bandwidth more efficiently and able to achieve the TCP transmission performance close to 10GB/s. Our solution is suitable for the application that need very high data rate over 100G without CPU intervention.

Applications

High throughput data streaming over 10G/25G/40G/100G

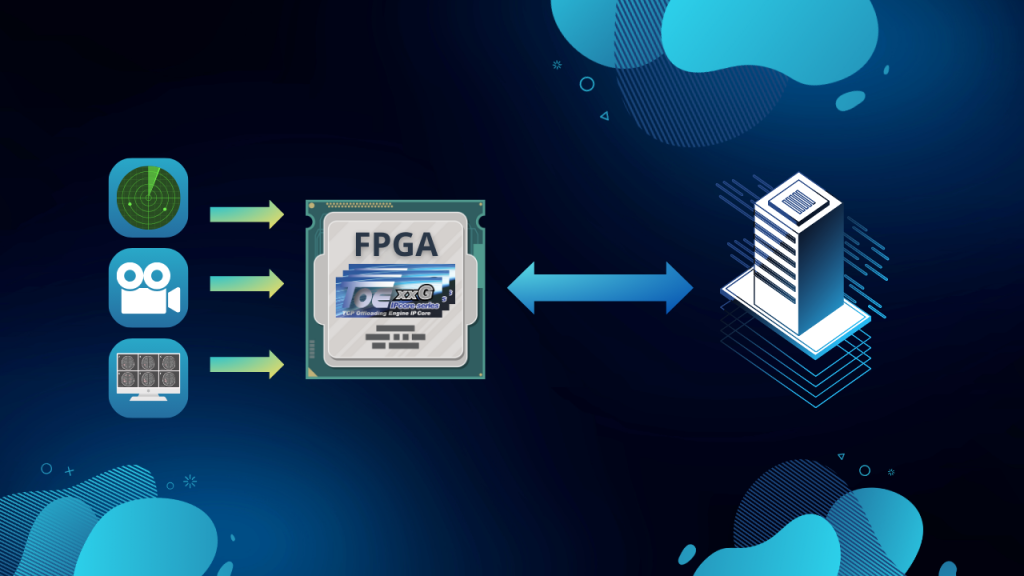

Many applications need to send and receive very high throughput data over the network, such as smart city video surveillance, smart automation control and monitoring, aerospace and defense radio or radar signals, and healthcare medical images. Our TOE-IP Core can support different ethernet speeds, such as 10G, 25G, 40G, and 100G, depending on your FPGA-based application needs.

Multiple data channel transmission between FPGA & Host systems

FPGA-based applications often use FPGA to capture data from multiple channels and send it over the network. We provide a proven reference design for multi-session TOE-IP that can help you reduce your development time and achieve very high TCP performance in your systems.

Conclusion

In conclusion, the TOE100G-IP Core from Design Gateway provides a full offload engine for processing TCP/IP packets without the need for a CPU or external memory. Its pure hardware logic design enables high performance and maximum TCP/IP throughput of 100 Gbit Ethernet while keeping the FPGA resource usage to a minimum. Our solution is suitable for full TCP Offload and TCP Accelerator for FPGA-based applications for both SmartNIC and Embedded systems.

Learn more about our solutions here

Learn more : TOExxG IP for Xilinx

Learn more : TOExxG IP for Intel