TOE-IP core Series200GbE is available on Agilex™ 7 I-Series!!

Features | Block diagram | Document Download| Applications

Technical document update information

Technical document update information

TOE100G-IP Multi-Session Demo : Picture Story Blog

TOE100G-IP Multi-Session Demo : Picture Story Blog

TOE100G-IP introduction & Application example video clip on YouTube. Watch

TOE100G-IP & Suitable applications : Picture Story Blog

TOE100G-IP & Suitable applications : Picture Story Blog

Blog Article: Proven 10G TCP Offload Engine IP Core for Industrial, Medical,

and Test & Measurement Applications

Blog Article: Proven 10G TCP Offload Engine IP Core for Industrial, Medical,

and Test & Measurement Applications

TCP Offloading Engine IP core (TOE200G/100G/40G/25G/10G/1G-IP) is the epochal solution implemented without CPU. Generally, TCP processing is so complicated that expensive high-end CPU

is required. TOE-IP core series built by pure hardwired logic can take

place of such extra CPU for TCP protocol management. This IP product includes

reference design for Altera FPGAs. It helps you to reduce development time.

DesignGateway provide demo file for Altera FPGA boards. You can evaluate

TOE-IP on real board before purchasing.

Features

|

|

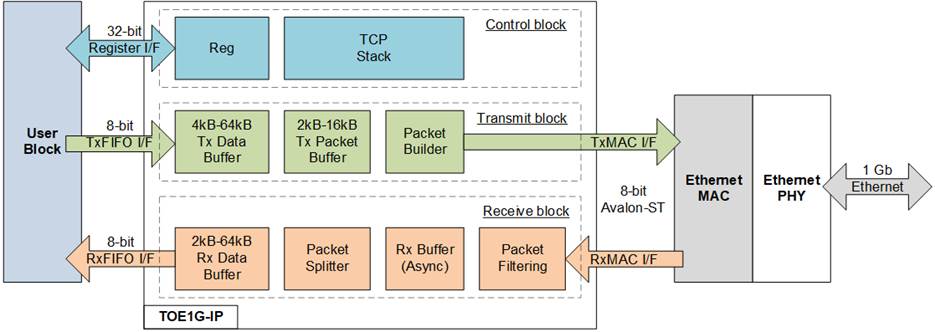

Block diagram

TOE200GADV-IP |

TOE100G-IP |

|

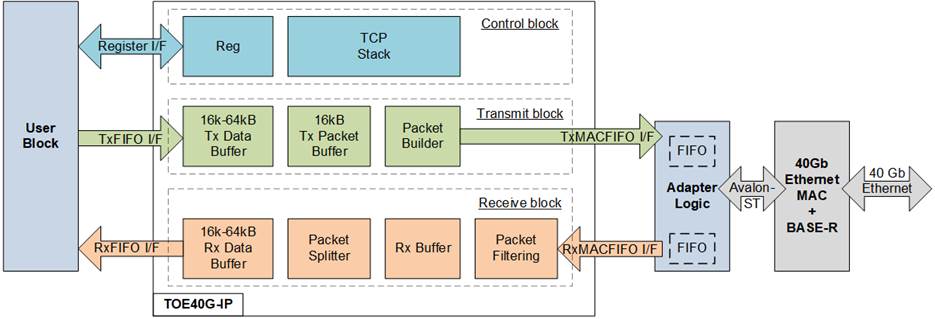

TOE40G-IP |

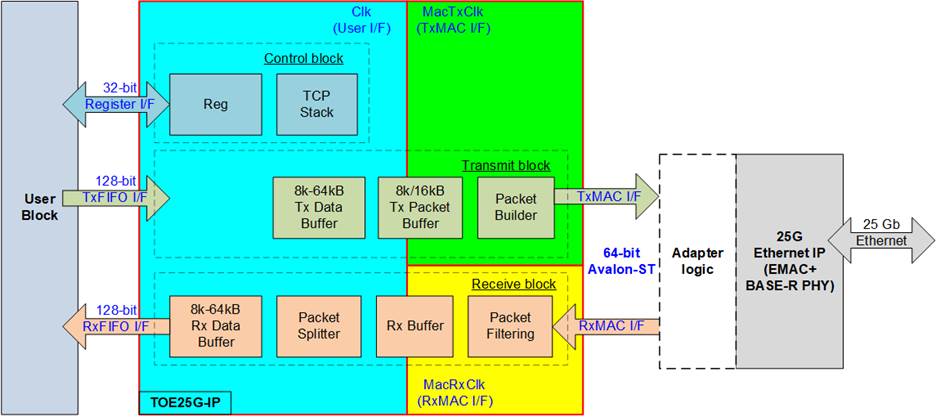

TOE25G-IP |

|

TOE10G-IP |

TOE1G-IP |

|

Document & Demo file download

Sales Materials

| Document Name | Update (Revision) |

| DG IP cores Brochure | Rev2026Q1 |

| TOE-IP core series Presentation | Rev2.0AE |

| 10GEMAC-IP for TOE10G-IP Presentation | Rev1.0AE |

| Introduction Video |

TOE25G-IP Introduction |

| Blog Articles |

- |

Technical Documents & Free Evaluation file

| Devices | Agilex™ 7 I-Series/F-Series, Stratix®10 MX/TX | |||||

| IP core & Option | Datasheet | Reference Design Document | Demo Instruction | FPGA Board Set up Document | Free Evaluation file | |

TOE200GADV-IP TOE200GADV-IP |

Rev2.00 | Rev2.00 | Rev2.00 | Rev2.00 | Agilex™ 7 I-Series |

|

TOE100GADV-IP TOE100GADV-IP |

Agilex™ 7 I-Series |

|||||

TOE100G-IP TOE100G-IP |

Rev2.0 | Rev2.1 | Rev1.2 | Rev3.2 | Agilex™ 7 F-Series Stratix 10 MX Stratix 10 TX |

|

| 4 Session demo | Rev1.0 | Rev1.0 | Rev3.2 | Stratix 10 TX | ||

| Devices | Altera PAC, Arria®10 GX | |||||

TOE40G-IP TOE40G-IP |

Rev1.1 | Rev1.0 | Rev1.0 | Arria 10 GX |  |

|

| Altera PAC | Rev1.0 | Rev1.0 | Altera PAC |  |

||

| Devices | Agilex™ 7 F-Series, Stratix®10 GX | |||||

TOE25G-IP TOE25G-IP |

Rev1.3 | Rev1.2 | Rev1.3 | Rev2.2 | Agilex-F Stratix 10 GX Stratix 10 MX |

|

| Devices | IntelPAC, Stratix® 10 GX, Arria® 10 SX, Arria® 10 GX, Cyclone® 10 GX | |||||

| IP core & Option | Datasheet | Reference Design Document | Demo Instruction | FPGA Board Set up Document | Free Evaluation file | |

TOE10G-IP TOE10G-IP |

Rev2.00 | Rev2.00 Rev1.0 (PAC) |

Rev2.04 Rev1.0 (PAC) |

Rev3.2 | Agilex 5 Sulfur Altera PAC Stratix 10 GX Stratix 10 MX Arria 10 SX Arria 10 GX Cyclone 10 GX |

|

| 10G EMAC-IP | Rev1.2 | Rev1.0 | Rev1.0 | Rev3.2 | Cyclone 10 GX | |

| 2 port demo | Rev1.01 | Rev1.0 | Rev3.2 | Arria 10 GX | ||

| Multi Session | Rev1.0 | Rev1.0 | Rev3.2 | Arria 10 SX | ||

| Devices | Arria® 10 SX, Cyclone® 10 GX, Arria® V GX, Cyclone® V E, Stratix® IV GX | |||||

TOE1G-IP TOE1G-IP |

Rev3.02 | Rev2.00 | Rev2.02 | Rev2.02 | Arria 10 SX Arria 10 GX Arria V GX Cyclone V E |

|

| 2 port demo | Rev1.0 | Rev1.0 | Cyclone 10 GX | |||

| FTP server demo with SATA-IP | Rev1.0 | Rev1.0 | Cyclone 10 GX |  |

||

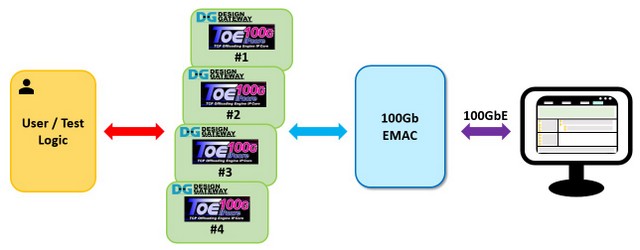

Muiti-Session Reference design to improve TCP communication with PC

| The TOE100G-IP core multiple sessions reference design is implemented to utilize 100G Ethernet channel effectively and maximize

TCP throughput by multiple instances of TOE100G-IP. It impro It significantly improves the performance of TCP communication dropped due to the restrictions on the PC side without any expensive enterprise grade server. |

|

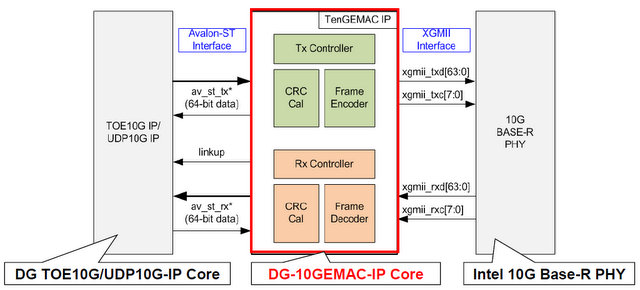

Super low-latency DG 10GbE MAC core for TOE10G-IP

DG 10GbE MAC core implements the MAC layer for TOE10G-IP core and fully compatible with

Altera MAC. It has many advantages.

|

|

| DG 10GEMAC-IP | Altera 10GEMAC | |

| Tx latency (clk freq.=156.25MHz) | 19.2ns (3clk) | 76.8ns (12clk) |

| Rx latency (clk freq.=156.25MHz) | 44.8ns (7clk) | 83.2ns (13clk) |

| ALMs | 1362 | 1617 |

| Registers | 1259 | 3015 |

| Block Memory | 0 | 2320 |

Application Examples

TOE100G-IP is the best solution for the system which has to process big data with minimum time.- Multi-channel HD video streaming

- Autonomous driving development system which consist of multi channel of Camera, Lidar, Radar and sensors

- Medical scanners such as MRI and PET scan

TOE100G-IP introduction & Application example video clip on YouTube. Watch

TOE10G-IP Real-World Applications

.jpg) Pipeline inspection system |

.jpg) CT Scan |

||

.png) Satellite Tracking System |

.png) Semiconductor Manufacturing |

.png) Ophthalmic Medical |

.png) Video equipment |

.jpg) Scanning sonar (fish detection system) |

.jpg) Radar system |

.jpg) Industrial printer |

.jpg) Wireless communication system |

Alliance Partner

Design Gateway Co., Ltd.

Head Office3-23-17 Naka-cho, Koganei, Tokyo, JAPAN

R&D

89/26 Amornpan 205 Tower1, 18th floor, Ratchadapisek7 (Nathong) Alley, Ratchadapisek Road, Din Daeng, Bangkok, 10400 THAILAND

AI Lab

Faculty of Engineering, Chulalongkorn University, 12th floor, Engineering 4 Building (Charoenvidsavakham), Phayathai Rd., Wang Mai, Pathumwan, Bangkok, 10330 THAILAND