TOE-IP core SeriesSupport 200GbE, Multi-session & AXI4 interface

TCP Offloading Engine IP core (TOE200G/100G/40G/25G/10G/1G-IP) is the epochal solution implemented without CPU. Generally, TCP processing is so complicated that expensive high-end CPU

is required. TOE-IP core series built by pure hardwired logic can take

place of such extra CPU for TCP protocol management. This IP product includes

reference design for AMD FPGA. It helps you to reduce development time.

DesignGateway provide free demo file for AMD FPGA boards. You can evaluate

TOE-IP on real board before purchasing.

Features

|

|

Block diagram

TOE200GADV-IP |

TOE100GADV-IP |

TOE100G-IP |

TOE40G-IP |

TOE25G-IP |

|

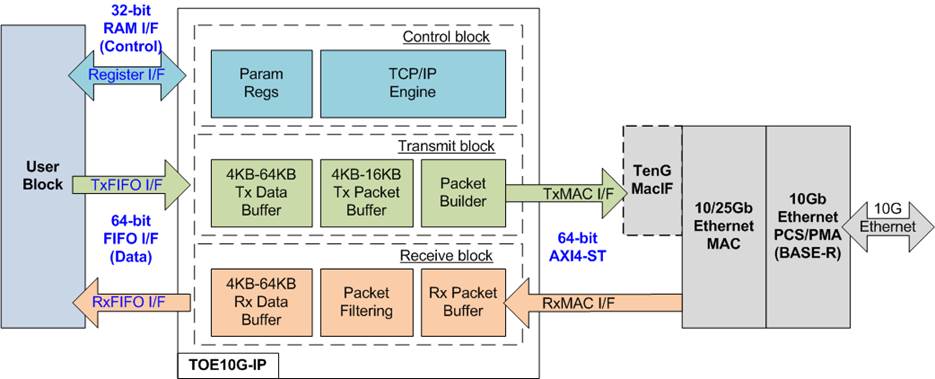

TOE10G-IP |

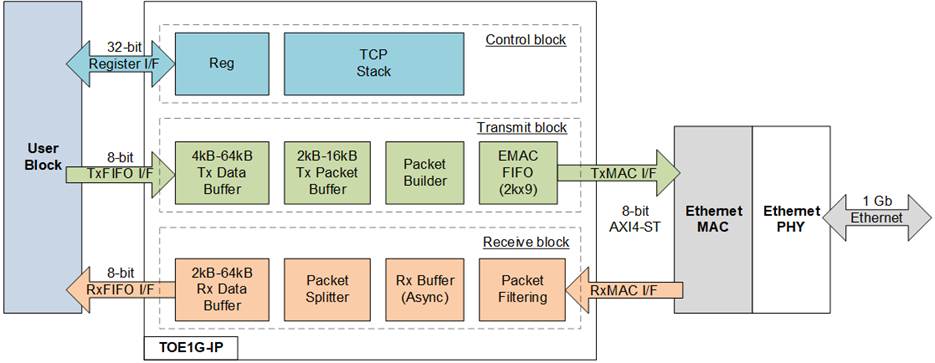

TOE1G-IP |

Document & Demo bit file download

Sales Materials

| Document name | Update (Revision) |

| DG IP cores Brochure | Rev2025Q4EX |

| TOE-IP core series Presentation | Rev2.0XE |

| 10G25GEMAC-IP for TOE25G/10G-IP Presentation | Rev1.0 |

YouTube & Blogs

| IP core |  |

|

|

| Introduction Videos |

|

|

|

| Blog Articles |

|||

| Digikey Article Library | |||

Technical Documents & Free Evaluation file

| Devices | Alvero U250, Versal Premium VPK120, Versal AI Core VCK190, Versal HBM VHK158, Kintex UltraScale+ KCU116 | |||||

| IP core & Option | Datasheet | Reference Design Document | Demo Instruction Document | FPGA Board Setup | Free Evaluation demo file | |

TOE200GADV-IP |

Rev1.00 | Rev2.00 | Rev1.00 | VPK120 | VHK158 |  |

|

TOE100GADV-IP |

Rev1.0 | Rev1.0 | Rev1.0 | Rev3.03 | VCK190 | KCU116 |  |

TOE100G-IP |

Rev2.0 | Rev2.0 | Rev1.2 | Rev3.03 | VCK190 U250 KCU116 Silicom KU15P |

|

| exFAT2-IP FTP Server Demo |

Rev1.0 | Rev1.01 | Rev1.00 | VCK190 |  |

|

| 4 Session demo | Rev1.1 | Rev1.0 | Rev3.03 | KCU116 |  |

|

| 2 Port demo | Rev1.1 | Rev1.0 | Rev3.03 | |||

| DMA on Alveo card |

Rev1.0 | Rev1.0 | Rev1.0 | U250 U50 |

|

|

| Silicom NIC card | Rev1.0 | Rev1.0 | Rev1.0 | Silicom KU15P |  |

|

| Devices | Zynq Ultrascale+ ZCU102 / ZCU106, Kintex Ultrascale KCU105 | |||||

TOE40G-IP |

Rev1.2 | Rev1.0 | Rev1.2 | - | KCU105 ZCU102 ZCU106 |

|

| Devices | Versal AI Core VCK190 Zynq Ultrascale+ ZCU111, Virtex UltraScale+ VCU118, Kintex UltraScale+ KCU116 |

|||||

TOE25G-IP |

Rev1.5 | Rev1.4 | Rev1.3 | Rev2.06 | VCK190 | VCU118 KCU116 | ZCU111 |

|

| 25GEMAC/PCS +RS-FEC IP |

Rev1.01 | Rev1.0 | Rev1.0 | KCU116 |  |

|

| 10G25G EMAC-IP | Rev1.04 |  |

||||

| 4 Session demo | Rev1.0 | Rev1.0 | Rev2.06 | VCK190 | ||

| 2 Port demo | Rev1.0 | Rev1.0 | Rev2.06 | |||

| FTP Server demo with NVMe-IP & exFAT-IP | Rev1.0 | Rev1.0 | Rev1.0 | KCU116 | ||

| Devices | Versal AI Core VCK190 Zynq UltraScale+ ZCU106/ZCU102, Virtex UltraScale+ VCU118, Kintex UltraScale KCU105 |

|||||

| IP core & Option | Datasheet | Reference Design Document | Demo Instruction Document | FPGA Board Setup | Free Evaluation demo file | |

TOE10G-IP |

Rev2.03 | Rev2.00 | Rev2.04 | Rev3.07 | VCK190 | VCU118 ZCU106 | ZCU102 KCU116 | KCU105 ZC706 |

|

| VC707/KC705 Half Duplex Rev1.01 Full DuplexRev1.0 |

VC707/KC705 Half Duplex Rev1.03 Full DuplexRev1.1 |

VC707 KC705 |

|

|||

| 10G25G EMAC-IP | Rev1.04 |  |

||||

| 2 port demo | Rev1.00 | Rev1.0 | Rev3.07 | KCU105 | ||

| FTP Server demo with NVMe-IP & exFAT-IP | Rev1.2 | Rev2.0 | Rev2.1 | ZCU102 | ZCU106 KCU105 |

||

| Multi Session | Rev1.0 | Rev1.0 | ZC706 KC705 VC707 |

|||

| Devices | Zynq-7000 ZC706, Virtex-7 VC707, Kintex-7 KC705, Artix-7 AC701 | |||||

TOE1G-IP |

Rev3.01 | Rev2.00 | Rev2.02 | Rev3.01 | KCU105 KC705 | AC701 |

|

| Multi Session | Rev1.0 | Rev1.0 | KC705 | |||

| 2 port demo | Rev1.4 | Rev1.3 | KCU105 | ZC706 KC705 | AC701 |

|||

| FTP server demo | Rev1.1 | Rev1.1 | ZC706 KC705 |

|

||

Performance

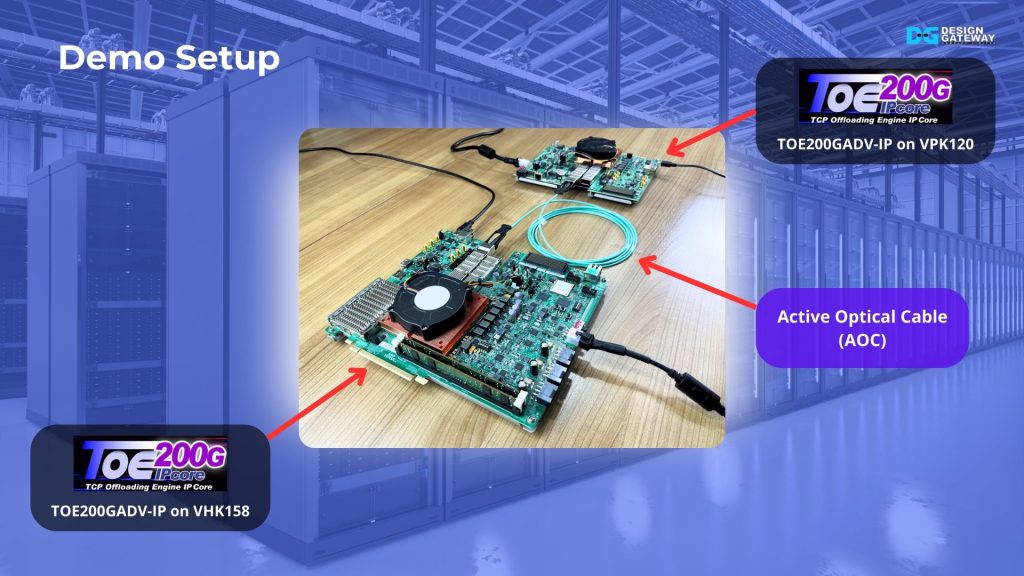

FPGA-FPGA Demo

|

TOE200GADV-IP achieves 24GB/sec with AMD VHK158 and VPK120. The performance demo on Youtube |

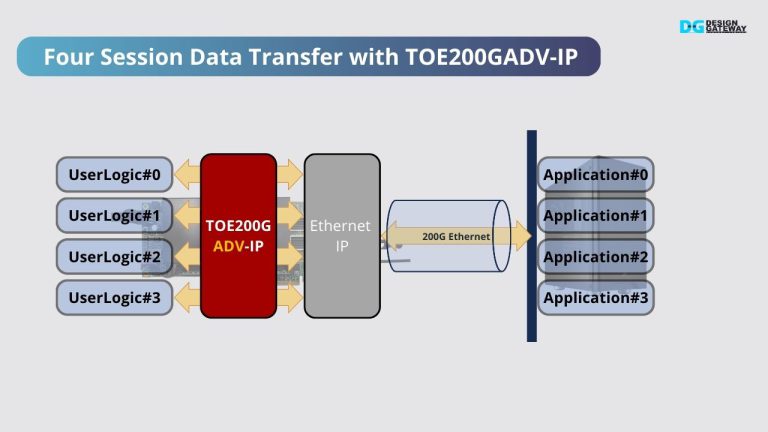

Muiti-Session Demo

|

The TOE200GADV-IP supports up to four simultaneous sessions, minimizing performance degradation caused by PC bottlenecks. It is ideal for applications that require high data throughput, such as data and video streaming, cloud computing, data centers, and high-performance computing. |

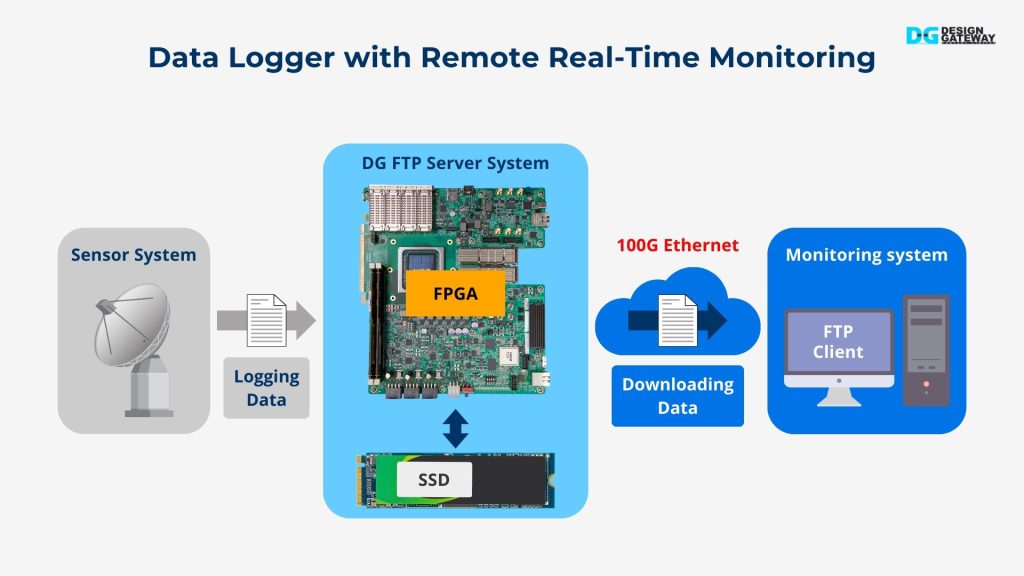

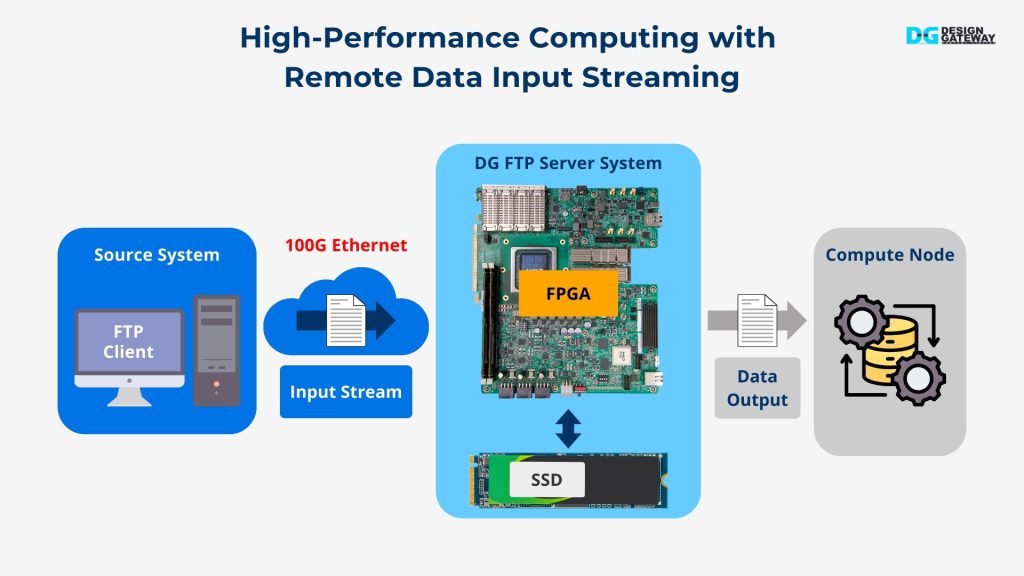

100GbE FTP Server Demo

Data Logger with Remote Real-Time Monitoring  High-Performance Computing with Remote Data Input Streaming |

In aerospace and advanced research fields, remote data logging and high-speed

long-distance data transfer are often required. By leveraging 100GbE fiber connectivity, real-time analysis in high-performance computing and

secure storage in data centers can be achieved. 100GbE high-speed connections are crucial for mission-critical applications that

demand both data integrity and speed. To meet these needs, we offer a practical,

application-level reference design combining the TOE100G-IP core with muNVMe-IP and exFAT2-IP, significantly reducing development time.

|

PacketMover Performance Demo

|

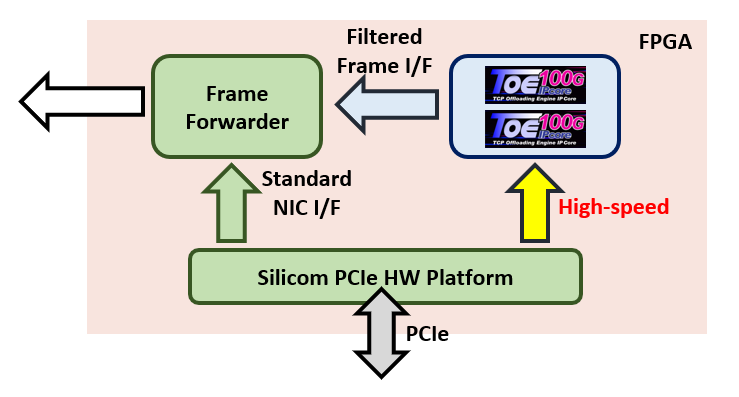

A 100G data transfer using TCP between a Linux host's memory and a 100G Ethernet connection can be achieved by utilizing the TOE100G-IP along with Silicom's PacketMover framework on their fb2CG@KU15P Kintex UltraScale+ FPGA Card. |

|

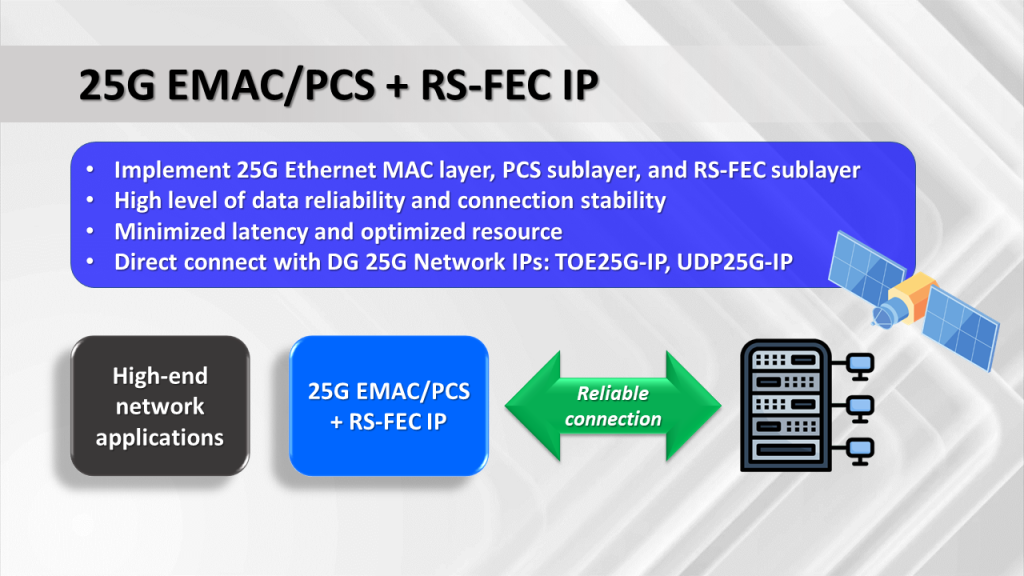

25GEMAC/PCS+RS-FEC IP

|

The 25G EMAC/PCS + RS-FEC IP core provides a comprehensive implementation of the physical layer, including

the Ethernet MAC layer, Physical Coding sublayer (PCS), and RS-FEC sublayer.

The incorporation of RS-FEC in the system significantly enhances data reliability

and connection stability, making it an ideal option for applications that

prioritize data reliability. |

|

|

KEY FEATURES

|

|

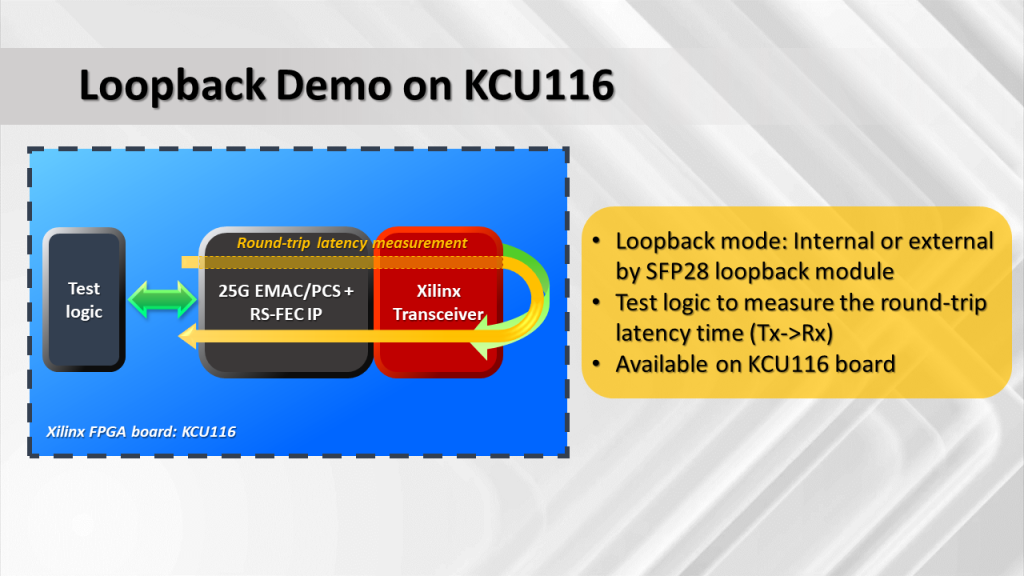

Loopback Demo is available on KCU116

The demo is ready available for IP core evaluation. This demo aims to provide a simple yet comprehensive demonstration of the capabilities of The 25G EMAC/PCS + RS-FEC IP, connected to the AMD Transceiver, which enables the physical and medium of the 25G Ethernet system. The round-trip latency time is 471.04 ns. (packet size 9014 bytes) |

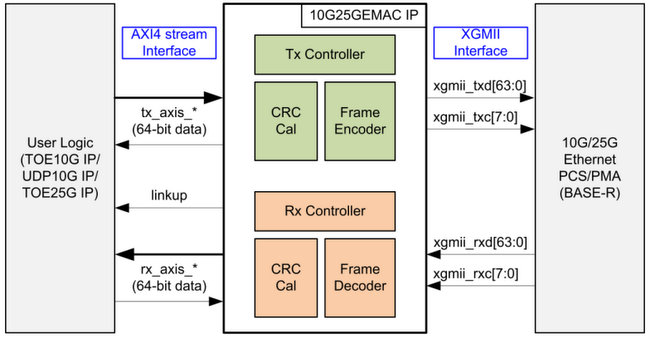

Super low-latency DG 10G25G EMAC IP core

DG 10G25GEMAC core implements the MAC layer for TOE10G-IP core and highly compatible with

AMD MAC. It has many advantages.

|

|

| DG 10G25GEMAC-IP | AMD 10GEMAC | |

| Tx latency (clk freq.=156.25MHz) | 19.2ns (3clk) | 19.2ns (3clk) |

| Rx latency (clk freq.=156.25MHz) | 44.8ns (7clk) | 115.2ns (18clk) |

| CLB LUTs | 1873 | 3498 |

| CLB Registers | 1072 | 3291 |

| CLB | 326 | 694 |

Application Examples

TOE100G-IP is the best solution for the system which has to process big data with minimum time.- Multi-channel HD video streaming

- Autonomous driving development system which consist of multi channel of Camera, Lidar, Radar and sensors

- Medical scanners such as MRI and PET scan

TOE100G-IP introduction & Application example video clip on YouTube. Watch

TOE10G-IP Real-World Applications

.jpg) Pipeline inspection system |

.jpg) CT Scan |

||

.png) Satellite Tracking System |

.png) Semiconductor Manufacturing |

.png) Ophthalmic Medical |

.png) Video equipment |

.jpg) Scanning sonar (fish detection system) |

.jpg) Radar system |

.jpg) Industrial printer |

.jpg) Wireless communication system |

Alliance Partner

Design Gateway Co., Ltd.

Head Office3-23-17 Naka-cho, Koganei, Tokyo, JAPAN

R&D

89/26 Amornpan 205 Tower1, 18th floor, Ratchadapisek7 (Nathong) Alley, Ratchadapisek Road, Din Daeng, Bangkok, 10400 THAILAND

AI Lab

Faculty of Engineering, Chulalongkorn University, 12th floor, Engineering 4 Building (Charoenvidsavakham), Phayathai Rd., Wang Mai, Pathumwan, Bangkok, 10330 THAILAND