Fintech向け低遅延ネットワークIPSuper Low Latency IP for Fintech

特長┃資料ダウンロード┃アプリケーション例

Design Gatewayの低遅延ネットワークIPは、高頻度取引(HFT)や高速取引(HST)等の超低レイテンシを要求するFintechアプリケーションに対応するために専用に設計されています。

またシステム固有の要件に合わせて、低レイテンシネットワークIPコアとFPGAロジックのカスタマイズのトータルソリューションを提供致します。 お問い合わせ下さい

Design Gatewayの低遅延ネットワークIPは、高頻度取引(HFT)や高速取引(HST)等の超低レイテンシを要求するFintechアプリケーションに対応するために専用に設計されています。

またシステム固有の要件に合わせて、低レイテンシネットワークIPコアとFPGAロジックのカスタマイズのトータルソリューションを提供致します。 お問い合わせ下さい

デザイン・ゲートウェイが提供するFintech向けネットワークIPとカスタマイズ対応可能なブロック

仕様の詳細については お問い合わせ下さい

Design Gatewayの低遅延ネットワークIPは、高頻度取引(HFT)や高速取引(HST)等の超低レイテンシを要求するFintechアプリケーションに対応するために専用に設計されています。

またシステム固有の要件に合わせて、低レイテンシネットワークIPコアとFPGAロジックのカスタマイズのトータルソリューションを提供致します。 お問い合わせ下さい

Design Gatewayの低遅延ネットワークIPは、高頻度取引(HFT)や高速取引(HST)等の超低レイテンシを要求するFintechアプリケーションに対応するために専用に設計されています。

またシステム固有の要件に合わせて、低レイテンシネットワークIPコアとFPGAロジックのカスタマイズのトータルソリューションを提供致します。 お問い合わせ下さい特長

Low Latency 10GEMAC-IP (LL10GEMAC-IP)

|

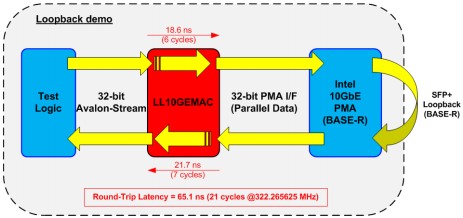

LL10GEMAC-IP ループバック・デモ |

Low Latency UDP10GRx-IP

|

Low Latency TOE10G-IP

|

|

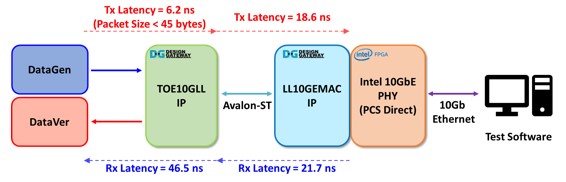

Fintech向けアプリケーション例 ブロック図

デザイン・ゲートウェイが提供するFintech向けネットワークIPとカスタマイズ対応可能なブロック

- UDP10GTx / UDP10GRx, TOE10GLL, LL10GEMAC

- カスタマイズ対応

資料ダウンロード

| 資料 | Update (Revision) | |

| プレゼンテーション | 1.1J | |

| ブロシュアー | Rev2025Q1JA | |

| LL 10GEMAC-IP | データシート | Rev1.1 |

| リファレンス・デザイン ドキュメント | Rev1.0 | |

| FPGA ボードセットアップ | Rev1.0 | |

| ループバックデモ手順書 | Rev1.0 | |

| 評価デモファイル | Arria 10 GX | |

| LL UDP10GRx-IP | データシート | Rev1.0 |

| リファレンス・デザイン ドキュメント | Rev1.0 | |

| FPGA ボードセットアップ | Rev1.0 | |

| デモ手順書 | Rev1.2 | |

| 評価デモファイル | Arria 10 GX | |

| TOE10GLL-IP | データシート | Rev1.1 |

| リファレンス・デザイン ドキュメント | Rev1.1 | |

| デモ手順書 | Rev1.0 | |

| 評価デモファイル | Arria 10 GX |

Alliance Partner

株式会社デザイン・ゲートウェイ

本社東京都小金井市中町3-23-17

R&D

89/26 Amornpan 205 Tower1, 18th floor, Ratchadapisek7 (Nathong) Alley, Ratchadapisek Road, Din Daeng, Bangkok, 10400 THAILAND

AI Lab

Faculty of Engineering, Chulalongkorn University, 12th floor, Engineering 4 Building (Charoenvidsavakham), Phayathai Rd., Wang Mai, Pathumwan, Bangkok, 10330 THAILAND