Super Low Latency Networking IPfor fintech

Features┃Document Download┃Applications

Design Gateway’s Low Latency Networking IP is designed from the ground

up for very low latency requirements. Especially, FinTech applications

such as high-frequency trading (HFT), high speed trading (HST), Market

Data Processing and Tick-to-Trade (T2T) systems. We can provide total solutions

for low latency Networking IP cores and FPGA logic customization for application

specific requirements. Contact Us

Design Gateway’s Low Latency Networking IP is designed from the ground

up for very low latency requirements. Especially, FinTech applications

such as high-frequency trading (HFT), high speed trading (HST), Market

Data Processing and Tick-to-Trade (T2T) systems. We can provide total solutions

for low latency Networking IP cores and FPGA logic customization for application

specific requirements. Contact Us

Design Gateway Provides optimized IP & Customized service for Fintech

For more detail, please Contact Us

Design Gateway’s Low Latency Networking IP is designed from the ground

up for very low latency requirements. Especially, FinTech applications

such as high-frequency trading (HFT), high speed trading (HST), Market

Data Processing and Tick-to-Trade (T2T) systems. We can provide total solutions

for low latency Networking IP cores and FPGA logic customization for application

specific requirements. Contact Us

Design Gateway’s Low Latency Networking IP is designed from the ground

up for very low latency requirements. Especially, FinTech applications

such as high-frequency trading (HFT), high speed trading (HST), Market

Data Processing and Tick-to-Trade (T2T) systems. We can provide total solutions

for low latency Networking IP cores and FPGA logic customization for application

specific requirements. Contact UsFeatures

Low Latency 10GEMAC-IP (LL10GEMAC-IP)

|

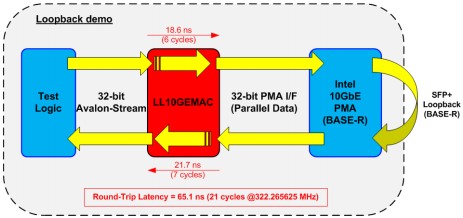

LL10GEMAC-IP Loopback Demo |

Low Latency UDP10G Rx-IP

|

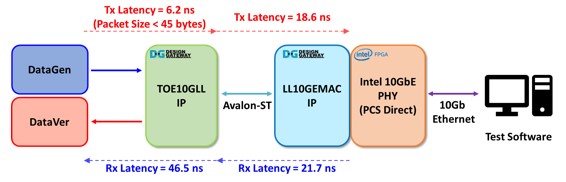

Low Latency TOE10G-IP (TOE10GLL-IP)

|

|

|

Example FinTech Implementation on FPGA

Design Gateway Provides optimized IP & Customized service for Fintech

- UDP10GTx / UDP10GRx, TOE10GLL, LL10GEMAC

- Customized service

Document download

| Document name | Update (Revision) | |

| Presentation | 1.0E | |

| Brochure | 2.6EA | |

| LL 10GEMAC-IP | Datasheet | Rev1.1 |

| Reference Design Document | Rev1.0 | |

| FPGA board Setup Document | Rev1.0 | |

| Loopback Demo Instruction | Rev1.0 | |

| Evaluation demo file | Arria 10 GX | |

| LL UDP10GRx-IP | Datasheet | Rev1.0 |

| Reference Design Document | Rev1.0 | |

| FPGA board Setup Document | Rev1.0 | |

| Demo Instruction | Rev1.2 | |

| Evaluation demo file | Arria 10 GX | |

| TOE10GLL-IP | Datasheet | Rev1.1 |

| Reference Design Document | Rev1.1 | |

| Demo Instruction | Rev1.0 | |

| Evaluation demo file | Arria 10 GX |

Alliance Partner

Design Gateway Co., Ltd.

Head Office3-23-17 Naka-cho, Koganei, Tokyo, JAPAN

R&D

89/26 Amornpan 205 Tower1, 18th floor, Ratchadapisek7 (Nathong) Alley, Ratchadapisek Road, Din Daeng, Bangkok, 10400 THAILAND

AI Lab

Faculty of Engineering, Chulalongkorn University, 12th floor, Engineering 4 Building (Charoenvidsavakham), Phayathai Rd., Wang Mai, Pathumwan, Bangkok, 10330 THAILAND