CPU-less QUIC Offload IP core for FPGA Acceleration

Features┃Advantage┃Document Download┃Performance Comparison┃Applications

Please receive technical document update from DG News Letter. Subscribe to DG News

Please receive technical document update from DG News Letter. Subscribe to DG News

Technical document update page

Technical document update page

.jpg)

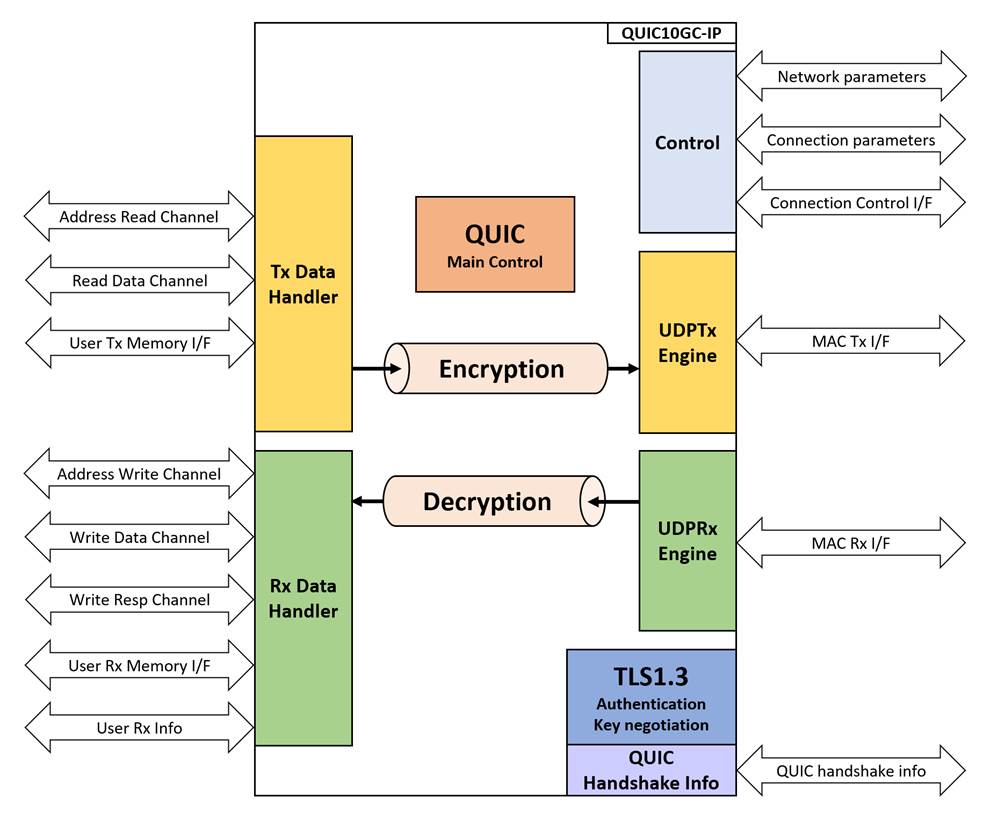

QUIC Client 10Gbps IP Core (QUIC10GC-IP) は、TLS 1.3セキュリティを備えたQUICプロトコルを、FPGAベースのクライアント・アプリケーション向けに、完全ハードウェア・ロジックで提供します。本IPコアは、TLS 1.3ハンドシェイク処理、ペイロードデータの暗号化/復号化、QUICレイヤーとUDP/IPレイヤーの管理といった複雑な処理からCPUを完全にオフロードします。

QUICとは?QUICはTCP/UDPに代わる次世代のトランスポート層プロトコルです。従来のTCPプロトコルのいくつかの欠点を克服し、より高速で信頼性の高い通信を提供します。

|

なぜQUIC?今日のデジタル環境では、従来のTCP/IPプロトコルではヘッドオブライン・ブロッキングなどにより、データの遅延や非効率が発生しています。QUICプロトコルはこれらの問題を解決し、中断のないデータ伝送、輻輳(ふくそう)制御の改善、TCP以上のセキュリティを提供します。これにより、ネットワーク効率が大幅に向上し、より迅速で信頼性の高い通信が可能になります。 |

Features

|

Block diagram * Click to show more detail Introduction Video Enhancing Internet Performance & Security with QUIC10GC-IP |

QUIC Protocol Advantage

Document download

Technical Documents

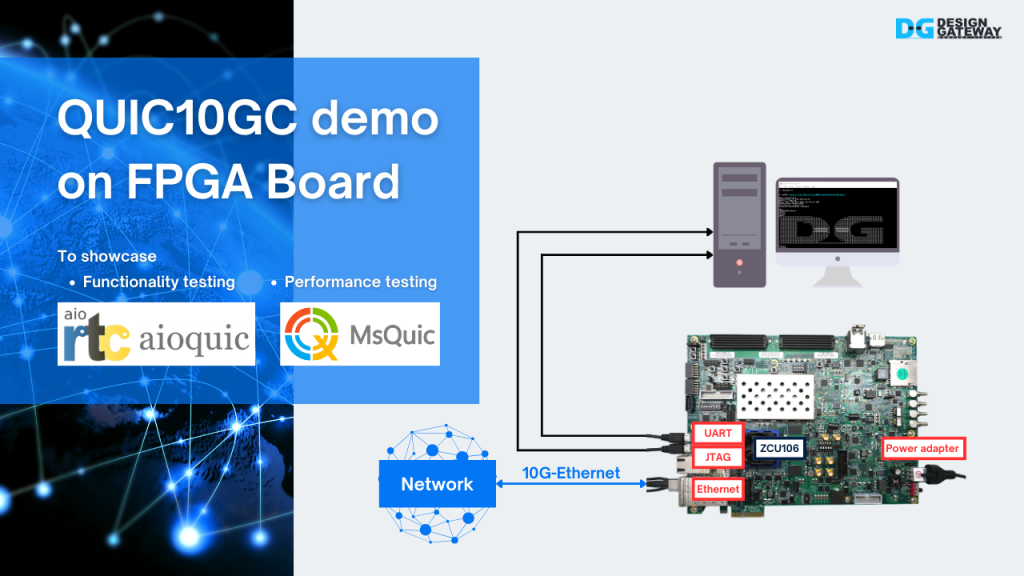

| Support Devices | Zynq UltraScale+ ZCU106 | for other device, please contact us | ||||

| IP core | Datasheet | Reference Design Document | Demo Instruction Document | Free Evaluation demo file | |

| QUIC Client 10G IP |

Rev1.00 | Rev1.00 | Rev1.00 | ZCU106 |  |

| QUIC Server 10G IP |

Rev1.00 | Rev1.00 | Rev1.00 | KCU116 |  |

Performance Comparison

CPU負荷0%! 10Gbps帯域をフルに活用

.jpg)

QUIC-IPは、MsQuic等各種サーバーとの通信速度を向上させ、CPUに負荷をかけることなく10Gbpsイーサネットのフルスピードを実現します。

Free Bit file for evaluation

|

Free evaluation demo is available on AMD FPGA boards. Download Performance Demo Video: |

クリティカル・アプリケーションに最適なソリューション

お問合せください。Alliance Partner

株式会社デザイン・ゲートウェイ

本社東京都小金井市中町3-23-17

R&D

89/26 Amornpan 205 Tower1, 18th floor, Ratchadapisek7 (Nathong) Alley, Ratchadapisek Road, Din Daeng, Bangkok, 10400 THAILAND

AI Lab

Faculty of Engineering, Chulalongkorn University, 12th floor, Engineering 4 Building (Charoenvidsavakham), Phayathai Rd., Wang Mai, Pathumwan, Bangkok, 10330 THAILAND

.jpg)

.jpg)

.jpg)

.jpg)

.jpg)

.jpg)