25G Ethernet MAC IP Suite: 10G25G EMAC IP vs 25G EMAC/PCS + RS-FEC IP

We compare the different between two 25G Ethernet MAC IP cores from Design Gateway. The 10G25G EMAC IP supports 10G and 25G Ethernet speeds, while the new 25G EMAC/PCS + RS-FEC IP is designed specifically for 25G Ethernet. Discover their features and differences, including their compatibility with UDP and TOE IP cores.

These IP cores enhance FPGA applications, offering complete network stacks with improved bandwidth and reduced development time. The 10G25G EMAC IP prioritizes low latency and resource efficiency, ideal for Fintech, while the 25G EMAC/PCS + RS-FEC IP emphasizes data reliability.

Compare two Ethernet MAC IP cores from Design Gateway

Our first IP core is the 10G25G EMAC IP core, which is part of our Network IP suite and supports 10G and 25G Ethernet speeds.

The second IP core is the new IP core, 25G EMAC/PCS + RS-FEC IP, which is designed specifically for 25G Ethernet speed.

Both IP cores are also compatible with our UDP and TOE IP cores.

By the end of this article, you will have a clear understanding of the features of both Ethernet MAC IP cores, and be able to differentiate the differences between them.

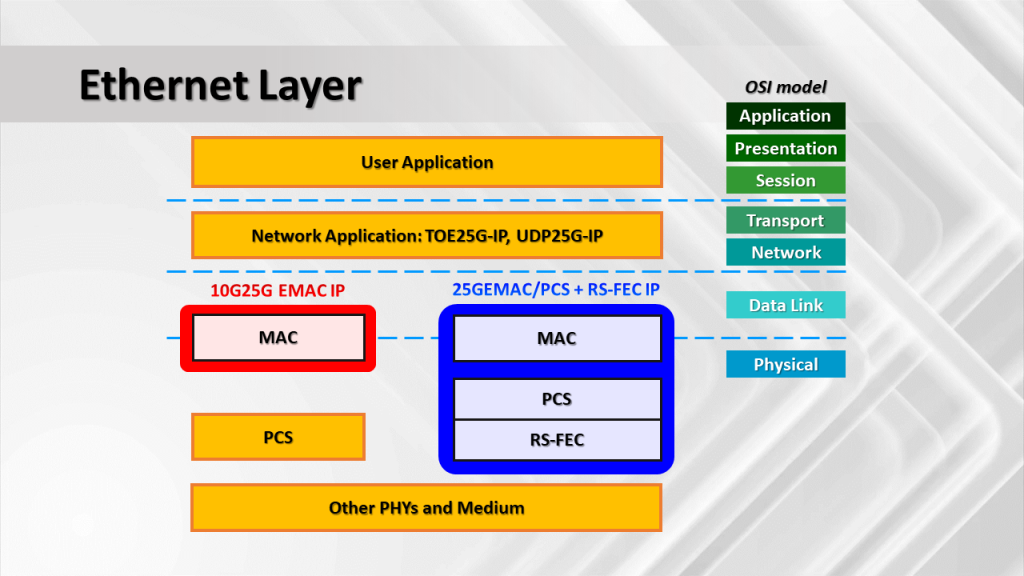

The network system is typically divided into seven layers according to the OSI model, which includes the application, transport, network and data link layers.

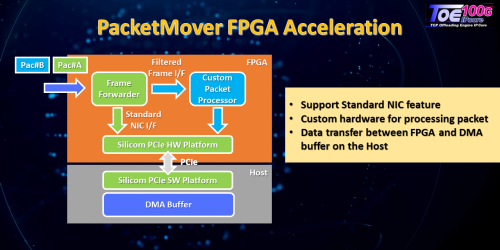

However, in FPGA systems, the five upper layers, from the application layer to the network layer, are implemented by software, while the data link and physical layers, are implemented by hardware logic.

To improve transfer performance and offload the CPU, Design Gateway provides TOE IP and UDP IP cores that use hardware logic to implement network applications such as TCP/IP and UDP/IP. This allows for increased bandwidth to achieve the maximum value.

To complete the network product lineup, Design Gateway also offers IP cores for the data link and physical layers.

Two IP cores are available for these features: the 10G25G EMAC IP core, which implements only the Ethernet MAC layer, and the 25G EMAC/PCS + RS-FEC IP core, which includes additional sublayers within the physical layer, PCS and RS-FEC.

Both IP cores are designed to minimize resource usage and latency time while remaining easy to use.

By utilizing Design Gateway’s IP cores, FPGA applications can easily obtain a complete network stack, reducing development time and allowing users to work with their own applications.

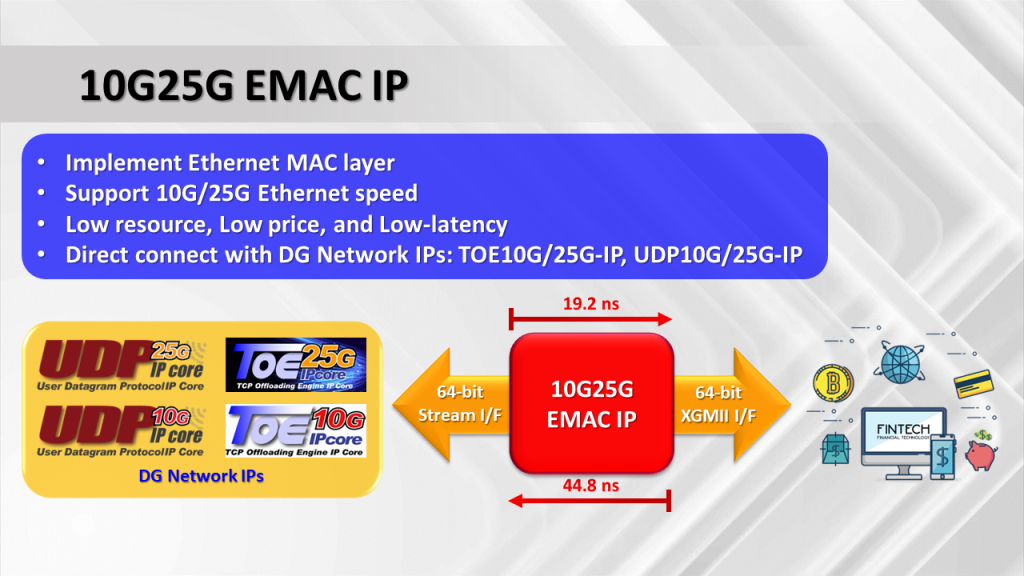

The 10G25G EMAC IP core

This IP core is responsible for implementing the Ethernet MAC layer and connects to the PCS logic via a 64-bit XGMII interface.

The versatility of the 10G25G EMAC IP core comes from its ability to support both 10G and 25G Ethernet speeds by simply changing the PCS logic.

It was specifically designed for low-latency applications, boasting an impressive transmit latency time of just 19.2 ns and a receive latency time of 44.8 ns.

With its low resource consumption, this IP core is lightweight and highly efficient, making it an excellent choice for applications that prioritize low latency, such as Fintech.

Furthermore, its 64-bit Stream user interface is compatible with Design Gateway’s network IP cores, including the TOE10G, TOE25G, UDP10G, and UDP25G IP cores, enabling seamless integration with existing systems.

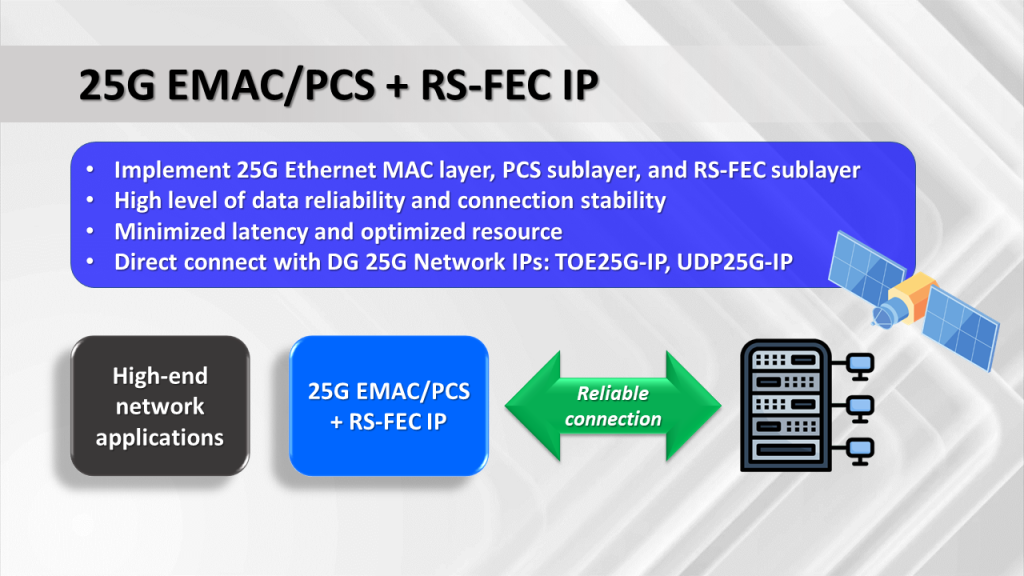

The 25G EMAC/PCS + RS-FEC IP core

As the name suggests, this IP core provides a comprehensive implementation of the physical layer, including the Ethernet MAC layer, Physical Coding sublayer (PCS), and RS-FEC sublayer.

The incorporation of RS-FEC in the system significantly enhances data reliability and connection stability, making it an ideal option for applications that prioritize data reliability.

Although the inclusion of RS-FEC may increase the overall latency time in the physical layer, it is worth noting that the resulting latency is still lower than many other options available on the market.

Overall, this IP core is well-suited for any 25G Ethernet application that requires reliable data transfer.

Furthermore, like the 10G25G EMAC IP, the user interface of this IP core is compatible with the TOE25G and UDP25G IP cores from Design Gateway.

Let’s conclude by summarizing the key differences between the two IP cores we’ve discussed – the 10G25G EMAC IP and 25G EMAC/PCS + RS-FEC IP.

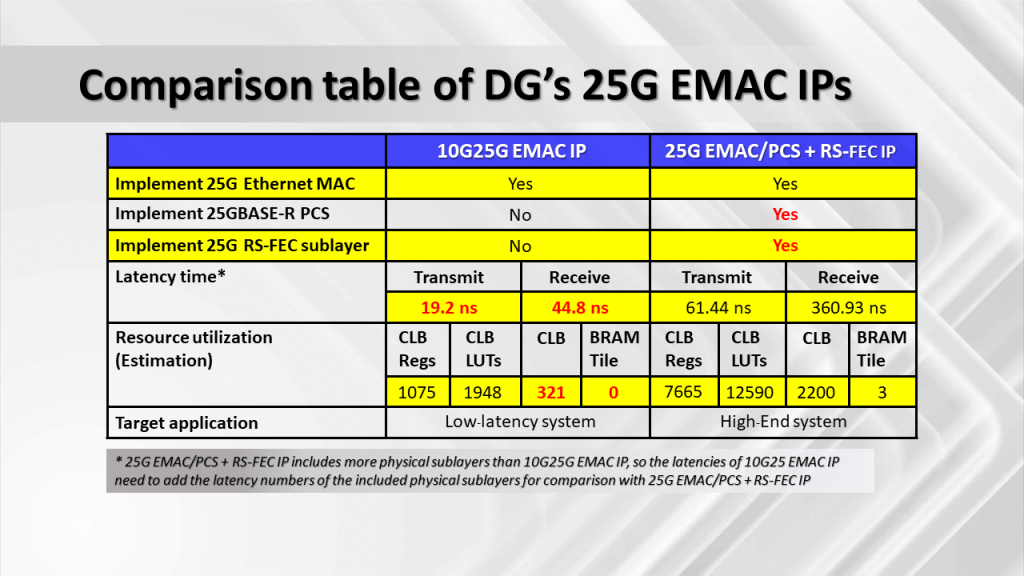

Firstly, the 10G25G EMAC IP only implements the Ethernet MAC layer, whereas the 25G EMAC/PCS + RS-FEC IP implements the Ethernet MAC, PCS, and RS-FEC layers.

Secondly, the latency times of both IPs differ. As shown in the table, the 10G25G EMAC IP has a lower transmit and receive latency time, owing to its shallower physical layer depth.

Thirdly, the resource utilization of 25G EMAC/PCS + RS-FEC IP is larger due to the inclusion of RS-FEC.

Overall, the 10G25G EMAC IP is more suitable for high-end Fintech applications that prioritize low latency, while the 25G EMAC/PCS + RS-FEC IP is better suited for 25G Ethernet applications that require high data reliability.

If you are interested in learning more or have further questions, please visit https://dgway.com/index_E.html

Article about 25G Ethernet MAC IP