Enhancing Internet Performance and Security with QUIC10GC-IP (Introduction)

Enhance Internet performance and security with the QUIC10GC IPcore from Design Gateway. In this article, we’ll delve into the remarkable benefits of QUIC10GC IP and why it stands out as the ideal solution for your needs.

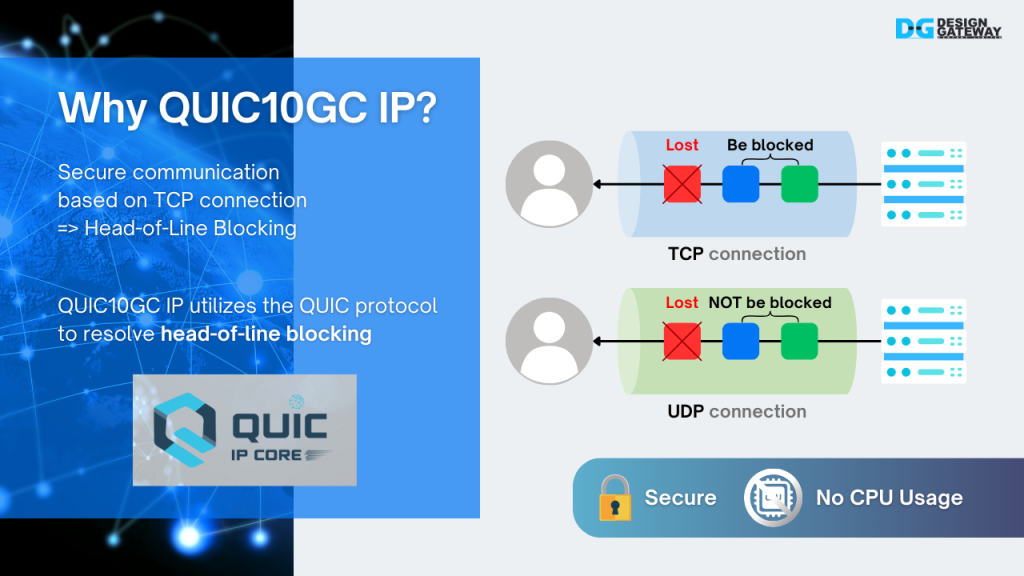

Why Choose QUIC10GC IP?

In unreliable networks, secure communication based on TCP connections suffers from Head-of-Line blocking, resulting in low data transfer throughput.

QUIC10GC IP leverages the QUIC protocol to overcome Head-of-Line blocking by using a UDP-based transport layer, while efficiently managing security and flow control.

Our QUIC10GC IP ensures network security, maintains high throughput, is compatible with 10G Ethernet, and operates without the need for a CPU.

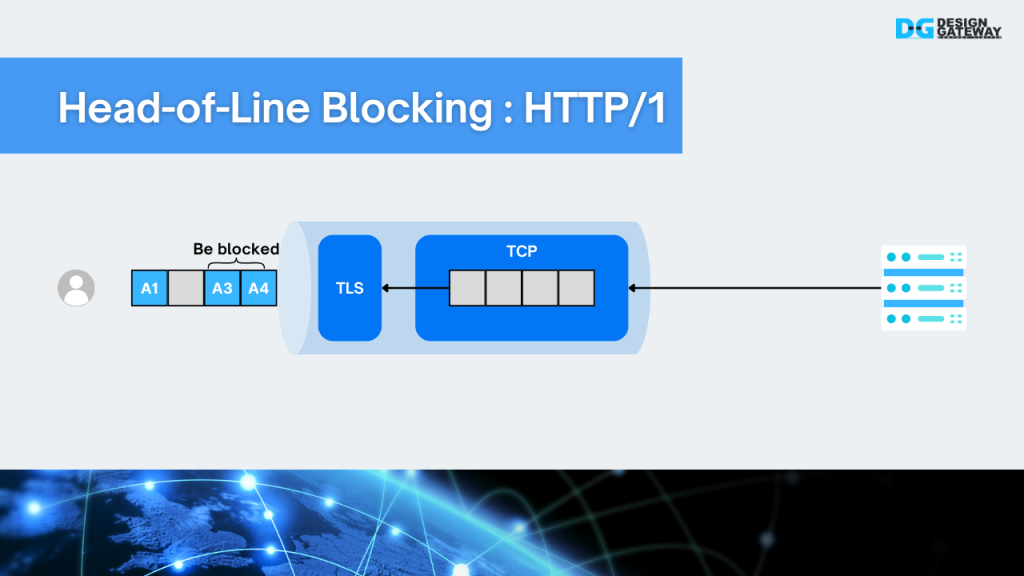

Let’s take a closer look for head-of-line blocking issue. Head-of-Line (HoL) blocking in HTTP/1.1 occurs because it uses a single connection for multiple requests.

When a client sends several requests, the server must respond in order. If one response is delayed, all subsequent responses are blocked, leading to slower performance and inefficient use of the connection, especially in high-latency or unreliable networks.

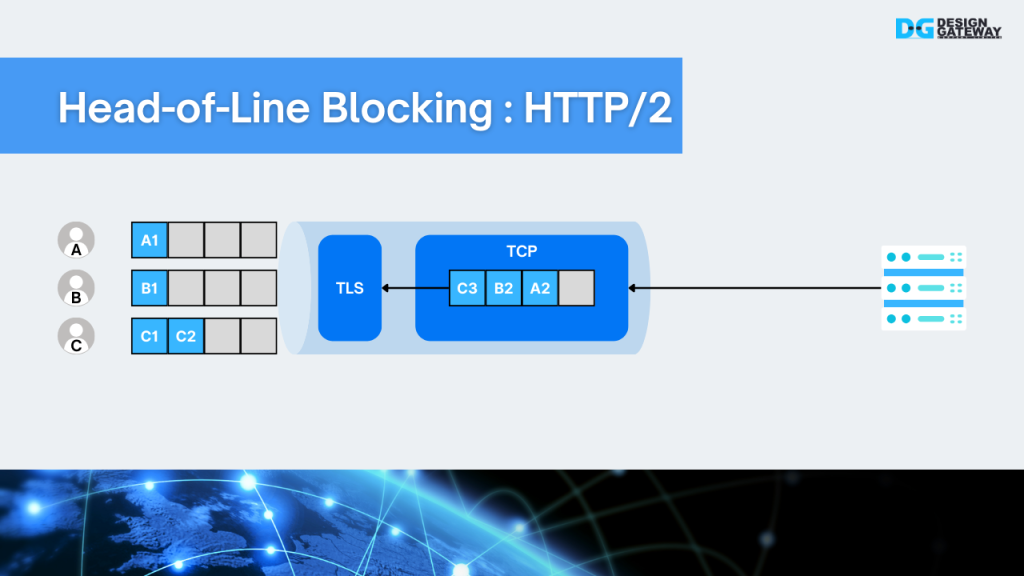

HTTP/2 addresses HoL blocking with multi-stream multiplexing at the application layer. It splits data into smaller frames, interleaves them, and identifies them by stream IDs.

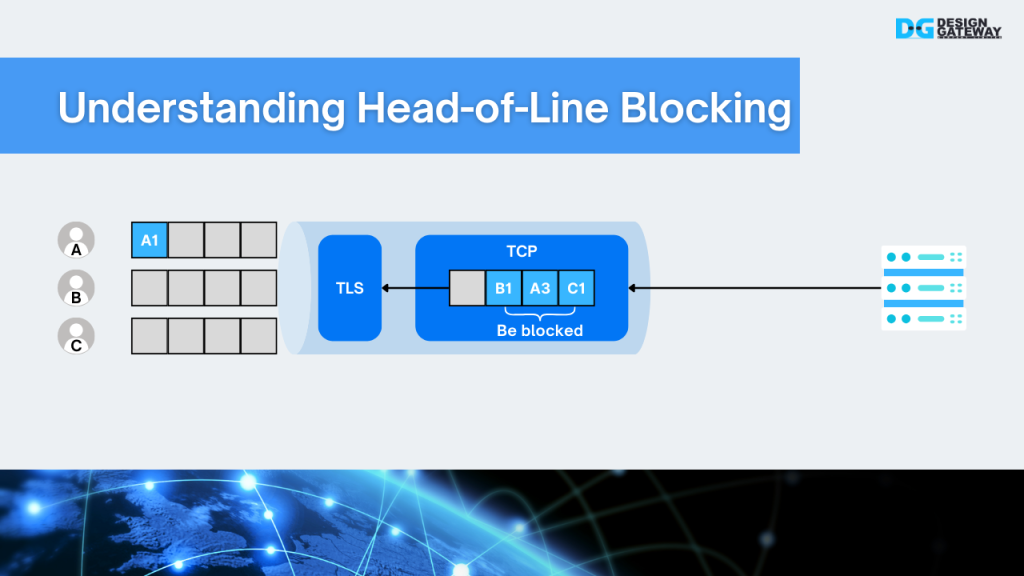

For example, there are 3 streams, A B C, for this connection. This allows independent streams to be processed out of order, reducing HoL blocking at the application layer, though it still remains an issue at the transport layer with TCP.

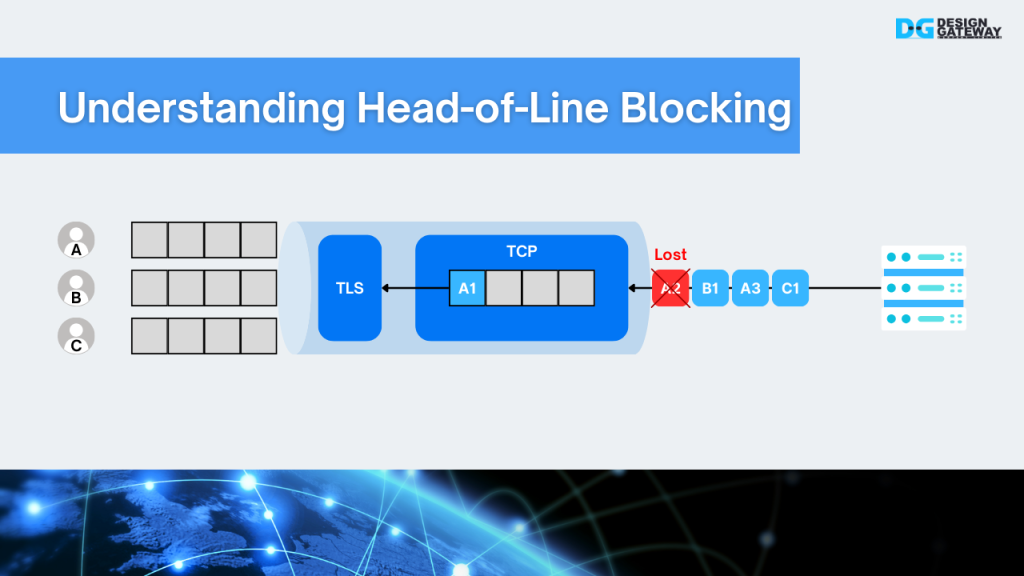

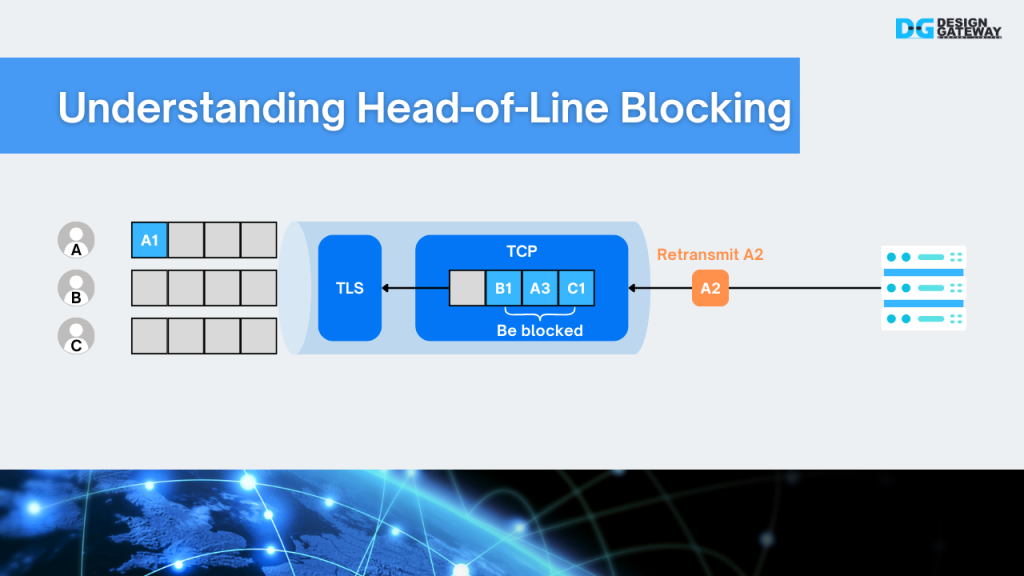

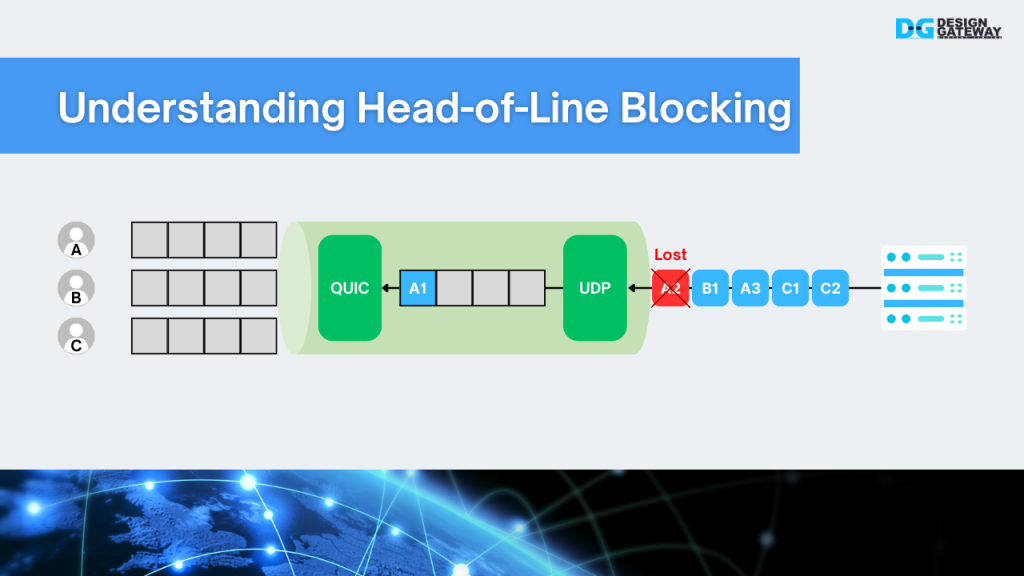

In an unreliable network using TCP, packet loss leads to head-of-line blocking. Imagine the sender transmits 4 packets, but packet A2 is lost.

When the receiver gets packets B1, A3 and C1, they are blocked and cannot be sent to the upper layer for processing because packet A2 is missing. TCP needs to receive packet A2 to construct the continuous received data before sending it to the upper layer.

In this scenario, TLS can only process encryption/decryption for packet A1.

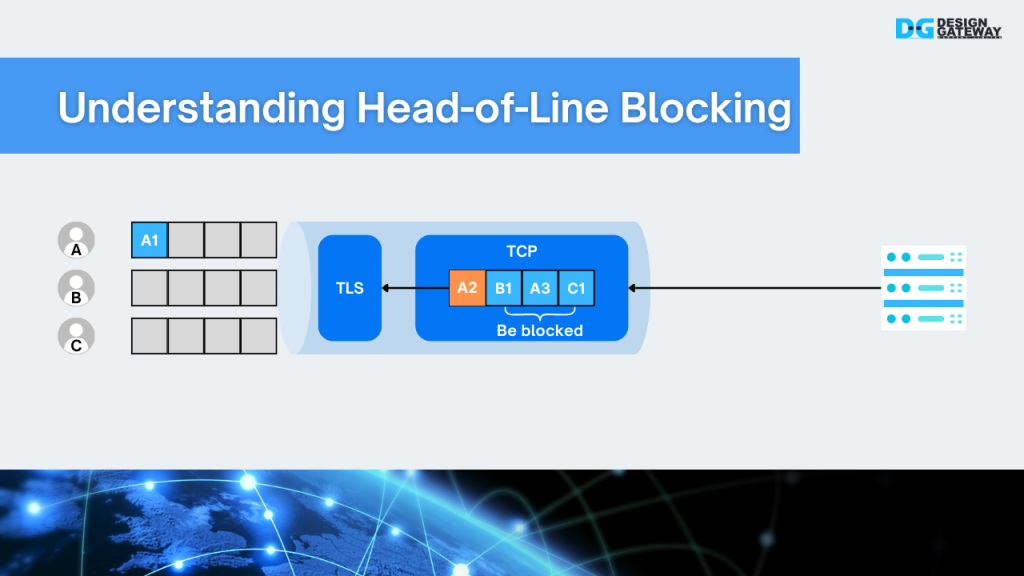

The TCP engine must completely receive packet A2 before sending packets B1, A3 and C1 to TLS for continuous processing.

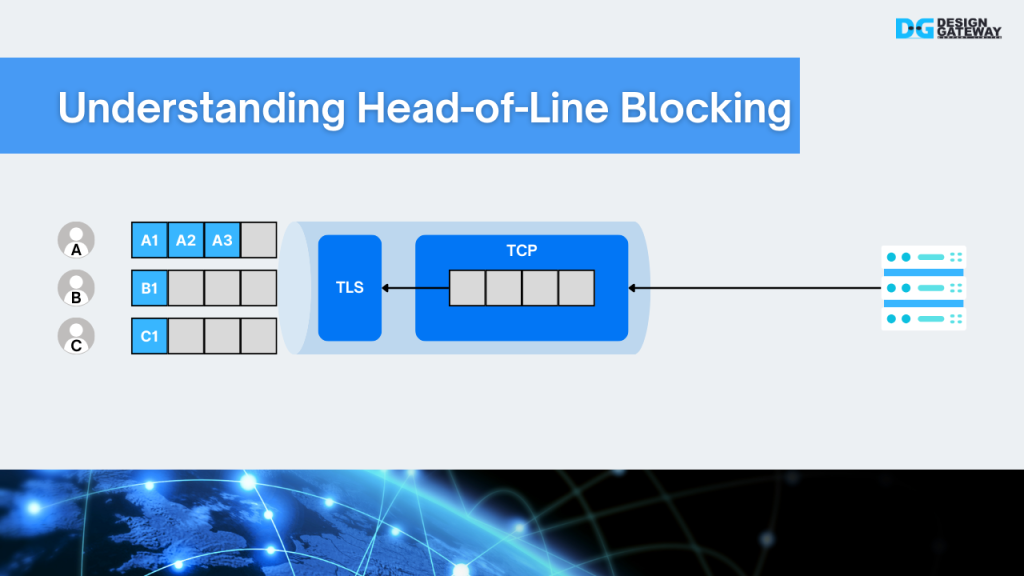

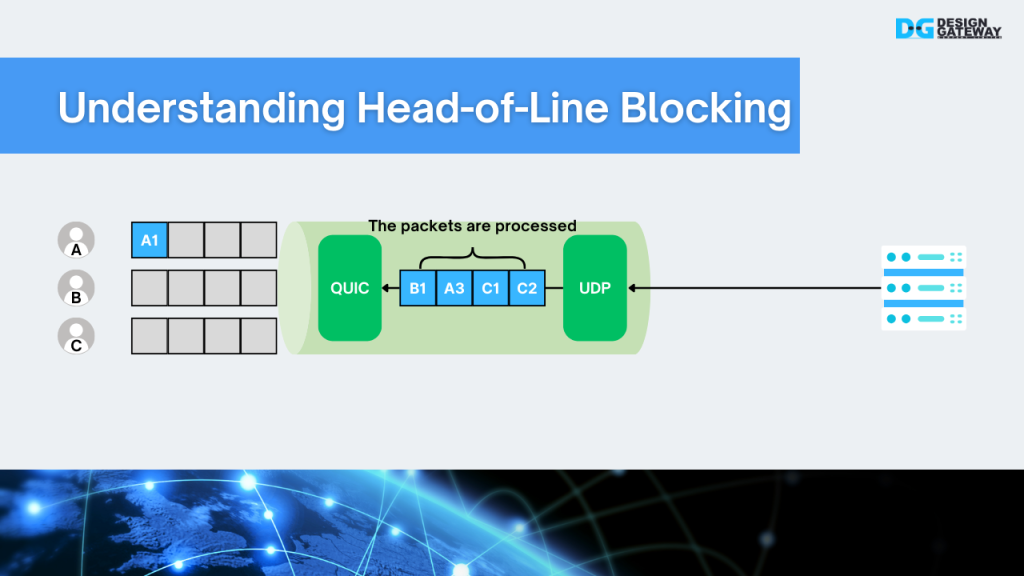

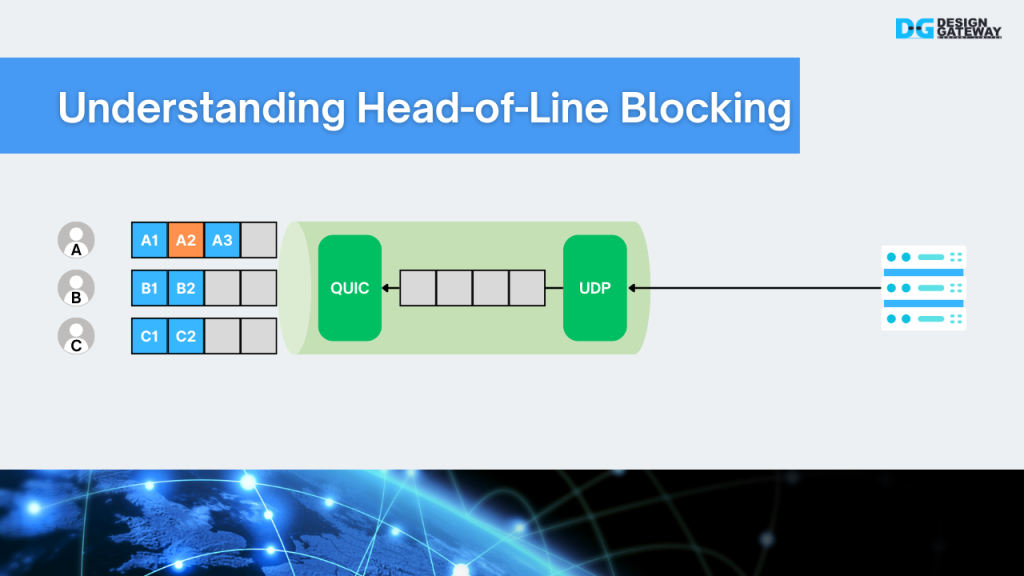

This issue can be solved by using QUIC with UDP. Data packets are not required to be received in sequence in a UDP connection, so if packet A2 is lost…

…and the next packets B1, A3, C1, and C2 are successfully received…

all received packets can still be sent to QUIC for processing. In this case, user B and C can process B1, C1 and C2 without being blocked by the lost A2.

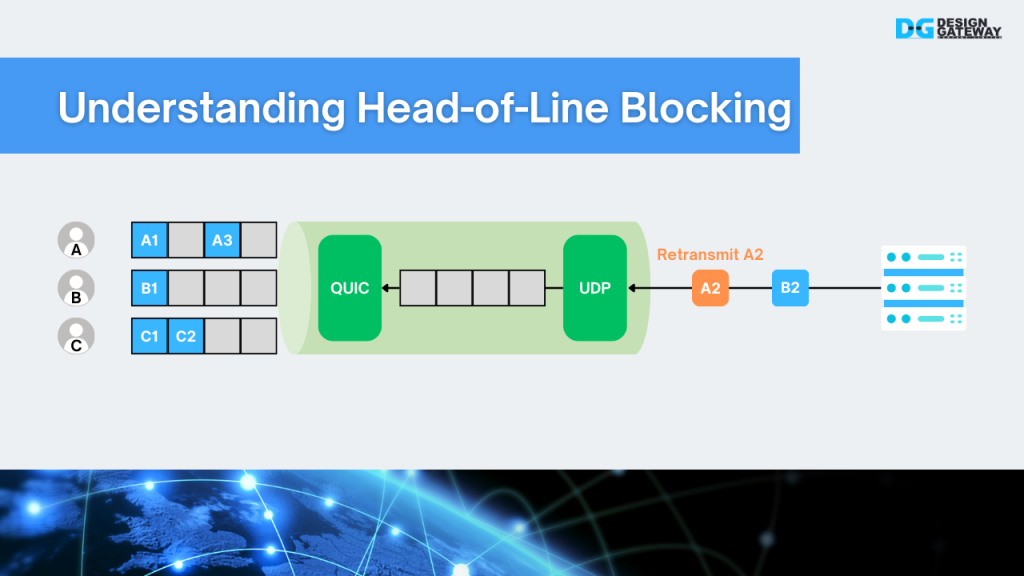

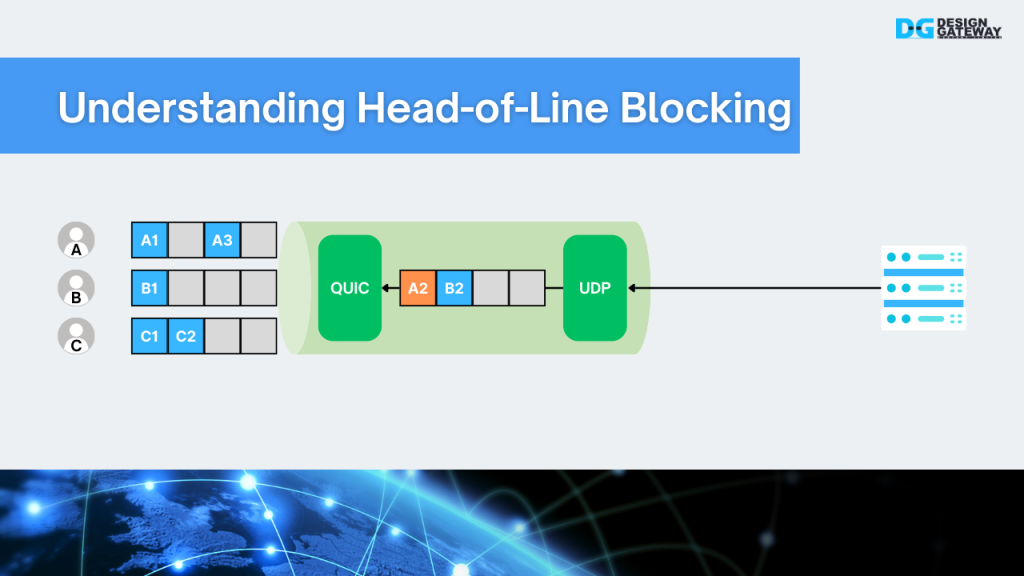

When the receiver gets the retransmitted packet A2, UDP can send the data to the upper layer, QUIC, which decrypts the packet…

…and manages the payload of packet A2 into the correct memory position.

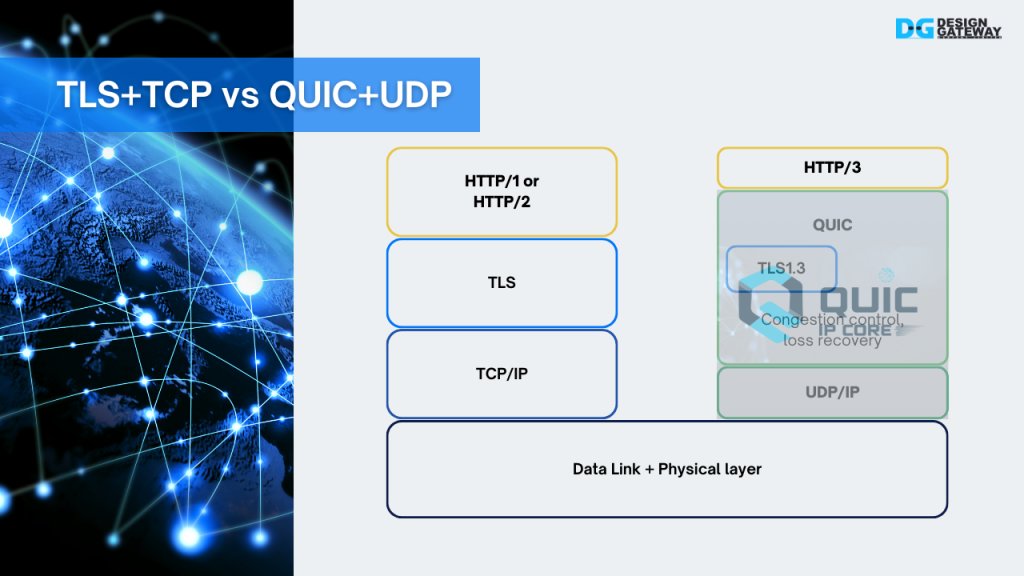

This figure illustrates the protocol stack differences between TLS+TCP/IP and the QUIC+UDP/IP.

QUIC+UDP/IP is used instead of TLS+TCP/IP to solve to head of line blocking. QUIC implements TLS1.3 for key negotiation and handles encryption/decryption, congestion control, loss recovery, and stream multiplexing, integrating some transport and application layer responsibilities.

Our QUIC10GC-IP implements both QUIC and UDP/IP layers, efficiently managing data flow, providing reliability, and ensuring security.

Get ready to witness the power of QUIC10GC in action! In our next article, you’ll see a live demonstration of QUIC10GC on the ZCU106 FPGA board.

Discover how this advanced solution seamlessly integrates and performs, showcasing its superior capabilities and features.

For more information about our QUIC10GC IP and to explore its full range of features, please visit our website. 🌐

👉 https://dgway.com/en/amd/quic-ip.html

YouTube: https://youtu.be/6to84e9H6EI

Article about QUIC10GC-IP