Enhancing Data Reliability in 25G Ethernet Systems with Reed Solomon Forward Error Correction

We delve into the implementation of Reed Solomon – Forward Error Correction in a 25G Ethernet system, with a focus on RS-FEC.

We will be exploring its benefits and practical applications in FPGA-based 25G Ethernet systems.

We will cover the basic concepts of RS-FEC, its implementation on FPGA, and how it enhances data reliability in Ethernet systems.

By the end of this presentation, you will have a clear understanding of the advantages of RS-FEC and its importance in modern 25G Ethernet applications.

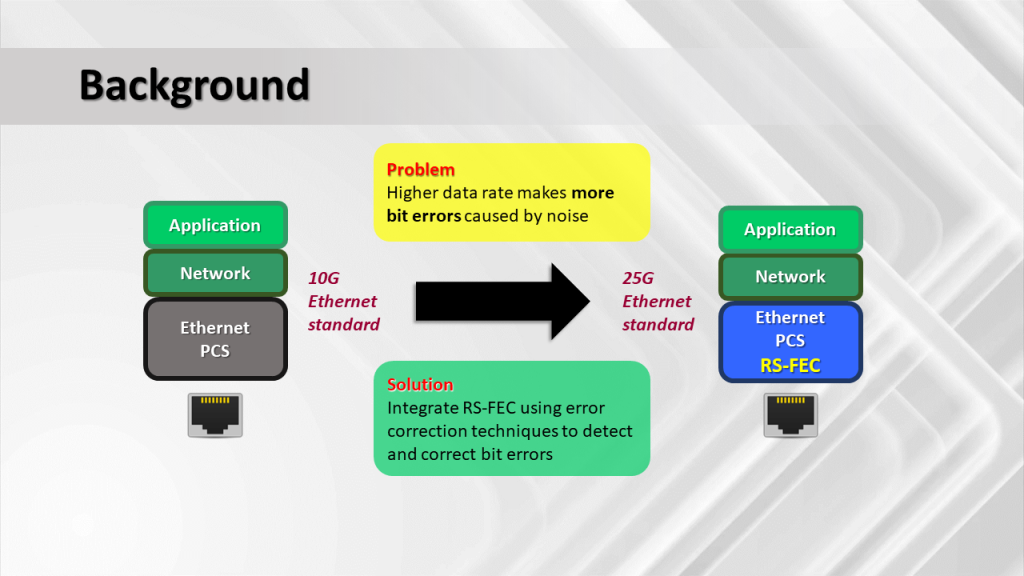

With the increasing demand for higher bandwidth in modern applications, the 25G Ethernet has become a crucial technology for meeting these needs.

However, higher data rates also bring challenges, such as an increased bit error rate caused by noise and interference in the transmission medium. To address this challenge, the IEEE 802.3 Ethernet standard recommends implementing RS-FEC in the Ethernet layer.

RS-FEC utilizes advanced error correction techniques, including complex mathematical theories, to detect and correct bit errors in real-time.

This ensures that the transmitted data is accurate and reliable, maintaining the integrity of the Ethernet connection.

By integrating RS-FEC into the 25G Ethernet standard, it is possible to improve the quality of transmission and support the requirements of high-bandwidth applications.

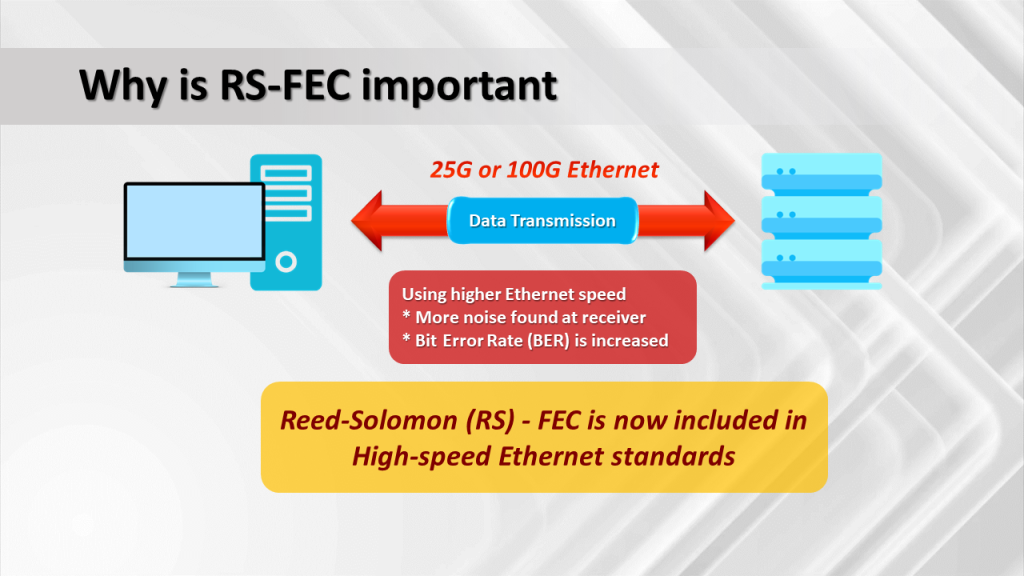

Now we will discuss the importance of using RS-FEC in high-speed Ethernet standards, such as 25G or 100G.

When two devices communicate with each other, they require a medium for data transmission.

As the need for higher Ethernet speeds increases, optical fiber is the appropriate medium for data transfer capabilities.

However, even with optical fiber, there is an increase in Bit Error Rate (BER) when data is transferred at very high speeds in Ethernet.

This issue arises due to several factors, including attenuation over distance in optical cables and equipment quality. To address this, RS-FEC (Reed-Solomon Forward Error Correction) is used.

RS-FEC provides the ability to detect and correct errors without requiring expensive mediums or equipment.

Therefore, RS-FEC has become a standard in high-speed Ethernet, ensuring data transmission at higher speeds with minimal errors.

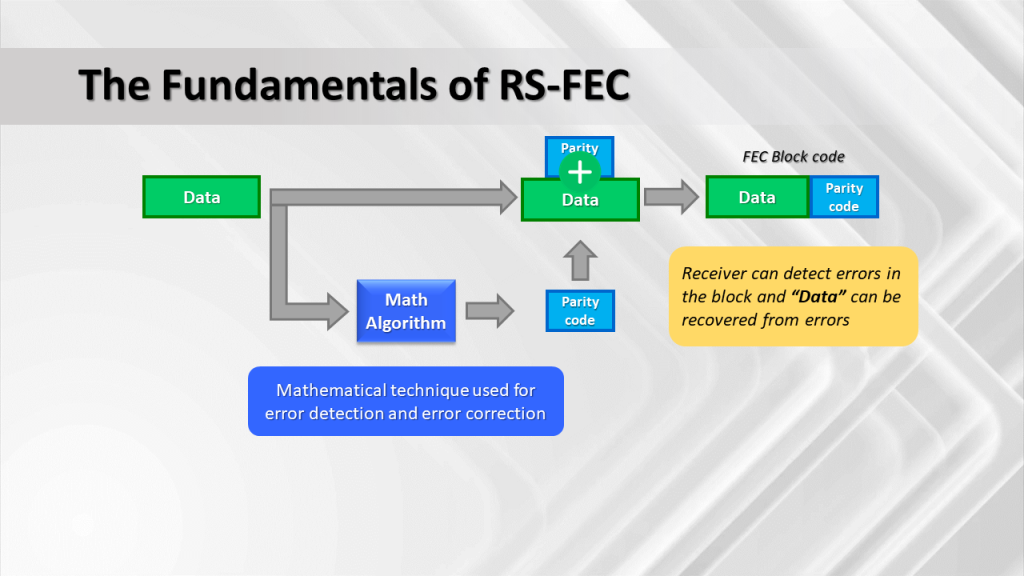

The fundamentals of RS-FEC

FEC is a mathematical technique used to identify and correct errors in the data stream.

Essentially, the mathematical algorithm generates additional information, called Parity code, which is then combined with the original data stream.

The Parity code is then used by the receiver to identify the errors in the data stream and correct them.

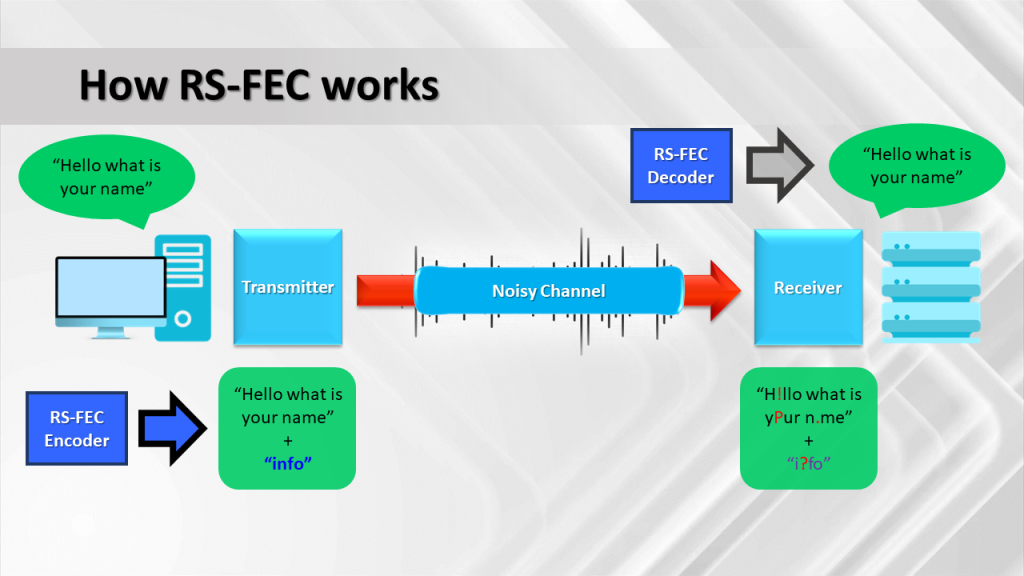

How RS-FEC works in a communication system

Imagine two devices communicating with each other, with the device on the left wanting to send a message to the device on the right.

Initially, the left device creates and sends the message, “Hello, what is your name”

However, before transmitting the message, the RS-FEC encoder calculates the parity and adds it as special information to the message.

When the message with the special information travels through a noisy channel, there’s a chance that some data bits may become corrupted and unreadable.

But the RS-FEC decoder at the receiver can detect and correct any corrupted messages by using the special information for data recovery.

As a result, the message “Hello, what is your name” can be correctly received and read by the device on the right, even if some bits were corrupted during transmission.

Overall, this example demonstrates how RS-FEC can effectively detect and correct data errors in a communication system, ensuring that messages are transmitted reliably and accurately.

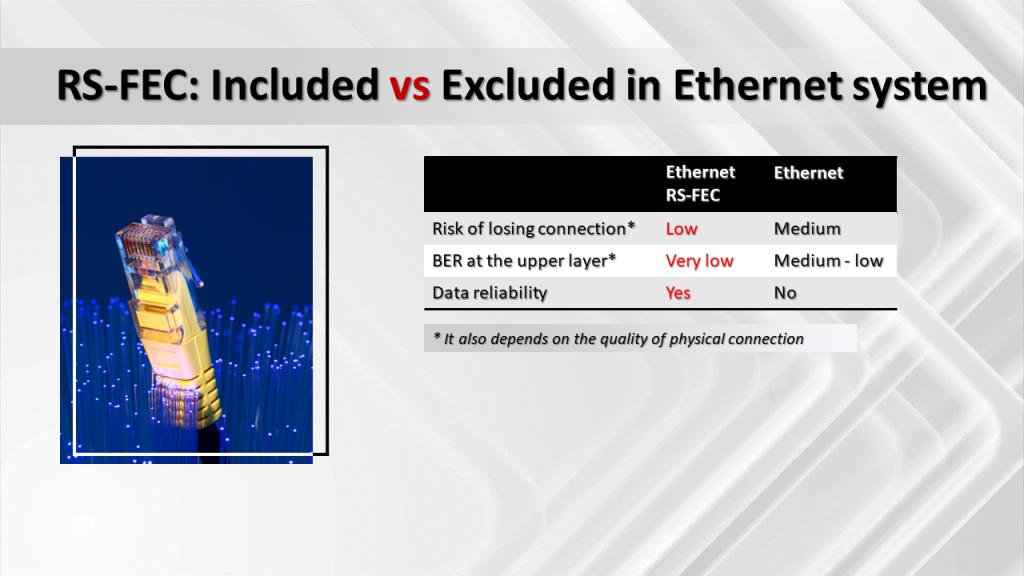

In the 25G Ethernet standard, users have the option to include or exclude RS-FEC in Ethernet configurations.

Let’s compare these two systems.

Firstly, the Ethernet system without RS-FEC has a higher risk of physical-layer Ethernet connection loss.

This means that data transmission may not occur as expected, leading to potential disruptions in communication.

Secondly, when the RS-FEC is included, the Bit Error Rate at the upper layer is significantly lower and can be considered “nearly free-error”.

This greatly reduces the likelihood of data transmission errors occurring during communication.

Finally, including RS-FEC in the system makes it more reliable for data communication, while the system without RS-FEC is not as reliable.

In conclusion, it is highly recommended to implement RS-FEC in high-speed Ethernet standards. It is an essential feature that improves the overall reliability of the Ethernet system, reducing the risk of errors and ensuring smooth communication.

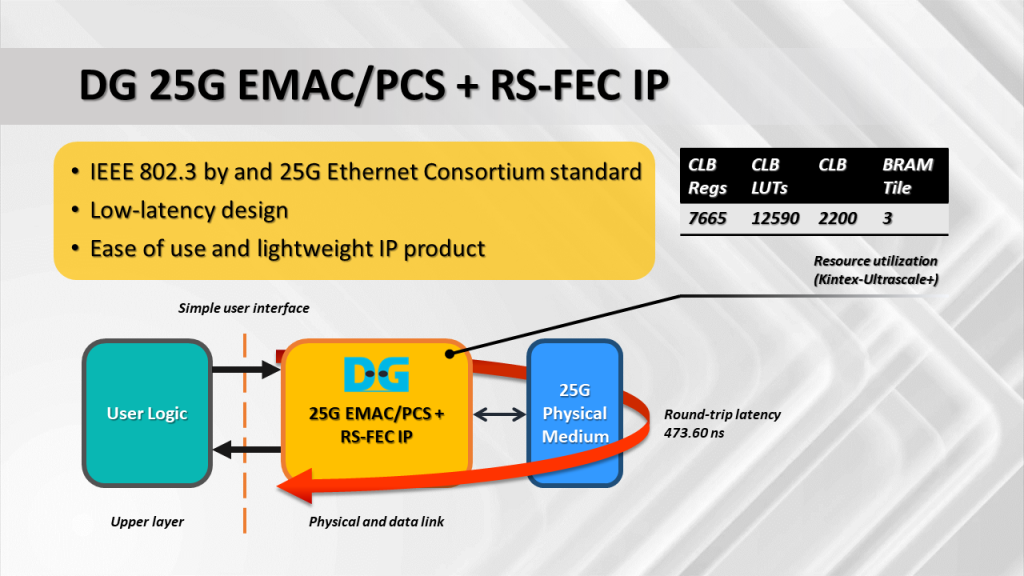

Design Gateway is proud to introduce our new FPGA solution, the “25G EMAC/PCS + RS-FEC IP”, which supports the RS-FEC feature in the 25G Ethernet system.

This IP product is designed to conform to both IEEE 802.3 by and 25G Ethernet Consortium standards, implementing the 25G Ethernet system with PCS and RS-FEC.

It uses a low-latency and area-optimized approach, and its interface is user-friendly, making it easy for users to work with.

By utilizing this IP, users can avoid the complexities of the mathematical theory of RS-FEC and the difficulties of the Ethernet standard and low-level aspects. Making it easier for users to apply 25G Ethernet in their applications.

If you are interested in learning more or have further questions, please visit https://dgway.com/index_E.html

Article about 25G Ethernet MAC IP