FPGA-based SmartNIC for high-performance TCP/IP application

This article will give you more detail of DG’s TOE100G-IP Core and Silicom’s PacketMover framework and the application of the FPGA-based SmartNIC designed for high performance TCP/IP applications.

TOE100G-IP on Silicom’s PacketMover consists of 2 parts

This system is the result of a collaboration between Design Gateway and Silicom Denmark.

Using the TOE100G-IP and PacketMover framework, we are proud to present a high performance TCP/IP engine and data mover solution for SmartNIC.

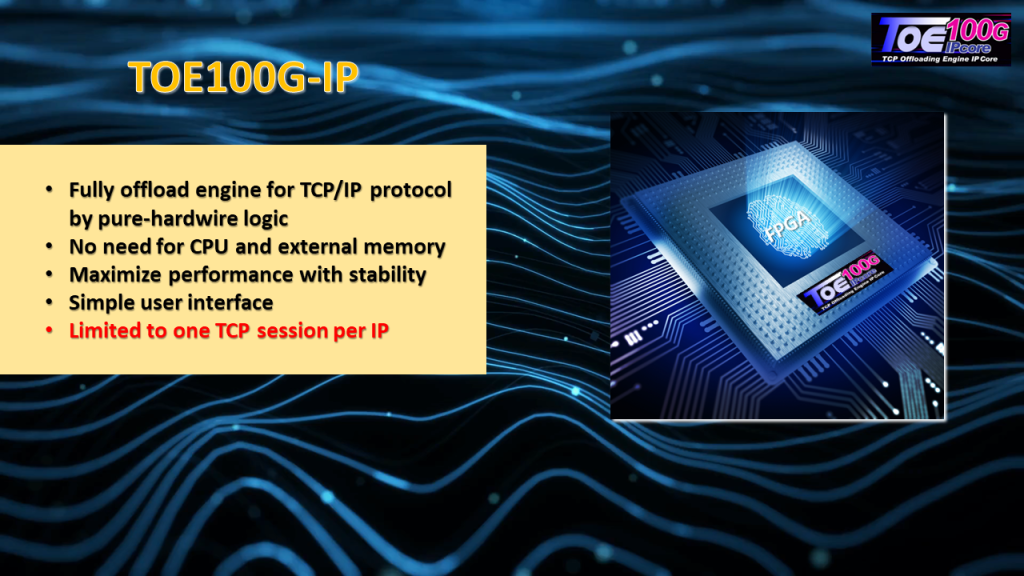

Introducing the TOE100G-IP, an inventive product from Design Gateway that provides a full offload engine for processing TCP/IP packets without using the CPU or external memory.

Its pure hardware logic design enables high performance and maximum TCP/IP throughput of 100 Gbit Ethernet while keeping the FPGA resource usage to a minimum.

Unlike other solutions, the TOE100G-IP features a sustainable performance as the hardware is always available, not a shared resource.

The user-friendly interface allows users to use the TOE100G-IP without requiring deep knowledge of TCP/IP protocol requirements.

Although the hardware is designed to handle only one TCP session for each TOE100G-IP, it delivers maximum transfer performance, making it an excellent choice for those who prioritize high-speed data transfer.

Experience the power of TOE100G-IP and achieve unparalleled data transfer speed with ease.

Introducing the KU15P FPGA card, a cutting-edge networking solution from Silicom.

Design for 100G Ethernet network connectivity, this FPGA card features two QSFP28 connectors for integration with other network devices.

With Silicom’s advanced platform, both hardware and software work in tandem to capture Ethernet network packets and efficiently transfer them to the host memory via a 16-lane PCIe Gen3 connector.

The maximum throughput and zero packet loss are succeeded while utilizing the packet filtering hardware to customize rule sets to your exacted specifications.

Even with the full range of Smart NIC features, this FPGA card still has enough logic resources available for users to add their packet processing engine for a personalized networking solution.

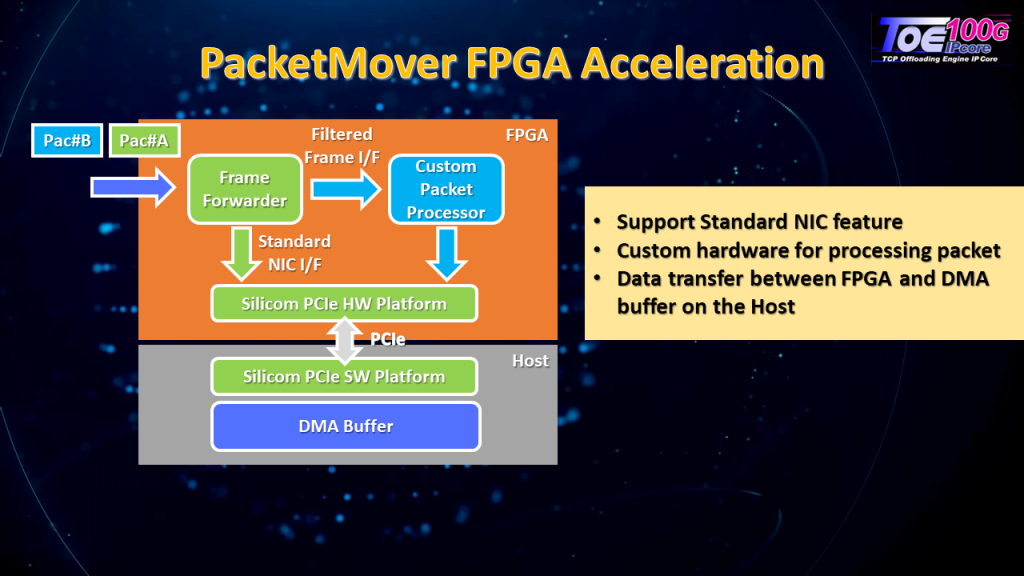

The PacketMover FPGA Acceleration is a platform that combines hardware and software and communicates through a PCIe interface.

The Host software sets the rules for the Frame Forwarder to forward Ethernet packets to either the Filtered Frame I/F or Standard NIC I/F.

If a packet doesn’t match any rule, it’s sent to the DMA buffer on the Host system via the Standard NIC I/F. If it matches the rule, it’s forwarded to the Filtered Frame I/F.

The default mode of the Custom Packet Processor simply sends the received packet to the DMA buffer on the Host system.

To summarize, the PacketMover FPGA Acceleration offers three main features: the Standard NIC feature, the Custom Packet Processor, and the data transfer between the FPGA and the Host.

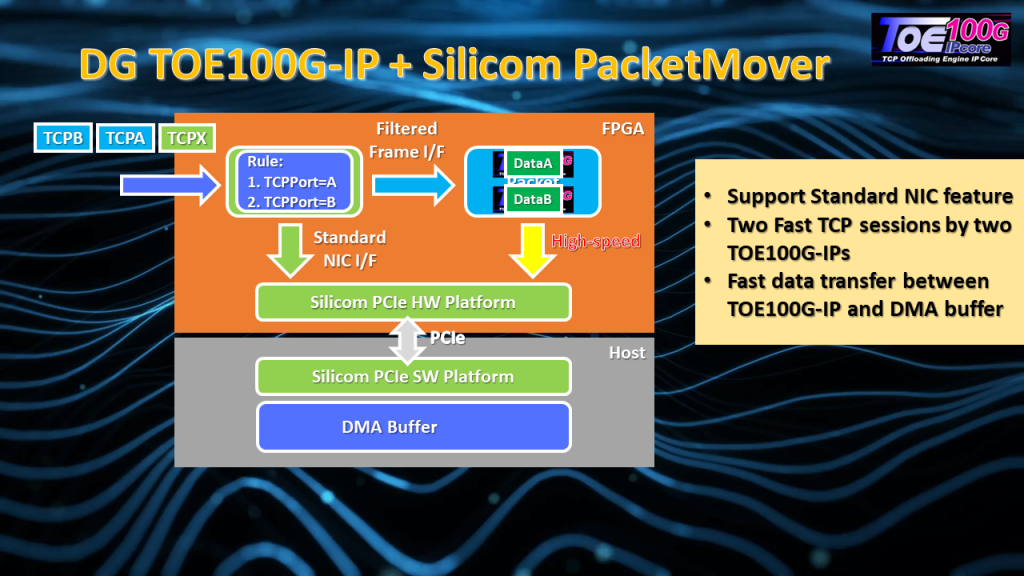

A high-performance TCP/IP application can be achieve with an FPGA-based SmartNIC, which integrates two TOE100G-IPs and DMA logic into the Silicom PacketMover hardware platform.

The rules of Frame Forwarder are configured to forward TCP/IP packets from two specific ports, PortA and PortB, to the custom hardware for fast-speed processing.

The other packets are forwarded to the Standard NIC I/F and then uploaded to the Host buffer to wait for CPU processing.

Meanwhile, the TOE100G-IPs handle the TCP/IP packets from PortA and PortB and extract the payload data, which is then upload to the DMA buffer at a very high-speed rate.

This allows the user application to process the data without needing to handle the TCP/IP protocol.

Overall, the system provides the standard NIC feature and the ability to transfer two specific TCP sessions at high speed rates, with the payload data fully decoded by the TOE100G-IPs.

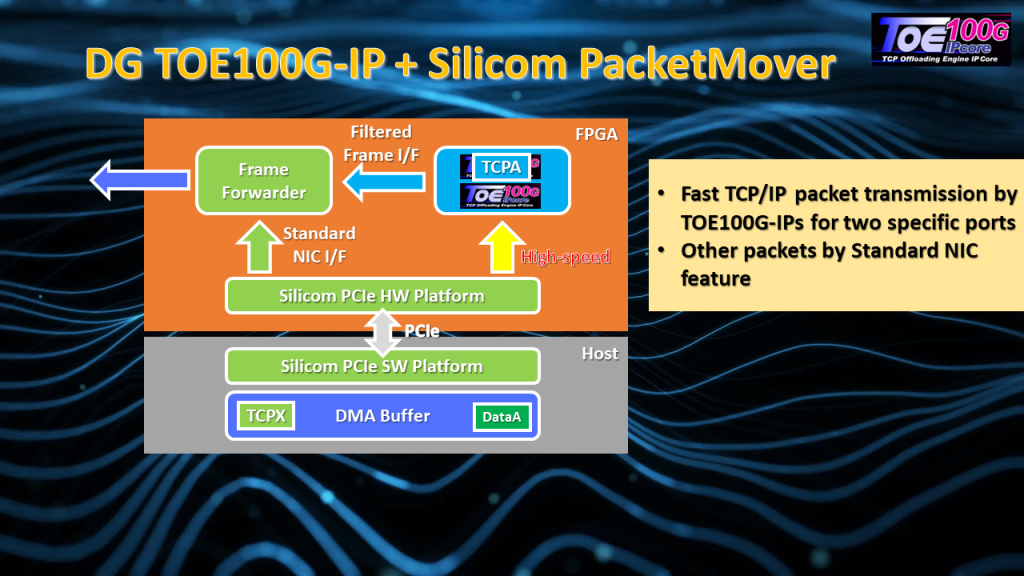

TOE100G-IP facilitates high-speed transmission of TCP/IP packets in both direction of transfer. To achieve fast transmission using PortA and PortB, the payload data within the DMA buffer is read and encoded by TOE100G-IPs.

The resulting TCP/IP packet is then transmit to the Ethernet connection via the Frame Forwarder. The Standard NIC feature remains available.

The CPU can generate packets within the DMA Buffer and subsequently initiates the FPGA logic to forward the packets from the DMA buffer to the Ethernet connection through the Standard NIC I/F.

In summary, the system is a solution that supports the standard NIC feature. The FPGA integrates two TOE100G-IPs, enhancing the speed of TCP/IP packet transmission for two TCP sessions.

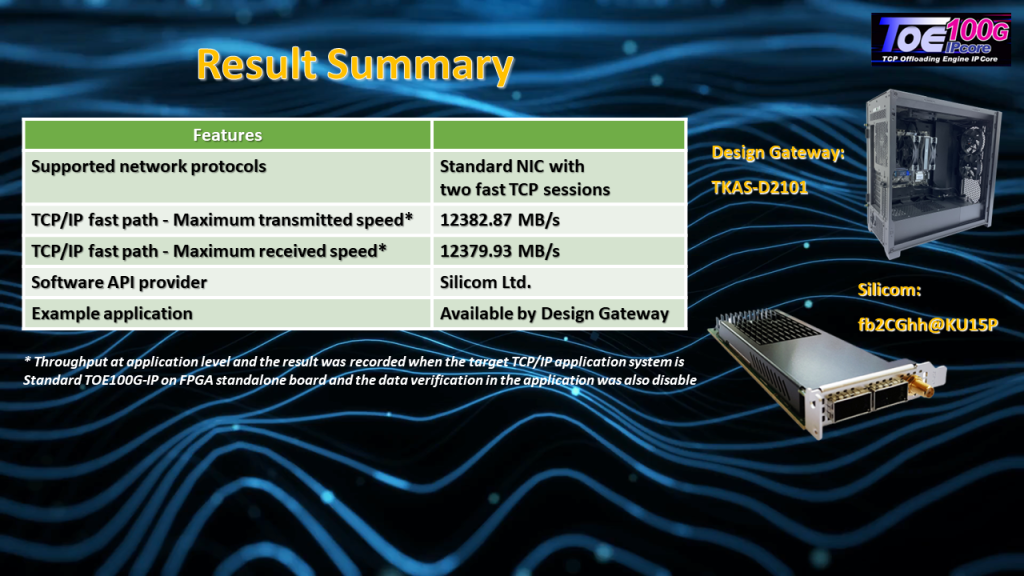

The performance test on the test system indicates a maximum throughput of 12 Gbytes/sec in both transmit and receive directions, achieving the 100G Ethernet line rate.

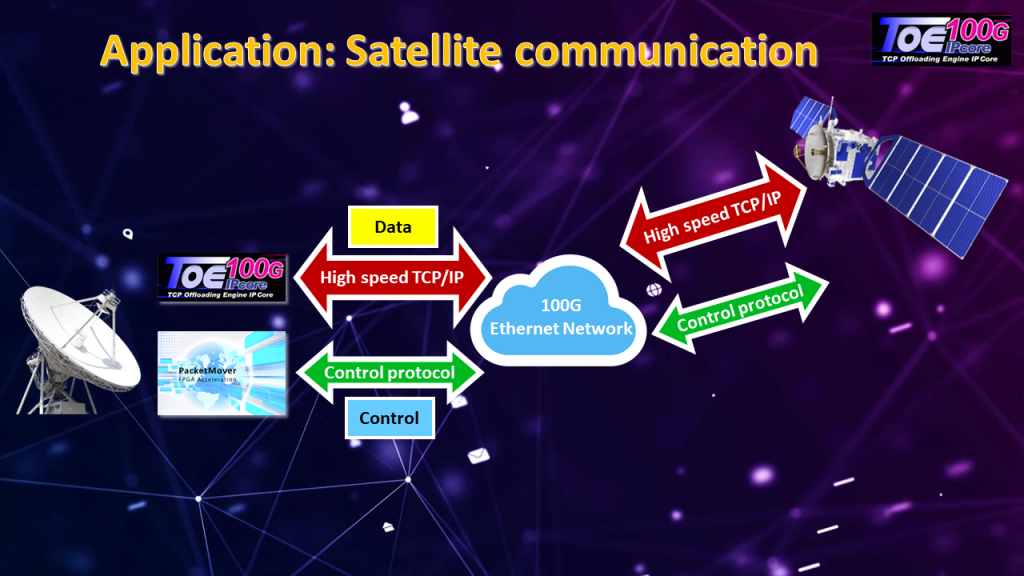

Satellite communication is the process of exchanging data between ground-based stations and satellites in orbit. This requires a reliable and high-performance network to ensure that data is transmitted quickly and accurately.

By integrating TOE100G-IP with FPGA, network processing in satellite communication systems can be accelerated, leading to faster data transfer.

In order to manage the control system which requires CPU power, the PacketMover platform is utilized for packet encoding and decoding.

Furthermore, additional logic can be implemented on the FPGA to offload CPU, such as security handling.

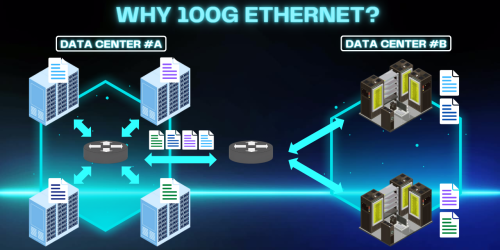

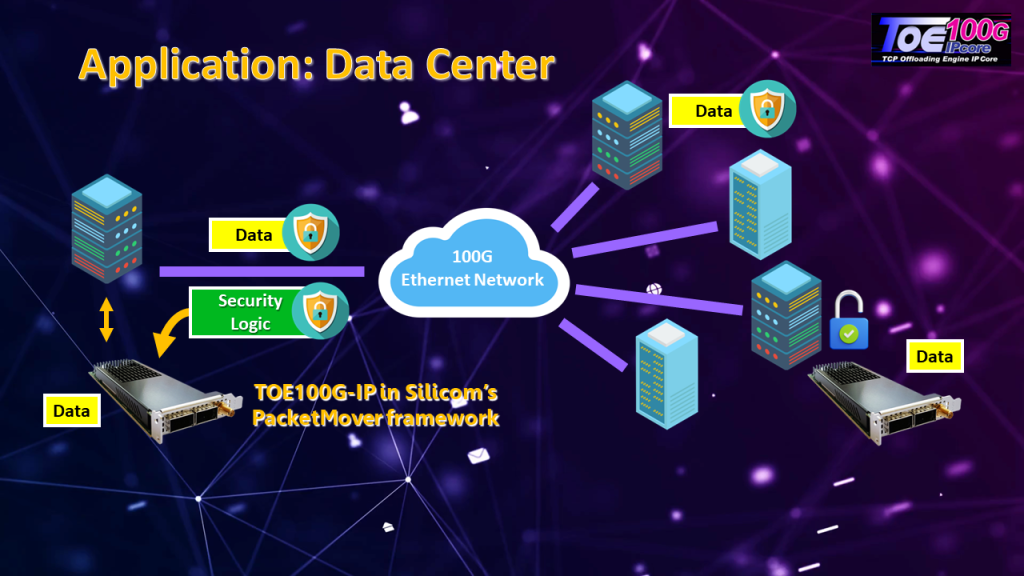

With the growing need for faster data transfer rates and more efficient use of network resources, data centers are turning to 100Gb Ethernet with FPGA to accelerate network processing and improve overall performance.

Besides, it is essential to protect the data from unauthorized access which requires significant CPU resources for enough security. By integrating more logic for offloading security operation into the TOE100G-IP on the PacketMover platform high-performance data transfer with advanced security capabilities can be achieved on a 100G Ethernet network, ensuring only authorized users can access sensitive data.

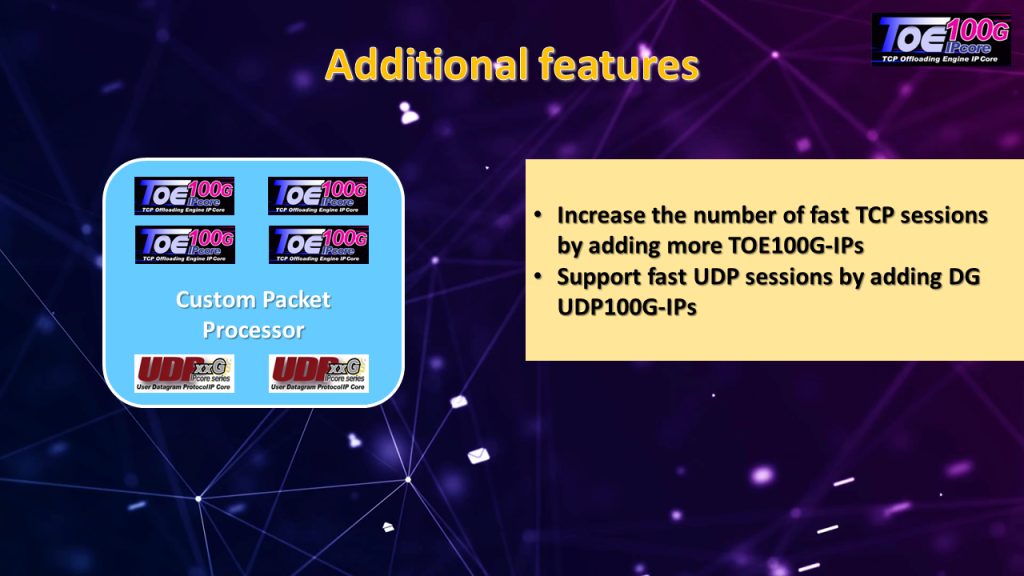

Modifications can be made to the TOE100G-IP with the PacketMover platform to enhance its functionalities.

One option is to integrate additional TOE100G-IPs, which can support the higher number of TCP sessions, resulting in faster data transmission.

Another approach is to incorporate the use of UDP100G-IP, which enables rapid transmission through the use of UDP/IP protocol.

This can improve the overall speed of data transfer, providing a more efficient and effective solution.

For more information about TOE100G-IP, please visit our website.

https://dgway.com/TOE-IP_X_E.html

For more information about PacketMover and FPGA Card, please visit Silicom website. https://www.silicom-usa.com/pr/server-adapters/programmable-fpga-server-adapter/fpga-xilinx-based-2/fb2cgku15p-fpga-card/

https://www.silicom.dk/product-details/packetmover-fpga-acceleration/

Youtube: https://youtu.be/7fp-QDO6vNM