#003 – From RTL IP core to RTL Kernel with Host Application demo

For Turnkey Accelerator System (TKAS-D2101) with Alveo U250 Card and Xilinx Vitis™ Unified Software Platform 2021.1

Based on Xilinx’s Vitis™ Application Acceleration Development Flow Tutorials: bottom_up_rtl_kernel

This tutorial introduces a bottom-up Vitis-based RTL kernel construct and wrap-up process, as well as the host-kernel interaction with Xilinx Runtime library (XRT). All the steps in this tutorial use the command-line interface, except those needed to view waveform or system diagram.

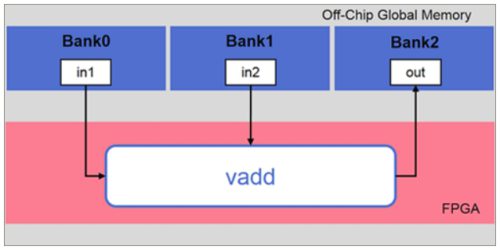

This tutorial uses an example design to illustrate the relevant concept and steps. The following image shows the block diagram of this design. It is a simple AES accelerator design and comprises two kernels, krnl_aes and krnl_cbc. The krnl_aes kernel is the core AES computation core with AXI streams slave and master ports. The krnl_cbc kernel handles the host-kernel data exchange, and the implementation of AES-ECB and AES-CBD modes along with the krnl_aes module.

Step by Step to run on TKAS-D2101

Set enviroment

source /tools/Xilinx/Vitis/2021.1/settings64.sh

source /opt/xilinx/xrt/setup.sh

Goto working folder from example #001

Additional requirements for Ubuntu

sudo apt install libssl-dev

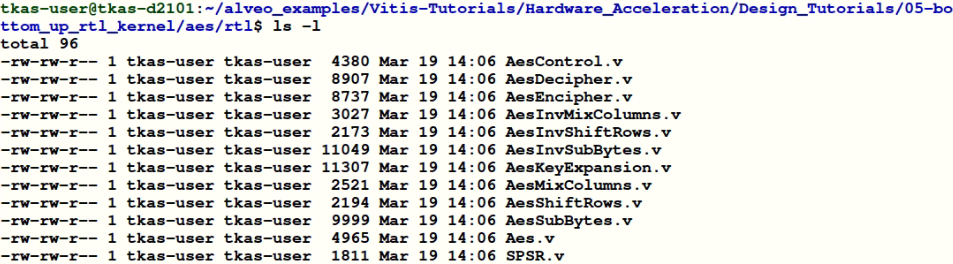

AES HDL(Verilog) & Simulation

Run make script to simulate

cd ~/aes

make runsim

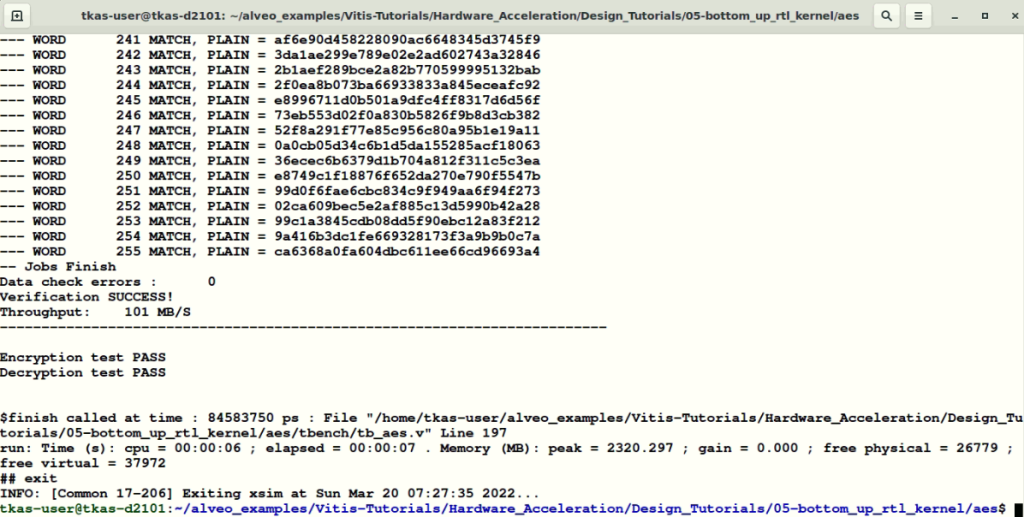

Simulation result

The simulation is executed with 256 input words (128-bit) along with pre-defined KEY. You can modified the simulation options in the ~/aes/runsim_aes_xsim.sh file. After simulation finishes, a waveform dump file called work.tb_aes.wdb is generated, in which you can view the interface waveform.

Open WDB wavform dump file from console

Create TCL script file name “open_waveform.tcl” with content below

current_filesetopen_wave_database work.tb_aes.wdb

Run vivado tcl script to open WDB waveform

vivado -source open_waveform.tcl

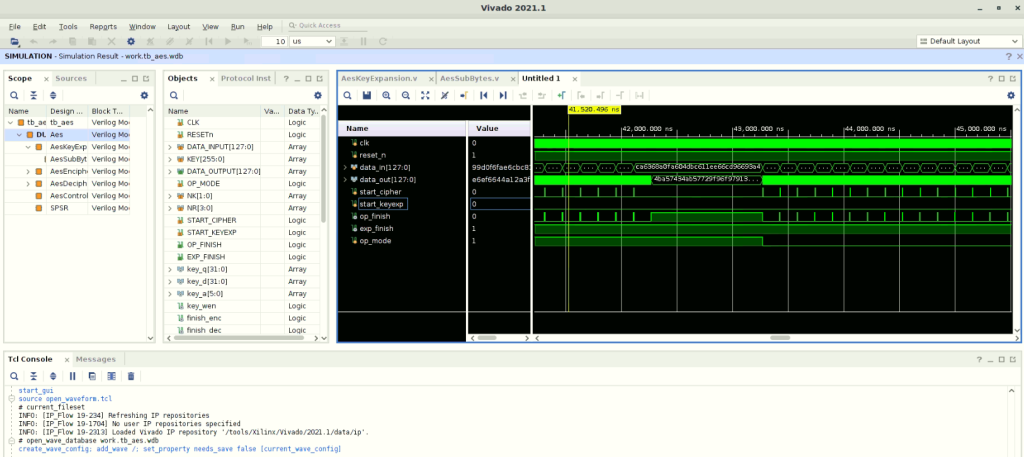

Waveform windows

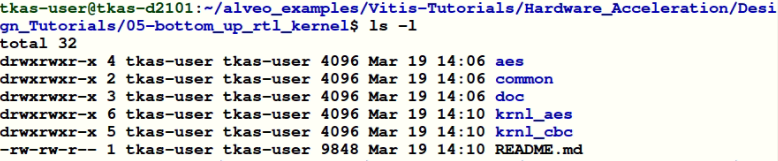

Create RTL module and pack into Vivado® IP and Vitis Kernel (XO) file

- Go to folder “~/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Design_Tutorials/05-bottom_up_rtl_kernel/krnl_aes”

- Make change in Makefile to match with your Alveo card and tool version 2021.1

Here are summary changed in Makefile.

Line 41-42

#PART := xcu200-fsgd2104-2-e

PART := xcu250-figd2104-2L-e

Line 48-49

#PLATFORM := xilinx_u200_xdma_201830_2

PLATFORM := xilinx_u250_gen3x16_xdma_3_1_202020_1

Note: no need and do not set clock constrain in “krnl_aes_test.xdc” file for Tool versions 2021.1, otherwise implementation error like below will occur.

Read this note and look inside Makefile & each TCL scripts to get idea for your own customization

IP Generation

IP Generation by Makefile and gen_ip.tcl script. Please a look inside these files to see how it works

make gen_ip

IP generation output message

tkas-user@tkas-d2101:~/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Desiggn_Tugn_Tugn_Tgngn_Tutgn_Tutggn_gn_Tggngn_Tutorials/05-bottom_up_rtl_kernel/krnl_aes$ make gen_ip

rm -rf ip_generation; mkdir ip_generation; vivado -mode batch -source ./gen_ip.tcl -tclargs xcu250-figd2104-2L-e

****** Vivado v2021.1 (64-bit)

**** SW Build 3247384 on Thu Jun 10 19:36:07 MDT 2021

**** IP Build 3246043 on Fri Jun 11 00:30:35 MDT 2021

** Copyright 1986-2021 Xilinx, Inc. All Rights Reserved.

source ./gen_ip.tcl

# set_part [lindex $argv 0]

INFO: [Coretcl 2-1500] The part has been set to 'xcu250-figd2104-2L-e' for the current project only. Run set_part -help for more details. To evaluate different speed grades in the current design, use the set_speed_grade command, or use the open_checkpoint -part command to change the part used by an existing checkpoint design.

# create_ip -name clk_wiz \

# -vendor xilinx.com \

# -library ip \

# -version 6.0 \

# -module_name clk_gen \

# -dir ./ip_generation

INFO: [IP_Flow 19-234] Refreshing IP repositories

INFO: [IP_Flow 19-1704] No user IP repositories specified

INFO: [IP_Flow 19-2313] Loaded Vivado IP repository '/tools/Xilinx/Vivado/2021.1/data/ip'.

create_ip: Time (s): cpu = 00:00:07 ; elapsed = 00:00:08 . Memory (MB): peak = 2972.422 ; gain = 416.820 ; free physical = 25643 ; free virtual = 36540

# set_property -dict [list CONFIG.USE_PHASE_ALIGNMENT {false} \

# CONFIG.PRIM_SOURCE {No_buffer} \

# CONFIG.PRIM_IN_FREQ {300.000} \

# CONFIG.CLKOUT1_REQUESTED_OUT_FREQ {400.000} \

# CONFIG.USE_RESET {false} \

# CONFIG.CLKOUT1_DRIVES {Buffer} \

# CONFIG.RESET_PORT {resetn}] \

# [get_ips clk_gen]

# generate_target all [get_files ./ip_generation/clk_gen/clk_gen.xci]

INFO: [IP_Flow 19-1686] Generating 'Instantiation Template' target for IP 'clk_gen'...

INFO: [IP_Flow 19-1686] Generating 'Synthesis' target for IP 'clk_gen'...

INFO: [IP_Flow 19-1686] Generating 'Simulation' target for IP 'clk_gen'...

INFO: [IP_Flow 19-1686] Generating 'Implementation' target for IP 'clk_gen'...

INFO: [IP_Flow 19-1686] Generating 'Change Log' target for IP 'clk_gen'...

# create_ip -name axis_clock_converter \

# -vendor xilinx.com \

# -library ip \

# -version 1.1 \

# -module_name axis_clock_converter \

# -dir ./ip_generation

# set_property -dict [list CONFIG.TDATA_NUM_BYTES {16} \

# CONFIG.IS_ACLK_ASYNC {1} \

# CONFIG.SYNCHRONIZATION_STAGES {3}] \

# [get_ips axis_clock_converter]

# generate_target all [get_files ./ip_generation/axis_clock_converter/axis_clock_converter.xci]

INFO: [IP_Flow 19-1686] Generating 'Instantiation Template' target for IP 'axis_clock_converter'...

INFO: [IP_Flow 19-1686] Generating 'Synthesis' target for IP 'axis_clock_converter'...

WARNING: [IP_Flow 19-4994] Overwriting existing constraint file '/home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Design_Tutorials/05-bottom_up_rtl_kernel/krnl_aes/ip_generation/axis_clock_converter/axis_clock_converter_ooc.xdc'

INFO: [IP_Flow 19-1686] Generating 'Simulation' target for IP 'axis_clock_converter'...

INFO: [IP_Flow 19-1686] Generating 'Change Log' target for IP 'axis_clock_converter'...

# create_ip -name axi_clock_converter \

# -vendor xilinx.com \

# -library ip \

# -version 2.1 \

# -module_name axi_clock_converter \

# -dir ./ip_generation

# set_property -dict [list CONFIG.PROTOCOL {AXI4LITE} \

# CONFIG.ADDR_WIDTH {12} \

# CONFIG.SYNCHRONIZATION_STAGES {3} \

# CONFIG.DATA_WIDTH {32} \

# CONFIG.ID_WIDTH {0} \

# CONFIG.AWUSER_WIDTH {0} \

# CONFIG.ARUSER_WIDTH {0} \

# CONFIG.RUSER_WIDTH {0} \

# CONFIG.WUSER_WIDTH {0} \

# CONFIG.BUSER_WIDTH {0}] \

# [get_ips axi_clock_converter]

# generate_target all [get_files ./ip_generation/axi_clock_converter/axi_clock_converter.xci]

INFO: [IP_Flow 19-1686] Generating 'Instantiation Template' target for IP 'axi_clock_converter'...

INFO: [IP_Flow 19-1686] Generating 'Synthesis' target for IP 'axi_clock_converter'...

WARNING: [IP_Flow 19-4994] Overwriting existing constraint file '/home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Design_Tutorials/05-bottom_up_rtl_kernel/krnl_aes/ip_generation/axi_clock_converter/axi_clock_converter_ooc.xdc'

INFO: [IP_Flow 19-1686] Generating 'Simulation' target for IP 'axi_clock_converter'...

INFO: [IP_Flow 19-5611] Unable to find an associated reset port for the interface 'S_AXI'. A default connection has been created.

INFO: [IP_Flow 19-5611] Unable to find an associated reset port for the interface 'M_AXI'. A default connection has been created.

INFO: [IP_Flow 19-1686] Generating 'Implementation' target for IP 'axi_clock_converter'...

INFO: [IP_Flow 19-1686] Generating 'Change Log' target for IP 'axi_clock_converter'...

# create_ip -name axi4stream_vip \

# -vendor xilinx.com \

# -library ip \

# -version 1.1 \

# -module_name axis_vip_mst \

# -dir ./ip_generation

# set_property -dict [list CONFIG.INTERFACE_MODE {MASTER} \

# CONFIG.TDATA_NUM_BYTES {16}] \

# [get_ips axis_vip_mst]

# generate_target all [get_files ./ip_generation/axis_vip_mst/axis_vip_mst.xci]

INFO: [IP_Flow 19-1686] Generating 'Instantiation Template' target for IP 'axis_vip_mst'...

INFO: [IP_Flow 19-1686] Generating 'Synthesis' target for IP 'axis_vip_mst'...

INFO: [IP_Flow 19-1686] Generating 'Simulation' target for IP 'axis_vip_mst'...

INFO: [IP_Flow 19-1686] Generating 'Change Log' target for IP 'axis_vip_mst'...

# create_ip -name axi4stream_vip \

# -vendor xilinx.com \

# -library ip \

# -version 1.1 \

# -module_name axis_vip_slv \

# -dir ./ip_generation

# set_property -dict [list CONFIG.INTERFACE_MODE {SLAVE} \

# CONFIG.TDATA_NUM_BYTES {16}] \

# [get_ips axis_vip_slv]

# generate_target all [get_files ./ip_generation/axis_vip_slv/axis_vip_slv.xci]

INFO: [IP_Flow 19-1686] Generating 'Instantiation Template' target for IP 'axis_vip_slv'...

INFO: [IP_Flow 19-1686] Generating 'Synthesis' target for IP 'axis_vip_slv'...

INFO: [IP_Flow 19-1686] Generating 'Simulation' target for IP 'axis_vip_slv'...

INFO: [IP_Flow 19-1686] Generating 'Change Log' target for IP 'axis_vip_slv'...

# create_ip -name axi_vip \

# -vendor xilinx.com \

# -library ip \

# -version 1.1 \

# -module_name axi_vip_mst \

# -dir ./ip_generation

# set_property -dict [list CONFIG.INTERFACE_MODE {MASTER} \

# CONFIG.PROTOCOL {AXI4LITE} \

# CONFIG.SUPPORTS_NARROW {0} \

# CONFIG.HAS_BURST {0} \

# CONFIG.HAS_LOCK {0} \

# CONFIG.HAS_CACHE {0} \

# CONFIG.HAS_REGION {0} \

# CONFIG.HAS_QOS {0} \

# CONFIG.HAS_PROT {0} \

# CONFIG.HAS_WSTRB {1}] \

# [get_ips axi_vip_mst]

# generate_target all [get_files ./ip_generation/axi_vip_mst/axi_vip_mst.xci]

INFO: [IP_Flow 19-1686] Generating 'Instantiation Template' target for IP 'axi_vip_mst'...

INFO: [IP_Flow 19-1686] Generating 'Synthesis' target for IP 'axi_vip_mst'...

INFO: [IP_Flow 19-1686] Generating 'Simulation' target for IP 'axi_vip_mst'...

INFO: [IP_Flow 19-1686] Generating 'Change Log' target for IP 'axi_vip_mst'...

INFO: [Common 17-206] Exiting Vivado at Sun Mar 20 13:36:28 2022...

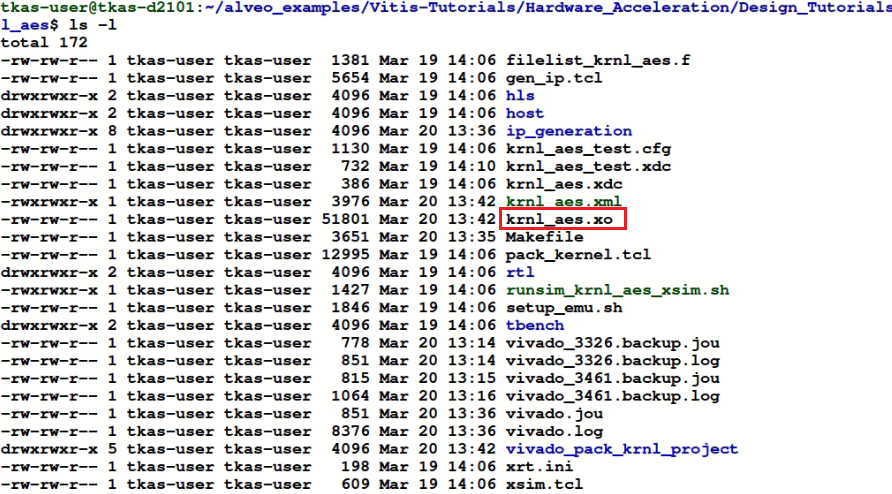

Pack the Design into Vivado IP and Vitis Kernel (.XO file)

make pack_kernel

Output message

tkas-user@tkas-d2101:~/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Design_Tutorials/05-bottom_up_rtl_kernel/krnl_aes$ make pack_kernel

rm -rf vivado_pack_krnl_project; mkdir vivado_pack_krnl_project; cd vivado_pack_krnl_project; vivado -mode batch -source ../pack_kernel.tcl -tclargs xcu250-figd2104-2L-e

****** Vivado v2021.1 (64-bit)

**** SW Build 3247384 on Thu Jun 10 19:36:07 MDT 2021

**** IP Build 3246043 on Fri Jun 11 00:30:35 MDT 2021

** Copyright 1986-2021 Xilinx, Inc. All Rights Reserved.

source ../pack_kernel.tcl

# create_project krnl_aes ./krnl_aes -part [lindex $argv 0]

# add_files -norecurse \

# { \

# ../rtl/aes_wrapper.sv \

# ../rtl/axis_interface.sv \

# ../rtl/krnl_aes_axi_ctrl_slave.v \

# ../rtl/krnl_aes.sv \

# ../../aes/rtl/AesControl.v \

# ../../aes/rtl/AesDecipher.v \

# ../../aes/rtl/AesEncipher.v \

# ../../aes/rtl/AesInvMixColumns.v \

# ../../aes/rtl/AesInvShiftRows.v \

# ../../aes/rtl/AesInvSubBytes.v \

# ../../aes/rtl/AesKeyExpansion.v \

# ../../aes/rtl/AesMixColumns.v \

# ../../aes/rtl/AesShiftRows.v \

# ../../aes/rtl/AesSubBytes.v \

# ../../aes/rtl/Aes.v \

# ../../aes/rtl/SPSR.v \

# ../ip_generation/clk_gen/clk_gen.xci \

# ../ip_generation/axi_clock_converter/axi_clock_converter.xci \

# ../ip_generation/axis_clock_converter/axis_clock_converter.xci \

# ../krnl_aes.xdc \

# }

INFO: [IP_Flow 19-234] Refreshing IP repositories

INFO: [IP_Flow 19-1704] No user IP repositories specified

INFO: [IP_Flow 19-2313] Loaded Vivado IP repository '/tools/Xilinx/Vivado/2021.1/data/ip'.

# update_compile_order -fileset sources_1

# ipx::package_project -root_dir ./krnl_aes_ip -vendor xilinx.com -library user -taxonomy /UserIP -import_files -set_current true

WARNING: [IP_Flow 19-5101] Packaging a component with a SystemVerilog top file is not fully supported. Please refer to UG1118 'Creating and Packaging Custom IP'.

INFO: [IP_Flow 19-5107] Inferred bus interface 'axis_mst0' of definition 'xilinx.com:interface:axis:1.0' (from Xilinx Repository).

INFO: [IP_Flow 19-5107] Inferred bus interface 'axis_mst1' of definition 'xilinx.com:interface:axis:1.0' (from Xilinx Repository).

INFO: [IP_Flow 19-5107] Inferred bus interface 'axis_mst2' of definition 'xilinx.com:interface:axis:1.0' (from Xilinx Repository).

INFO: [IP_Flow 19-5107] Inferred bus interface 'axis_mst3' of definition 'xilinx.com:interface:axis:1.0' (from Xilinx Repository).

INFO: [IP_Flow 19-5107] Inferred bus interface 'axis_slv0' of definition 'xilinx.com:interface:axis:1.0' (from Xilinx Repository).

INFO: [IP_Flow 19-5107] Inferred bus interface 'axis_slv1' of definition 'xilinx.com:interface:axis:1.0' (from Xilinx Repository).

INFO: [IP_Flow 19-5107] Inferred bus interface 'axis_slv2' of definition 'xilinx.com:interface:axis:1.0' (from Xilinx Repository).

INFO: [IP_Flow 19-5107] Inferred bus interface 'axis_slv3' of definition 'xilinx.com:interface:axis:1.0' (from Xilinx Repository).

INFO: [IP_Flow 19-5107] Inferred bus interface 's_axi_control' of definition 'xilinx.com:interface:aximm:1.0' (from Xilinx Repository).

INFO: [IP_Flow 19-5107] Inferred bus interface 'ap_rst_n' of definition 'xilinx.com:signal:reset:1.0' (from Xilinx Repository).

INFO: [IP_Flow 19-5107] Inferred bus interface 'ap_clk' of definition 'xilinx.com:signal:clock:1.0' (from Xilinx Repository).

INFO: [IP_Flow 19-4728] Bus Interface 'ap_rst_n': Added interface parameter 'POLARITY' with value 'ACTIVE_LOW'.

INFO: [IP_Flow 19-4728] Bus Interface 'ap_clk': Added interface parameter 'ASSOCIATED_RESET' with value 'ap_rst_n'.

WARNING: [IP_Flow 19-3158] Bus Interface 'axis_mst0': FREQ_HZ bus parameter missing from AXI interface when interface is not associated to a clock.

WARNING: [IP_Flow 19-3158] Bus Interface 'axis_mst1': FREQ_HZ bus parameter missing from AXI interface when interface is not associated to a clock.

WARNING: [IP_Flow 19-3158] Bus Interface 'axis_mst2': FREQ_HZ bus parameter missing from AXI interface when interface is not associated to a clock.

WARNING: [IP_Flow 19-3158] Bus Interface 'axis_mst3': FREQ_HZ bus parameter missing from AXI interface when interface is not associated to a clock.

WARNING: [IP_Flow 19-3158] Bus Interface 'axis_slv0': FREQ_HZ bus parameter missing from AXI interface when interface is not associated to a clock.

WARNING: [IP_Flow 19-3158] Bus Interface 'axis_slv1': FREQ_HZ bus parameter missing from AXI interface when interface is not associated to a clock.

WARNING: [IP_Flow 19-3158] Bus Interface 'axis_slv2': FREQ_HZ bus parameter missing from AXI interface when interface is not associated to a clock.

WARNING: [IP_Flow 19-3158] Bus Interface 'axis_slv3': FREQ_HZ bus parameter missing from AXI interface when interface is not associated to a clock.

WARNING: [IP_Flow 19-3158] Bus Interface 's_axi_control': FREQ_HZ bus parameter missing from AXI interface when interface is not associated to a clock.

WARNING: [IP_Flow 19-3157] Bus Interface 'ap_rst_n': Bus parameter POLARITY is ACTIVE_LOW but port 'ap_rst_n' is not *resetn - please double check the POLARITY setting.

WARNING: [IP_Flow 19-5661] Bus Interface 'ap_clk' does not have any bus interfaces associated with it.

INFO: [IP_Flow 19-2181] Payment Required is not set for this core.

INFO: [IP_Flow 19-2187] The Product Guide file is missing.

# ipx::infer_bus_interface ap_clk xilinx.com:signal:clock_rtl:1.0 [ipx::current_core]

INFO: [IP_Flow 19-5107] Inferred bus interface 'ap_clk' of definition 'xilinx.com:signal:clock:1.0' (from TCL Argument).

# ipx::infer_bus_interface ap_rst_n xilinx.com:signal:reset_rtl:1.0 [ipx::current_core]

INFO: [IP_Flow 19-5107] Inferred bus interface 'ap_rst_n' of definition 'xilinx.com:signal:reset:1.0' (from TCL Argument).

# ipx::associate_bus_interfaces -busif s_axi_control -clock ap_clk [ipx::current_core]

INFO: [IP_Flow 19-4728] Bus Interface 'ap_clk': Added interface parameter 'ASSOCIATED_BUSIF' with value 's_axi_control'.

# ipx::associate_bus_interfaces -busif axis_mst0 -clock ap_clk [ipx::current_core]

# ipx::associate_bus_interfaces -busif axis_mst1 -clock ap_clk [ipx::current_core]

# ipx::associate_bus_interfaces -busif axis_mst2 -clock ap_clk [ipx::current_core]

# ipx::associate_bus_interfaces -busif axis_mst3 -clock ap_clk [ipx::current_core]

# ipx::associate_bus_interfaces -busif axis_slv0 -clock ap_clk [ipx::current_core]

# ipx::associate_bus_interfaces -busif axis_slv1 -clock ap_clk [ipx::current_core]

# ipx::associate_bus_interfaces -busif axis_slv2 -clock ap_clk [ipx::current_core]

# ipx::associate_bus_interfaces -busif axis_slv3 -clock ap_clk [ipx::current_core]

# ipx::associate_bus_interfaces -clock ap_clk -reset ap_rst_n [ipx::current_core]

# ipx::add_register CTRL [ipx::get_address_blocks reg0 -of_objects [ipx::get_memory_maps s_axi_control -of_objects [ipx::current_core]]]

# ipx::add_register MODE [ipx::get_address_blocks reg0 -of_objects [ipx::get_memory_maps s_axi_control -of_objects [ipx::current_core]]]

# ipx::add_register KEY_LEN [ipx::get_address_blocks reg0 -of_objects [ipx::get_memory_maps s_axi_control -of_objects [ipx::current_core]]]

# ipx::add_register STATUS [ipx::get_address_blocks reg0 -of_objects [ipx::get_memory_maps s_axi_control -of_objects [ipx::current_core]]]

# ipx::add_register KEY_W7 [ipx::get_address_blocks reg0 -of_objects [ipx::get_memory_maps s_axi_control -of_objects [ipx::current_core]]]

# ipx::add_register KEY_W6 [ipx::get_address_blocks reg0 -of_objects [ipx::get_memory_maps s_axi_control -of_objects [ipx::current_core]]]

# ipx::add_register KEY_W5 [ipx::get_address_blocks reg0 -of_objects [ipx::get_memory_maps s_axi_control -of_objects [ipx::current_core]]]

# ipx::add_register KEY_W4 [ipx::get_address_blocks reg0 -of_objects [ipx::get_memory_maps s_axi_control -of_objects [ipx::current_core]]]

# ipx::add_register KEY_W3 [ipx::get_address_blocks reg0 -of_objects [ipx::get_memory_maps s_axi_control -of_objects [ipx::current_core]]]

# ipx::add_register KEY_W2 [ipx::get_address_blocks reg0 -of_objects [ipx::get_memory_maps s_axi_control -of_objects [ipx::current_core]]]

# ipx::add_register KEY_W1 [ipx::get_address_blocks reg0 -of_objects [ipx::get_memory_maps s_axi_control -of_objects [ipx::current_core]]]

# ipx::add_register KEY_W0 [ipx::get_address_blocks reg0 -of_objects [ipx::get_memory_maps s_axi_control -of_objects [ipx::current_core]]]

# set_property description {Control Signals} [ipx::get_registers CTRL -of_objects [ipx::get_address_blocks reg0 -of_objects [ipx::get_memory_maps s_axi_control -of_objects [ipx::current_core]]]]

# set_property address_offset {0x000} [ipx::get_registers CTRL -of_objects [ipx::get_address_blocks reg0 -of_objects [ipx::get_memory_maps s_axi_control -of_objects [ipx::current_core]]]]

# set_property size {32} [ipx::get_registers CTRL -of_objects [ipx::get_address_blocks reg0 -of_objects [ipx::get_memory_maps s_axi_control -of_objects [ipx::current_core]]]]

# set_property description {AES working mode} [ipx::get_registers MODE -of_objects [ipx::get_address_blocks reg0 -of_objects [ipx::get_memory_maps s_axi_control -of_objects [ipx::current_core]]]]

# set_property address_offset {0x010} [ipx::get_registers MODE -of_objects [ipx::get_address_blocks reg0 -of_objects [ipx::get_memory_maps s_axi_control -of_objects [ipx::current_core]]]]

# set_property size {32} [ipx::get_registers MODE -of_objects [ipx::get_address_blocks reg0 -of_objects [ipx::get_memory_maps s_axi_control -of_objects [ipx::current_core]]]]

# set_property description {AES key length} [ipx::get_registers KEY_LEN -of_objects [ipx::get_address_blocks reg0 -of_objects [ipx::get_memory_maps s_axi_control -of_objects [ipx::current_core]]]]

# set_property address_offset {0x018} [ipx::get_registers KEY_LEN -of_objects [ipx::get_address_blocks reg0 -of_objects [ipx::get_memory_maps s_axi_control -of_objects [ipx::current_core]]]]

# set_property size {32} [ipx::get_registers KEY_LEN -of_objects [ipx::get_address_blocks reg0 -of_objects [ipx::get_memory_maps s_axi_control -of_objects [ipx::current_core]]]]

# set_property description {AES engine status} [ipx::get_registers STATUS -of_objects [ipx::get_address_blocks reg0 -of_objects [ipx::get_memory_maps s_axi_control -of_objects [ipx::current_core]]]]

# set_property address_offset {0x020} [ipx::get_registers STATUS -of_objects [ipx::get_address_blocks reg0 -of_objects [ipx::get_memory_maps s_axi_control -of_objects [ipx::current_core]]]]

# set_property size {32} [ipx::get_registers STATUS -of_objects [ipx::get_address_blocks reg0 -of_objects [ipx::get_memory_maps s_axi_control -of_objects [ipx::current_core]]]]

# set_property description {AES key word 7} [ipx::get_registers KEY_W7 -of_objects [ipx::get_address_blocks reg0 -of_objects [ipx::get_memory_maps s_axi_control -of_objects [ipx::current_core]]]]

# set_property address_offset {0x028} [ipx::get_registers KEY_W7 -of_objects [ipx::get_address_blocks reg0 -of_objects [ipx::get_memory_maps s_axi_control -of_objects [ipx::current_core]]]]

# set_property size {32} [ipx::get_registers KEY_W7 -of_objects [ipx::get_address_blocks reg0 -of_objects [ipx::get_memory_maps s_axi_control -of_objects [ipx::current_core]]]]

# set_property description {AES key word 6} [ipx::get_registers KEY_W6 -of_objects [ipx::get_address_blocks reg0 -of_objects [ipx::get_memory_maps s_axi_control -of_objects [ipx::current_core]]]]

# set_property address_offset {0x030} [ipx::get_registers KEY_W6 -of_objects [ipx::get_address_blocks reg0 -of_objects [ipx::get_memory_maps s_axi_control -of_objects [ipx::current_core]]]]

# set_property size {32} [ipx::get_registers KEY_W6 -of_objects [ipx::get_address_blocks reg0 -of_objects [ipx::get_memory_maps s_axi_control -of_objects [ipx::current_core]]]]

# set_property description {AES key word 5} [ipx::get_registers KEY_W5 -of_objects [ipx::get_address_blocks reg0 -of_objects [ipx::get_memory_maps s_axi_control -of_objects [ipx::current_core]]]]

# set_property address_offset {0x038} [ipx::get_registers KEY_W5 -of_objects [ipx::get_address_blocks reg0 -of_objects [ipx::get_memory_maps s_axi_control -of_objects [ipx::current_core]]]]

# set_property size {32} [ipx::get_registers KEY_W5 -of_objects [ipx::get_address_blocks reg0 -of_objects [ipx::get_memory_maps s_axi_control -of_objects [ipx::current_core]]]]

# set_property description {AES key word 4} [ipx::get_registers KEY_W4 -of_objects [ipx::get_address_blocks reg0 -of_objects [ipx::get_memory_maps s_axi_control -of_objects [ipx::current_core]]]]

# set_property address_offset {0x040} [ipx::get_registers KEY_W4 -of_objects [ipx::get_address_blocks reg0 -of_objects [ipx::get_memory_maps s_axi_control -of_objects [ipx::current_core]]]]

# set_property size {32} [ipx::get_registers KEY_W4 -of_objects [ipx::get_address_blocks reg0 -of_objects [ipx::get_memory_maps s_axi_control -of_objects [ipx::current_core]]]]

# set_property description {AES key word 3} [ipx::get_registers KEY_W3 -of_objects [ipx::get_address_blocks reg0 -of_objects [ipx::get_memory_maps s_axi_control -of_objects [ipx::current_core]]]]

# set_property address_offset {0x048} [ipx::get_registers KEY_W3 -of_objects [ipx::get_address_blocks reg0 -of_objects [ipx::get_memory_maps s_axi_control -of_objects [ipx::current_core]]]]

# set_property size {32} [ipx::get_registers KEY_W3 -of_objects [ipx::get_address_blocks reg0 -of_objects [ipx::get_memory_maps s_axi_control -of_objects [ipx::current_core]]]]

# set_property description {AES key word 2} [ipx::get_registers KEY_W2 -of_objects [ipx::get_address_blocks reg0 -of_objects [ipx::get_memory_maps s_axi_control -of_objects [ipx::current_core]]]]

# set_property address_offset {0x050} [ipx::get_registers KEY_W2 -of_objects [ipx::get_address_blocks reg0 -of_objects [ipx::get_memory_maps s_axi_control -of_objects [ipx::current_core]]]]

# set_property size {32} [ipx::get_registers KEY_W2 -of_objects [ipx::get_address_blocks reg0 -of_objects [ipx::get_memory_maps s_axi_control -of_objects [ipx::current_core]]]]

# set_property description {AES key word 1} [ipx::get_registers KEY_W1 -of_objects [ipx::get_address_blocks reg0 -of_objects [ipx::get_memory_maps s_axi_control -of_objects [ipx::current_core]]]]

# set_property address_offset {0x058} [ipx::get_registers KEY_W1 -of_objects [ipx::get_address_blocks reg0 -of_objects [ipx::get_memory_maps s_axi_control -of_objects [ipx::current_core]]]]

# set_property size {32} [ipx::get_registers KEY_W1 -of_objects [ipx::get_address_blocks reg0 -of_objects [ipx::get_memory_maps s_axi_control -of_objects [ipx::current_core]]]]

# set_property description {AES key word 0} [ipx::get_registers KEY_W0 -of_objects [ipx::get_address_blocks reg0 -of_objects [ipx::get_memory_maps s_axi_control -of_objects [ipx::current_core]]]]

# set_property address_offset {0x060} [ipx::get_registers KEY_W0 -of_objects [ipx::get_address_blocks reg0 -of_objects [ipx::get_memory_maps s_axi_control -of_objects [ipx::current_core]]]]

# set_property size {32} [ipx::get_registers KEY_W0 -of_objects [ipx::get_address_blocks reg0 -of_objects [ipx::get_memory_maps s_axi_control -of_objects [ipx::current_core]]]]

# set_property sdx_kernel true [ipx::current_core]

# set_property sdx_kernel_type rtl [ipx::current_core]

# ipx::update_source_project_archive -component [ipx::current_core]

# ipx::save_core [ipx::current_core]

# package_xo -force -xo_path ../krnl_aes.xo -kernel_name krnl_aes -ctrl_protocol ap_ctrl_hs -ip_directory ./krnl_aes_ip -output_kernel_xml ../krnl_aes.xml

WARNING: [Vivado 12-4404] The CPU emulation flow in v++ is only supported when using a packaged XO file that contains C-model files, none were found.

WARNING: [IP_Flow 19-3157] Bus Interface 'ap_rst_n': Bus parameter POLARITY is ACTIVE_LOW but port 'ap_rst_n' is not *resetn - please double check the POLARITY setting.

INFO: [IP_Flow 19-2181] Payment Required is not set for this core.

INFO: [IP_Flow 19-2187] The Product Guide file is missing.

INFO: [Ipptcl 7-1486] check_integrity: Integrity check passed.

INFO: [Common 17-206] Exiting Vivado at Sun Mar 20 13:42:54 2022...

This starts Vivado in batch mode and calls ~/krnl_aes/pack_kernel.tcl to package the RTL sources, generated IP XCI files, and XDC files into Vivado IP. It then generates the Vitis kernel file ~/krnl_aes/krnl_aes.xo.

Build for hardware target

make build_hw

Build output message. It will take around 1 hour 4 minutes (From 15:47 to 16:51)

tkas-user@tkas-d2101:~/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Design_Tutorials/05-bottom_up_rtl_kernel/krnl_aes$ make build_hw

v++ --link --optimize 3 --vivado.synth.jobs 15 --vivado.impl.jobs 15 --platform xilinx_u250_gen3x16_xdma_3_1_202020_1 -t hw -s -g --config krnl_aes_test.cfg -o krnl_aes_test_hw.xclbin krnl_aes.xo strm_dump.xo strm_issue.xo

Option Map File Used: '/tools/Xilinx/Vitis/2021.1/data/vitis/vpp/optMap.xml'

****** v++ v2021.1 (64-bit)

**** SW Build 3246112 on 2021-06-09-14:19:56

** Copyright 1986-2020 Xilinx, Inc. All Rights Reserved.

INFO: [v++ 60-1306] Additional information associated with this v++ link can be found at:

Reports: /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Design_Tutorials/05-bottom_up_rtl_kernel/krnl_aes/_x/reports/link

Log files: /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Design_Tutorials/05-bottom_up_rtl_kernel/krnl_aes/_x/logs/link

Running Dispatch Server on port: 35047

INFO: [v++ 60-1548] Creating build summary session with primary output /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Design_Tutorials/05-bottom_up_rtl_kernel/krnl_aes/krnl_aes_test_hw.xclbin.link_summary, at Sun Mar 20 15:47:26 2022

INFO: [v++ 60-1316] Initiating connection to rulecheck server, at Sun Mar 20 15:47:26 2022

Running Rule Check Server on port:34523

INFO: [v++ 60-1315] Creating rulecheck session with output '/home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Design_Tutorials/05-bottom_up_rtl_kernel/krnl_aes/_x/reports/link/v++_link_krnl_aes_test_hw_guidance.html', at Sun Mar 20 15:47:27 2022

INFO: [v++ 60-895] Target platform: /opt/xilinx/platforms/xilinx_u250_gen3x16_xdma_3_1_202020_1/xilinx_u250_gen3x16_xdma_3_1_202020_1.xpfm

INFO: [v++ 60-1578] This platform contains Xilinx Shell Archive '/opt/xilinx/platforms/xilinx_u250_gen3x16_xdma_3_1_202020_1/hw/hw.xsa'

INFO: [v++ 74-78] Compiler Version string: 2021.1

INFO: [v++ 60-629] Linking for hardware target

INFO: [v++ 60-423] Target device: xilinx_u250_gen3x16_xdma_3_1_202020_1

INFO: [v++ 60-1332] Run 'run_link' status: Not started

INFO: [v++ 60-1443] [15:47:28] Run run_link: Step system_link: Started

INFO: [v++ 60-1453] Command Line: system_link --xo /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Design_Tutorials/05-bottom_up_rtl_kernel/krnl_aes/krnl_aes.xo --xo /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Design_Tutorials/05-bottom_up_rtl_kernel/krnl_aes/strm_dump.xo --xo /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Design_Tutorials/05-bottom_up_rtl_kernel/krnl_aes/strm_issue.xo -keep --config /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Design_Tutorials/05-bottom_up_rtl_kernel/krnl_aes/_x/link/int/syslinkConfig.ini --xpfm /opt/xilinx/platforms/xilinx_u250_gen3x16_xdma_3_1_202020_1/xilinx_u250_gen3x16_xdma_3_1_202020_1.xpfm --target hw --output_dir /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Design_Tutorials/05-bottom_up_rtl_kernel/krnl_aes/_x/link/int --temp_dir /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Design_Tutorials/05-bottom_up_rtl_kernel/krnl_aes/_x/link/sys_link

INFO: [v++ 60-1454] Run Directory: /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Design_Tutorials/05-bottom_up_rtl_kernel/krnl_aes/_x/link/run_link

INFO: [SYSTEM_LINK 60-1316] Initiating connection to rulecheck server, at Sun Mar 20 15:47:30 2022

INFO: [SYSTEM_LINK 82-70] Extracting xo v3 file /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Design_Tutorials/05-bottom_up_rtl_kernel/krnl_aes/krnl_aes.xo

INFO: [SYSTEM_LINK 82-70] Extracting xo v3 file /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Design_Tutorials/05-bottom_up_rtl_kernel/krnl_aes/strm_dump.xo

INFO: [SYSTEM_LINK 82-70] Extracting xo v3 file /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Design_Tutorials/05-bottom_up_rtl_kernel/krnl_aes/strm_issue.xo

INFO: [SYSTEM_LINK 82-53] Creating IP database /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Design_Tutorials/05-bottom_up_rtl_kernel/krnl_aes/_x/link/sys_link/_sysl/.cdb/xd_ip_db.xml

INFO: [SYSTEM_LINK 82-38] [15:47:30] build_xd_ip_db started: /tools/Xilinx/Vitis/2021.1/bin/build_xd_ip_db -ip_search 0 -sds-pf /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Design_Tutorials/05-bottom_up_rtl_kernel/krnl_aes/_x/link/sys_link/hw.hpfm -clkid 0 -ip /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Design_Tutorials/05-bottom_up_rtl_kernel/krnl_aes/_x/link/sys_link/iprepo/xilinx_com_hls_strm_issue_1_0,strm_issue -ip /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Design_Tutorials/05-bottom_up_rtl_kernel/krnl_aes/_x/link/sys_link/iprepo/xilinx_com_user_krnl_aes_1_0,krnl_aes -ip /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Design_Tutorials/05-bottom_up_rtl_kernel/krnl_aes/_x/link/sys_link/iprepo/xilinx_com_hls_strm_dump_1_0,strm_dump -o /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Design_Tutorials/05-bottom_up_rtl_kernel/krnl_aes/_x/link/sys_link/_sysl/.cdb/xd_ip_db.xml

INFO: [SYSTEM_LINK 82-37] [15:47:33] build_xd_ip_db finished successfully

Time (s): cpu = 00:00:04 ; elapsed = 00:00:03 . Memory (MB): peak = 2004.715 ; gain = 0.000 ; free physical = 27450 ; free virtual = 37716

INFO: [SYSTEM_LINK 82-51] Create system connectivity graph

INFO: [SYSTEM_LINK 82-102] Applying explicit connections to the system connectivity graph: /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Design_Tutorials/05-bottom_up_rtl_kernel/krnl_aes/_x/link/sys_link/cfgraph/cfgen_cfgraph.xml

INFO: [SYSTEM_LINK 82-38] [15:47:33] cfgen started: /tools/Xilinx/Vitis/2021.1/bin/cfgen -nk strm_dump:4 -nk strm_issue:4 -sc krnl_aes_1.axis_mst0:strm_dump_1.data_input -sc krnl_aes_1.axis_mst1:strm_dump_2.data_input -sc krnl_aes_1.axis_mst2:strm_dump_3.data_input -sc krnl_aes_1.axis_mst3:strm_dump_4.data_input -sc strm_issue_1.data_output:krnl_aes_1.axis_slv0 -sc strm_issue_2.data_output:krnl_aes_1.axis_slv1 -sc strm_issue_3.data_output:krnl_aes_1.axis_slv2 -sc strm_issue_4.data_output:krnl_aes_1.axis_slv3 -slr strm_dump_1:SLR0 -slr strm_dump_2:SLR0 -slr strm_dump_3:SLR0 -slr strm_dump_4:SLR0 -slr strm_issue_1:SLR0 -slr strm_issue_2:SLR0 -slr strm_issue_3:SLR0 -slr strm_issue_4:SLR0 -slr krnl_aes_1:SLR0 -dmclkid 0 -r /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Design_Tutorials/05-bottom_up_rtl_kernel/krnl_aes/_x/link/sys_link/_sysl/.cdb/xd_ip_db.xml -o /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Design_Tutorials/05-bottom_up_rtl_kernel/krnl_aes/_x/link/sys_link/cfgraph/cfgen_cfgraph.xml

INFO: [CFGEN 83-0] Kernel Specs:

INFO: [CFGEN 83-0] kernel: strm_dump, num: 4 {strm_dump_1 strm_dump_2 strm_dump_3 strm_dump_4}

INFO: [CFGEN 83-0] kernel: strm_issue, num: 4 {strm_issue_1 strm_issue_2 strm_issue_3 strm_issue_4}

INFO: [CFGEN 83-0] kernel: krnl_aes, num: 1 {krnl_aes_1}

INFO: [CFGEN 83-0] Stream Specs:

INFO: [CFGEN 83-0] krnl_aes_1.axis_mst0 => strm_dump_1.data_input

INFO: [CFGEN 83-0] krnl_aes_1.axis_mst1 => strm_dump_2.data_input

INFO: [CFGEN 83-0] krnl_aes_1.axis_mst2 => strm_dump_3.data_input

INFO: [CFGEN 83-0] krnl_aes_1.axis_mst3 => strm_dump_4.data_input

INFO: [CFGEN 83-0] strm_issue_1.data_output => krnl_aes_1.axis_slv0

INFO: [CFGEN 83-0] strm_issue_2.data_output => krnl_aes_1.axis_slv1

INFO: [CFGEN 83-0] strm_issue_3.data_output => krnl_aes_1.axis_slv2

INFO: [CFGEN 83-0] strm_issue_4.data_output => krnl_aes_1.axis_slv3

INFO: [CFGEN 83-0] SLR Specs:

INFO: [CFGEN 83-0] instance: krnl_aes_1, SLR: SLR0

INFO: [CFGEN 83-0] instance: strm_dump_1, SLR: SLR0

INFO: [CFGEN 83-0] instance: strm_dump_2, SLR: SLR0

INFO: [CFGEN 83-0] instance: strm_dump_3, SLR: SLR0

INFO: [CFGEN 83-0] instance: strm_dump_4, SLR: SLR0

INFO: [CFGEN 83-0] instance: strm_issue_1, SLR: SLR0

INFO: [CFGEN 83-0] instance: strm_issue_2, SLR: SLR0

INFO: [CFGEN 83-0] instance: strm_issue_3, SLR: SLR0

INFO: [CFGEN 83-0] instance: strm_issue_4, SLR: SLR0

INFO: [CFGEN 83-2226] Inferring mapping for argument strm_dump_1.data_output to DDR[1]

INFO: [CFGEN 83-2226] Inferring mapping for argument strm_dump_2.data_output to DDR[1]

INFO: [CFGEN 83-2226] Inferring mapping for argument strm_dump_3.data_output to DDR[1]

INFO: [CFGEN 83-2226] Inferring mapping for argument strm_dump_4.data_output to DDR[1]

INFO: [CFGEN 83-2226] Inferring mapping for argument strm_issue_1.data_input to DDR[1]

INFO: [CFGEN 83-2226] Inferring mapping for argument strm_issue_2.data_input to DDR[1]

INFO: [CFGEN 83-2226] Inferring mapping for argument strm_issue_3.data_input to DDR[1]

INFO: [CFGEN 83-2226] Inferring mapping for argument strm_issue_4.data_input to DDR[1]

INFO: [SYSTEM_LINK 82-37] [15:47:36] cfgen finished successfully

Time (s): cpu = 00:00:03 ; elapsed = 00:00:03 . Memory (MB): peak = 2004.715 ; gain = 0.000 ; free physical = 27449 ; free virtual = 37715

INFO: [SYSTEM_LINK 82-52] Create top-level block diagram

INFO: [SYSTEM_LINK 82-38] [15:47:36] cf2bd started: /tools/Xilinx/Vitis/2021.1/bin/cf2bd --linux --trace_buffer 1024 --input_file /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Design_Tutorials/05-bottom_up_rtl_kernel/krnl_aes/_x/link/sys_link/cfgraph/cfgen_cfgraph.xml --ip_db /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Design_Tutorials/05-bottom_up_rtl_kernel/krnl_aes/_x/link/sys_link/_sysl/.cdb/xd_ip_db.xml --cf_name dr --working_dir /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Design_Tutorials/05-bottom_up_rtl_kernel/krnl_aes/_x/link/sys_link/_sysl/.xsd --temp_dir /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Design_Tutorials/05-bottom_up_rtl_kernel/krnl_aes/_x/link/sys_link --output_dir /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Design_Tutorials/05-bottom_up_rtl_kernel/krnl_aes/_x/link/int --target_bd ulp.bd

INFO: [CF2BD 82-31] Launching cf2xd: cf2xd -linux -trace-buffer 1024 -i /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Design_Tutorials/05-bottom_up_rtl_kernel/krnl_aes/_x/link/sys_link/cfgraph/cfgen_cfgraph.xml -r /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Design_Tutorials/05-bottom_up_rtl_kernel/krnl_aes/_x/link/sys_link/_sysl/.cdb/xd_ip_db.xml -o dr.xml

INFO: [CF2BD 82-28] cf2xd finished successfully

INFO: [CF2BD 82-31] Launching cf_xsd: cf_xsd -disable-address-gen -bd ulp.bd -dn dr -dp /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Design_Tutorials/05-bottom_up_rtl_kernel/krnl_aes/_x/link/sys_link/_sysl/.xsd

INFO: [CF2BD 82-28] cf_xsd finished successfully

INFO: [SYSTEM_LINK 82-37] [15:47:40] cf2bd finished successfully

Time (s): cpu = 00:00:04 ; elapsed = 00:00:04 . Memory (MB): peak = 2004.715 ; gain = 0.000 ; free physical = 27433 ; free virtual = 37704

INFO: [v++ 60-1441] [15:47:40] Run run_link: Step system_link: Completed

Time (s): cpu = 00:00:13 ; elapsed = 00:00:12 . Memory (MB): peak = 1899.504 ; gain = 0.000 ; free physical = 27468 ; free virtual = 37739

INFO: [v++ 60-1443] [15:47:40] Run run_link: Step cf2sw: Started

INFO: [v++ 60-1453] Command Line: cf2sw -sdsl /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Design_Tutorials/05-bottom_up_rtl_kernel/krnl_aes/_x/link/int/sdsl.dat -rtd /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Design_Tutorials/05-bottom_up_rtl_kernel/krnl_aes/_x/link/int/cf2sw.rtd -nofilter /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Design_Tutorials/05-bottom_up_rtl_kernel/krnl_aes/_x/link/int/cf2sw_full.rtd -xclbin /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Design_Tutorials/05-bottom_up_rtl_kernel/krnl_aes/_x/link/int/xclbin_orig.xml -o /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Design_Tutorials/05-bottom_up_rtl_kernel/krnl_aes/_x/link/int/xclbin_orig.1.xml

INFO: [v++ 60-1454] Run Directory: /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Design_Tutorials/05-bottom_up_rtl_kernel/krnl_aes/_x/link/run_link

INFO: [v++ 60-1441] [15:47:45] Run run_link: Step cf2sw: Completed

Time (s): cpu = 00:00:05 ; elapsed = 00:00:05 . Memory (MB): peak = 1899.504 ; gain = 0.000 ; free physical = 27482 ; free virtual = 37753

INFO: [v++ 60-1443] [15:47:45] Run run_link: Step rtd2_system_diagram: Started

INFO: [v++ 60-1453] Command Line: rtd2SystemDiagram

INFO: [v++ 60-1454] Run Directory: /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Design_Tutorials/05-bottom_up_rtl_kernel/krnl_aes/_x/link/run_link

INFO: [v++ 60-1441] [15:47:45] Run run_link: Step rtd2_system_diagram: Completed

Time (s): cpu = 00:00:00 ; elapsed = 00:00:00.24 . Memory (MB): peak = 1899.504 ; gain = 0.000 ; free physical = 27466 ; free virtual = 37737

INFO: [v++ 60-1443] [15:47:45] Run run_link: Step vpl: Started

INFO: [v++ 60-1453] Command Line: vpl -t hw -f xilinx_u250_gen3x16_xdma_3_1_202020_1 -g --remote_ip_cache /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Design_Tutorials/05-bottom_up_rtl_kernel/krnl_aes/.ipcache -s --output_dir /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Design_Tutorials/05-bottom_up_rtl_kernel/krnl_aes/_x/link/int --log_dir /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Design_Tutorials/05-bottom_up_rtl_kernel/krnl_aes/_x/logs/link --report_dir /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Design_Tutorials/05-bottom_up_rtl_kernel/krnl_aes/_x/reports/link --config /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Design_Tutorials/05-bottom_up_rtl_kernel/krnl_aes/_x/link/int/vplConfig.ini -k /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Design_Tutorials/05-bottom_up_rtl_kernel/krnl_aes/_x/link/int/kernel_info.dat --webtalk_flag Vitis --temp_dir /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Design_Tutorials/05-bottom_up_rtl_kernel/krnl_aes/_x/link --no-info --iprepo /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Design_Tutorials/05-bottom_up_rtl_kernel/krnl_aes/_x/link/int/xo/ip_repo/xilinx_com_hls_strm_issue_1_0 --iprepo /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Design_Tutorials/05-bottom_up_rtl_kernel/krnl_aes/_x/link/int/xo/ip_repo/xilinx_com_user_krnl_aes_1_0 --iprepo /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Design_Tutorials/05-bottom_up_rtl_kernel/krnl_aes/_x/link/int/xo/ip_repo/xilinx_com_hls_strm_dump_1_0 --messageDb /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Design_Tutorials/05-bottom_up_rtl_kernel/krnl_aes/_x/link/run_link/vpl.pb /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Design_Tutorials/05-bottom_up_rtl_kernel/krnl_aes/_x/link/int/dr.bd.tcl

INFO: [v++ 60-1454] Run Directory: /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Design_Tutorials/05-bottom_up_rtl_kernel/krnl_aes/_x/link/run_link

****** vpl v2021.1 (64-bit)

**** SW Build 3246112 on 2021-06-09-14:19:56

** Copyright 1986-2020 Xilinx, Inc. All Rights Reserved.

INFO: [VPL 60-839] Read in kernel information from file '/home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Design_Tutorials/05-bottom_up_rtl_kernel/krnl_aes/_x/link/int/kernel_info.dat'.

INFO: [VPL 74-78] Compiler Version string: 2021.1

INFO: [VPL 60-423] Target device: xilinx_u250_gen3x16_xdma_3_1_202020_1

INFO: [VPL 60-1032] Extracting hardware platform to /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Design_Tutorials/05-bottom_up_rtl_kernel/krnl_aes/_x/link/vivado/vpl/.local/hw_platform

[15:47:55] Run vpl: Step create_project: Started

Creating Vivado project.

[15:47:55] Run vpl: Step create_project: Completed

[15:47:55] Run vpl: Step create_bd: Started

[15:48:19] Run vpl: Step create_bd: Completed

[15:48:19] Run vpl: Step update_bd: Started

[15:48:19] Run vpl: Step update_bd: Completed

[15:48:19] Run vpl: Step generate_target: Started

[15:49:07] Run vpl: Step generate_target: Completed

[15:49:07] Run vpl: Step config_hw_runs: Started

[15:49:09] Run vpl: Step config_hw_runs: Completed

[15:49:09] Run vpl: Step synth: Started

[15:49:40] Block-level synthesis in progress, 0 of 8 jobs complete, 1 job running.

[15:49:56] Run vpl: Step synth: Completed

[15:49:56] Run vpl: Step impl: Started

[15:54:57] Finished 2nd of 6 tasks (FPGA linking synthesized kernels to platform). Elapsed time: 00h 07m 10s

[15:54:57] Starting logic optimization..

[15:55:27] Phase 1 Retarget

[15:55:27] Phase 2 Constant propagation

[15:55:27] Phase 3 Sweep

[15:55:57] Phase 4 BUFG optimization

[15:55:57] Phase 5 Shift Register Optimization

[15:55:57] Phase 6 Post Processing Netlist

[15:57:28] Finished 3rd of 6 tasks (FPGA logic optimization). Elapsed time: 00h 02m 30s

[15:57:28] Starting logic placement..

[15:57:28] Phase 1 Placer Initialization

[15:57:28] Phase 1.1 Placer Initialization Netlist Sorting

[15:59:58] Phase 1.2 IO Placement/ Clock Placement/ Build Placer Device

[16:03:59] Phase 1.3 Build Placer Netlist Model

[16:04:59] Phase 1.4 Constrain Clocks/Macros

[16:04:59] Phase 2 Global Placement

[16:04:59] Phase 2.1 Floorplanning

[16:05:29] Phase 2.1.1 Partition Driven Placement

[16:05:59] Phase 2.1.1.1 PBP: Partition Driven Placement

[16:05:59] Phase 2.1.1.2 PBP: Clock Region Placement

[16:06:59] Phase 2.1.1.3 PBP: Compute Congestion

[16:06:59] Phase 2.1.1.4 PBP: UpdateTiming

[16:06:59] Phase 2.1.1.5 PBP: Add part constraints

[16:06:59] Phase 2.2 Physical Synthesis After Floorplan

[16:07:30] Phase 2.3 Update Timing before SLR Path Opt

[16:07:30] Phase 2.4 Post-Processing in Floorplanning

[16:07:30] Phase 2.5 Global Placement Core

[16:11:31] Phase 2.5.1 Physical Synthesis In Placer

[16:13:01] Phase 3 Detail Placement

[16:13:01] Phase 3.1 Commit Multi Column Macros

[16:13:01] Phase 3.2 Commit Most Macros & LUTRAMs

[16:14:32] Phase 3.3 Small Shape DP

[16:14:32] Phase 3.3.1 Small Shape Clustering

[16:15:02] Phase 3.3.2 Flow Legalize Slice Clusters

[16:15:02] Phase 3.3.3 Slice Area Swap

[16:16:02] Phase 3.4 Place Remaining

[16:16:02] Phase 3.5 Re-assign LUT pins

[16:16:32] Phase 3.6 Pipeline Register Optimization

[16:16:32] Phase 3.7 Fast Optimization

[16:17:03] Phase 4 Post Placement Optimization and Clean-Up

[16:17:03] Phase 4.1 Post Commit Optimization

[16:17:33] Phase 4.1.1 Post Placement Optimization

[16:17:33] Phase 4.1.1.1 BUFG Insertion

[16:17:33] Phase 1 Physical Synthesis Initialization

[16:17:33] Phase 4.1.1.2 BUFG Replication

[16:17:33] Phase 4.1.1.3 Post Placement Timing Optimization

[16:18:33] Phase 4.1.1.4 Replication

[16:19:03] Phase 4.2 Post Placement Cleanup

[16:19:03] Phase 4.3 Placer Reporting

[16:19:03] Phase 4.3.1 Print Estimated Congestion

[16:19:03] Phase 4.4 Final Placement Cleanup

[16:24:05] Finished 4th of 6 tasks (FPGA logic placement). Elapsed time: 00h 26m 37s

[16:24:05] Starting logic routing..

[16:24:35] Phase 1 Build RT Design

[16:25:35] Phase 2 Router Initialization

[16:25:35] Phase 2.1 Fix Topology Constraints

[16:25:35] Phase 2.2 Pre Route Cleanup

[16:25:35] Phase 2.3 Global Clock Net Routing

[16:26:05] Phase 2.4 Update Timing

[16:26:35] Phase 2.5 Update Timing for Bus Skew

[16:26:35] Phase 2.5.1 Update Timing

[16:27:06] Phase 3 Initial Routing

[16:27:06] Phase 3.1 Global Routing

[16:28:06] Phase 4 Rip-up And Reroute

[16:28:06] Phase 4.1 Global Iteration 0

[16:31:37] Phase 4.2 Global Iteration 1

[16:32:07] Phase 4.3 Global Iteration 2

[16:33:07] Phase 4.4 Global Iteration 3

[16:33:37] Phase 4.5 Global Iteration 4

[16:33:37] Phase 5 Delay and Skew Optimization

[16:33:37] Phase 5.1 Delay CleanUp

[16:34:08] Phase 5.2 Clock Skew Optimization

[16:34:08] Phase 6 Post Hold Fix

[16:34:08] Phase 6.1 Hold Fix Iter

[16:34:08] Phase 6.1.1 Update Timing

[16:34:38] Phase 7 Leaf Clock Prog Delay Opt

[16:35:08] Phase 8 Route finalize

[16:35:08] Phase 9 Verifying routed nets

[16:35:08] Phase 10 Depositing Routes

[16:35:38] Phase 11 Post Router Timing

[16:35:38] Finished 5th of 6 tasks (FPGA routing). Elapsed time: 00h 11m 33s

[16:35:38] Starting bitstream generation..

Starting optional post-route physical design optimization.

Finished optional post-route physical design optimization.

[16:46:11] Creating bitmap...

[16:50:12] Writing bitstream ./level0_i_level1_level1_i_ulp_my_rm_partial.bit...

[16:50:12] Finished 6th of 6 tasks (FPGA bitstream generation). Elapsed time: 00h 14m 34s

[16:50:50] Run vpl: Step impl: Completed

[16:50:50] Run vpl: FINISHED. Run Status: impl Complete!

INFO: [v++ 60-1441] [16:50:51] Run run_link: Step vpl: Completed

Time (s): cpu = 00:00:17 ; elapsed = 01:03:05 . Memory (MB): peak = 1899.504 ; gain = 0.000 ; free physical = 24180 ; free virtual = 36112

INFO: [v++ 60-1443] [16:50:51] Run run_link: Step rtdgen: Started

INFO: [v++ 60-1453] Command Line: rtdgen

INFO: [v++ 60-1454] Run Directory: /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Design_Tutorials/05-bottom_up_rtl_kernel/krnl_aes/_x/link/run_link

INFO: [v++ 60-991] clock name 'ss_ucs/aclk_kernel_00' (clock ID '0') is being mapped to clock name 'DATA_CLK' in the xclbin

INFO: [v++ 60-991] clock name 'ss_ucs/aclk_kernel_01' (clock ID '1') is being mapped to clock name 'KERNEL_CLK' in the xclbin

INFO: [v++ 60-1230] The compiler selected the following frequencies for the runtime controllable kernel clock(s) and scalable system clock(s): Kernel (DATA) clock: ss_ucs/aclk_kernel_00 = 300, Kernel (KERNEL) clock: ss_ucs/aclk_kernel_01 = 500

INFO: [v++ 60-1453] Command Line: cf2sw -a /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Design_Tutorials/05-bottom_up_rtl_kernel/krnl_aes/_x/link/int/address_map.xml -sdsl /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Design_Tutorials/05-bottom_up_rtl_kernel/krnl_aes/_x/link/int/sdsl.dat -xclbin /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Design_Tutorials/05-bottom_up_rtl_kernel/krnl_aes/_x/link/int/xclbin_orig.xml -rtd /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Design_Tutorials/05-bottom_up_rtl_kernel/krnl_aes/_x/link/int/krnl_aes_test_hw.rtd -o /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Design_Tutorials/05-bottom_up_rtl_kernel/krnl_aes/_x/link/int/krnl_aes_test_hw.xml

INFO: [v++ 60-1652] Cf2sw returned exit code: 0

INFO: [v++ 60-1441] [16:50:55] Run run_link: Step rtdgen: Completed

Time (s): cpu = 00:00:04 ; elapsed = 00:00:04 . Memory (MB): peak = 1899.504 ; gain = 0.000 ; free physical = 25848 ; free virtual = 37781

INFO: [v++ 60-1443] [16:50:55] Run run_link: Step xclbinutil: Started

INFO: [v++ 60-1453] Command Line: xclbinutil --add-section BITSTREAM:RAW:/home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Design_Tutorials/05-bottom_up_rtl_kernel/krnl_aes/_x/link/int/partial.bit --force --target hw --key-value SYS:dfx_enable:true --add-section :JSON:/home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Design_Tutorials/05-bottom_up_rtl_kernel/krnl_aes/_x/link/int/krnl_aes_test_hw.rtd --append-section :JSON:/home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Design_Tutorials/05-bottom_up_rtl_kernel/krnl_aes/_x/link/int/appendSection.rtd --add-section CLOCK_FREQ_TOPOLOGY:JSON:/home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Design_Tutorials/05-bottom_up_rtl_kernel/krnl_aes/_x/link/int/krnl_aes_test_hw_xml.rtd --add-section BUILD_METADATA:JSON:/home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Design_Tutorials/05-bottom_up_rtl_kernel/krnl_aes/_x/link/int/krnl_aes_test_hw_build.rtd --add-section EMBEDDED_METADATA:RAW:/home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Design_Tutorials/05-bottom_up_rtl_kernel/krnl_aes/_x/link/int/krnl_aes_test_hw.xml --add-section SYSTEM_METADATA:RAW:/home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Design_Tutorials/05-bottom_up_rtl_kernel/krnl_aes/_x/link/int/systemDiagramModelSlrBaseAddress.json --key-value SYS:PlatformVBNV:xilinx_u250_gen3x16_xdma_3_1_202020_1 --output /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Design_Tutorials/05-bottom_up_rtl_kernel/krnl_aes/krnl_aes_test_hw.xclbin

INFO: [v++ 60-1454] Run Directory: /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Design_Tutorials/05-bottom_up_rtl_kernel/krnl_aes/_x/link/run_link

XRT Build Version: 2.11.634 (2021.1)

Build Date: 2021-06-08 22:08:45

Hash ID: 5ad5998d67080f00bca5bf15b3838cf35e0a7b26

Creating a default 'in-memory' xclbin image.

Section: 'BITSTREAM'(0) was successfully added.

Size : 46387874 bytes

Format : RAW

File : '/home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Design_Tutorials/05-bottom_up_rtl_kernel/krnl_aes/_x/link/int/partial.bit'

Section: 'MEM_TOPOLOGY'(6) was successfully added.

Format : JSON

File : 'mem_topology'

Section: 'IP_LAYOUT'(8) was successfully added.

Format : JSON

File : 'ip_layout'

Section: 'CONNECTIVITY'(7) was successfully added.

Format : JSON

File : 'connectivity'

Section: 'CLOCK_FREQ_TOPOLOGY'(11) was successfully added.

Size : 274 bytes

Format : JSON

File : '/home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Design_Tutorials/05-bottom_up_rtl_kernel/krnl_aes/_x/link/int/krnl_aes_test_hw_xml.rtd'

Section: 'BUILD_METADATA'(14) was successfully added.

Size : 8451 bytes

Format : JSON

File : '/home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Design_Tutorials/05-bottom_up_rtl_kernel/krnl_aes/_x/link/int/krnl_aes_test_hw_build.rtd'

Section: 'EMBEDDED_METADATA'(2) was successfully added.

Size : 13110 bytes

Format : RAW

File : '/home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Design_Tutorials/05-bottom_up_rtl_kernel/krnl_aes/_x/link/int/krnl_aes_test_hw.xml'

Section: 'SYSTEM_METADATA'(22) was successfully added.

Size : 30254 bytes

Format : RAW

File : '/home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Design_Tutorials/05-bottom_up_rtl_kernel/krnl_aes/_x/link/int/systemDiagramModelSlrBaseAddress.json'

Section: 'PARTITION_METADATA'(20) was successfully appended to.

Format : JSON

File : 'partition_metadata'

Section: 'IP_LAYOUT'(8) was successfully appended to.

Format : JSON

File : 'ip_layout'

Successfully wrote (46470448 bytes) to the output file: /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Design_Tutorials/05-bottom_up_rtl_kernel/krnl_aes/krnl_aes_test_hw.xclbin

Leaving xclbinutil.

INFO: [v++ 60-1441] [16:50:55] Run run_link: Step xclbinutil: Completed

Time (s): cpu = 00:00:00.06 ; elapsed = 00:00:00.10 . Memory (MB): peak = 1899.504 ; gain = 0.000 ; free physical = 25801 ; free virtual = 37780

INFO: [v++ 60-1443] [16:50:55] Run run_link: Step xclbinutilinfo: Started

INFO: [v++ 60-1453] Command Line: xclbinutil --quiet --force --info /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Design_Tutorials/05-bottom_up_rtl_kernel/krnl_aes/krnl_aes_test_hw.xclbin.info --input /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Design_Tutorials/05-bottom_up_rtl_kernel/krnl_aes/krnl_aes_test_hw.xclbin

INFO: [v++ 60-1454] Run Directory: /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Design_Tutorials/05-bottom_up_rtl_kernel/krnl_aes/_x/link/run_link

INFO: [v++ 60-1441] [16:50:55] Run run_link: Step xclbinutilinfo: Completed

Time (s): cpu = 00:00:00.26 ; elapsed = 00:00:00.29 . Memory (MB): peak = 1899.504 ; gain = 0.000 ; free physical = 25800 ; free virtual = 37779

INFO: [v++ 60-1443] [16:50:55] Run run_link: Step generate_sc_driver: Started

INFO: [v++ 60-1453] Command Line:

INFO: [v++ 60-1454] Run Directory: /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Design_Tutorials/05-bottom_up_rtl_kernel/krnl_aes/_x/link/run_link

INFO: [v++ 60-1441] [16:50:55] Run run_link: Step generate_sc_driver: Completed

Time (s): cpu = 00:00:00 ; elapsed = 00:00:00 . Memory (MB): peak = 1899.504 ; gain = 0.000 ; free physical = 25800 ; free virtual = 37779

INFO: [v++ 60-2331] SLR0 was specfied for compute unit krnl_aes_1, and verified as such in implementation.

INFO: [v++ 60-2331] SLR0 was specfied for compute unit strm_dump_1, and verified as such in implementation.

INFO: [v++ 60-2331] SLR0 was specfied for compute unit strm_dump_2, and verified as such in implementation.

INFO: [v++ 60-2331] SLR0 was specfied for compute unit strm_dump_3, and verified as such in implementation.

INFO: [v++ 60-2331] SLR0 was specfied for compute unit strm_dump_4, and verified as such in implementation.

INFO: [v++ 60-2331] SLR0 was specfied for compute unit strm_issue_1, and verified as such in implementation.

INFO: [v++ 60-2331] SLR0 was specfied for compute unit strm_issue_2, and verified as such in implementation.

INFO: [v++ 60-2331] SLR0 was specfied for compute unit strm_issue_3, and verified as such in implementation.

INFO: [v++ 60-2331] SLR0 was specfied for compute unit strm_issue_4, and verified as such in implementation.

INFO: [v++ 60-244] Generating system estimate report...

INFO: [v++ 60-1092] Generated system estimate report: /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Design_Tutorials/05-bottom_up_rtl_kernel/krnl_aes/_x/reports/link/system_estimate_krnl_aes_test_hw.xtxt

INFO: [v++ 60-586] Created /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Design_Tutorials/05-bottom_up_rtl_kernel/krnl_aes/krnl_aes_test_hw.ltx

INFO: [v++ 60-586] Created krnl_aes_test_hw.xclbin

INFO: [v++ 60-1307] Run completed. Additional information can be found in:

Guidance: /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Design_Tutorials/05-bottom_up_rtl_kernel/krnl_aes/_x/reports/link/v++_link_krnl_aes_test_hw_guidance.html

Timing Report: /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Design_Tutorials/05-bottom_up_rtl_kernel/krnl_aes/_x/reports/link/imp/impl_1_hw_bb_locked_timing_summary_routed.rpt

Vivado Log: /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Design_Tutorials/05-bottom_up_rtl_kernel/krnl_aes/_x/logs/link/vivado.log

Steps Log File: /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Design_Tutorials/05-bottom_up_rtl_kernel/krnl_aes/_x/logs/link/link.steps.log

INFO: [v++ 60-2343] Use the vitis_analyzer tool to visualize and navigate the relevant reports. Run the following command.

vitis_analyzer /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Design_Tutorials/05-bottom_up_rtl_kernel/krnl_aes/krnl_aes_test_hw.xclbin.link_summary

INFO: [v++ 60-791] Total elapsed time: 1h 3m 40s

INFO: [v++ 60-1653] Closing dispatch client.

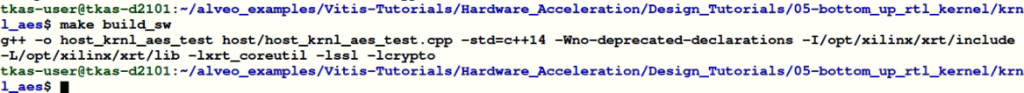

Compile Host Application

make build_sw

Build output message

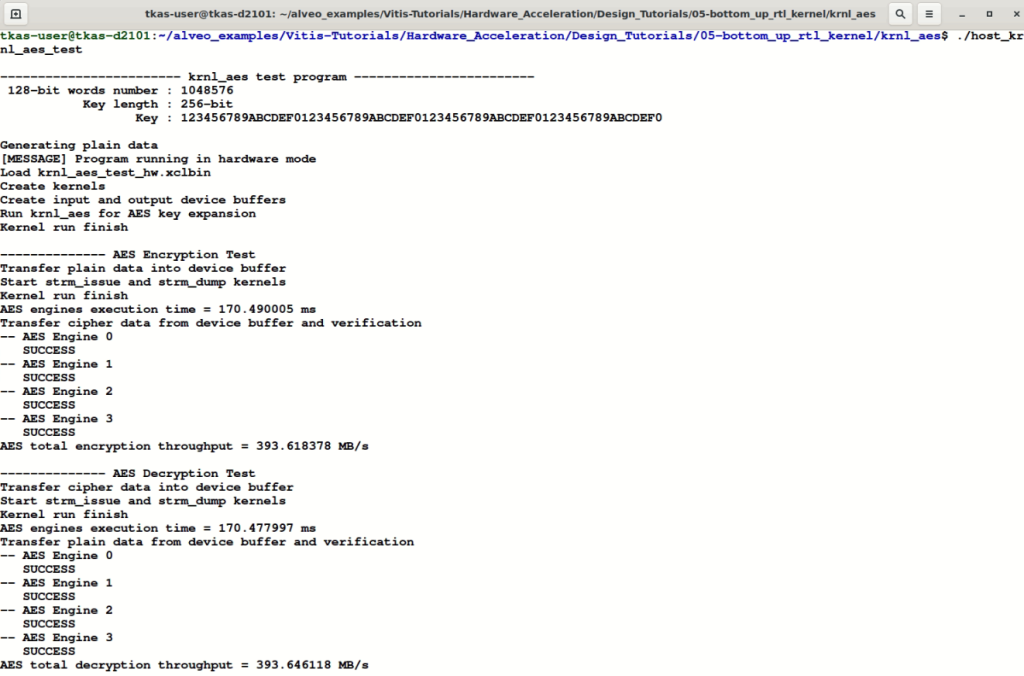

Run Host Application in Hardware Mode

If you have tried hardware emulation in the previous step, you must run the following command to disable the hw_emu mode:source setup_emu.sh -s off

Now, you can run the compiled host_krnl_aes_test file to test the system in hardware mode. The default words number to process is 1M 128-bit words, which is 16 MBytes. Because of the data transfer efficiency between host and FPGA via PCIe, you can peak processing throughput with big-enough input data.

./host_krnl_aes_test

Host application output message