#001 – Mix C++ and RTL kernel

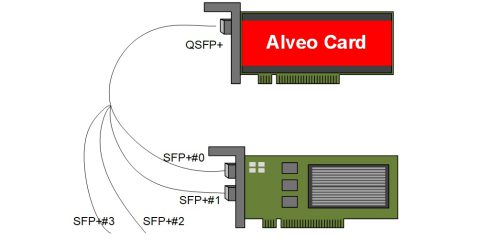

For Turnkey Accelerator System (TKAS-D2101) with Alveo U250 Card and Xilinx Vitis™ Unified Software Platform 2021.1

Based on Xilinx’s Vitis™ Application Acceleration Development Flow Tutorials: Mixing C++ and RTL Kernels

This tutorial is split into two parts:

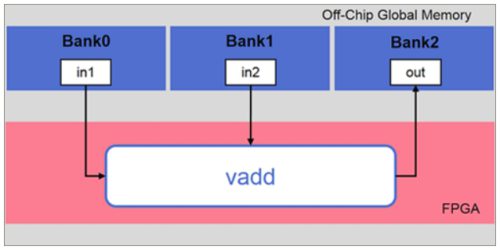

- In the first part, you will build an application (host and kernel) with one C++ based kernel. The host code, including the kernel function call, is reviewed.

- In the second part, an RTL-based kernel will be added to the application. The updated host code, including the function call to the additional kernel, is reviewed.

During both parts, the application is built using a Makefile. Software emulation is run in step one and hardware emulation is run in step two. In both steps, the generated Application Timeline will be reviewed to highlight the kernels being called and run by the host application. The host code and C++ kernel code are supplied. The RTL code will be generated using the RTL Kernel Wizard.

Step by Step to run on TKAS-D2101

Set enviroment

source /tools/Xilinx/Vitis/2021.1/settings64.sh

source /opt/xilinx/xrt/setup.sh

Create working folder

mkdir alveo_examplecd alveo_example

Clone from Github

git clone https://github.com/Xilinx/Vitis-Tutorials.gitcd Vitis-Tutorials

tkas-user@tkas-d2101:~/alveo_examples$ git clone https://github.com/Xilinx/Vitis-Tutorials.git

Cloning into 'Vitis-Tutorials'...

remote: Enumerating objects: 29932, done.

remote: Counting objects: 100% (2168/2168), done.

remote: Compressing objects: 100% (1228/1228), done.

remote: Total 29932 (delta 940), reused 1581 (delta 666), pack-reused 27764

Receiving objects: 100% (29932/29932), 415.13 MiB | 5.25 MiB/s, done.

Resolving deltas: 100% (15360/15360), done.

Updating files: 100% (4088/4088), done.

tkas-user@tkas-d2101:~/alveo_examples$ cd Vitis-TutorialsChange git branch to 2021.1 to match with Vitis version 2021.1 on Turnkey Accelerator Systems

tkas-user@tkas-d2101:~/alveo_examples/Vitis-Tutorials$ git status

On branch 2021.2

Your branch is up to date with 'origin/2021.2'.

nothing to commit, working tree clean

tkas-user@tkas-d2101:~/alveo_examples/Vitis-Tutorials$ git checkout 2021.1

Branch '2021.1' set up to track remote branch '2021.1' from 'origin'.

Switched to a new branch '2021.1'

tkas-user@tkas-d2101:~/alveo_examples/Vitis-Tutorials$ git log

commit c84a09e50fdbbf7d1752740bea39218b2b639788 (HEAD -> 2021.1, origin/2021.1)

Author: Ricky Su <imrickysu@users.noreply.github.com>

Date: Tue Mar 8 09:34:10 2022 +0800

PFM Kv260: update description for boot and sd_dir in step3 (#202)

- preparing boot dir is to fulfill the Vitis IDE workflow requirements

- User don't need to add files to sd_dir directory

commit 65bccd541b96a1a865e34c6ac049433b2764666d

Author: randyh62 <42045079+randyh62@users.noreply.github.com>

Date: Tue Jan 25 08:14:03 2022 -0800

HwAcc Intro: fix port name in connectivity ini to match wide_vadd.cpp (#177)

* edited u200.ini to match wide_vadd.cpp

* edited u250.ini to match wide_vadd.cpp

commit e902ab96065bbca73cf29933003d3fc9e73747da

Author: Ricky Su <imrickysu@users.noreply.github.com>

Date: Wed Jan 19 23:14:15 2022 +0800

PFM VCK190: Apply 2021.2 enhancements to 2021.1

Validation Makefile tests AIE test case

Add platforminfo Makefile

Step 3: explain more for boot components

Step 4: switch the order of hw-emu and hw build. Usually we do hw-emu before hw.

Step 4: fix sysroot path to cortexa72-cortexa53-xilinx-linux for PetaLinux 2021.1 update

tkas-user@tkas-d2101:~/alveo_examples/Vitis-Tutorials$1st: Build & Run C++ based kernel on run1 folder

cd Hardware_Acceleration/Feature_Tutorials/02-mixing-c-rtl-kernels/reference-files/run1

Change configuration for Alveo U250 Card

File #1 design.cfg :

Line 1 | platform=xilinx_u250_gen3x16_xdma_3_1_202020_1

File #2 Makefile :

Line 19 | DEVICE := xilinx_u250_gen3x16_xdma_3_1_202020_1

Line 25 | From “-lpthread” to “-pthread”

Build for software emulation

make all TARGET=sw_emu

This builds both the host software and hardware binary targeted to software emulation. The makefile will also generate the platform JSON emulation file to use during emulation.

Make result

tkas-user@tkas-d2101:~/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Feature_Tutorials/02-mixing-c-rtl-kernels/reference-files/run1$ make all TARGET=sw_emu

g++ -I/opt/xilinx/xrt/include/ -I/tools/Xilinx/Vivado/2021.1/include/ -Wall -O0 -g -std=c++11 -L/opt/xilinx/xrt/lib/ -lOpenCL -lpthread -lrt -lstdc++ -o 'host' '../src/host/host_step1.cpp' -lOpenCL

v++ -t sw_emu --config design.cfg -c -k krnl_vadd -I'../src/kernel_cpp' -o'krnl_vadd.sw_emu.xilinx_u250_gen3x16_xdma_3_1_202020_1.xo' '../src/kernel_cpp/krnl_vadd.cpp'

Option Map File Used: '/tools/Xilinx/Vitis/2021.1/data/vitis/vpp/optMap.xml'

****** v++ v2021.1 (64-bit)

**** SW Build 3246112 on 2021-06-09-14:19:56

** Copyright 1986-2020 Xilinx, Inc. All Rights Reserved.

INFO: [v++ 60-1306] Additional information associated with this v++ compile can be found at:

Reports: /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Feature_Tutorials/02-mixing-c-rtl-kernels/reference-files/run1/_x/reports/krnl_vadd.sw_emu.xilinx_u250_gen3x16_xdma_3_1_202020_1

Log files: /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Feature_Tutorials/02-mixing-c-rtl-kernels/reference-files/run1/_x/logs/krnl_vadd.sw_emu.xilinx_u250_gen3x16_xdma_3_1_202020_1

Running Dispatch Server on port: 42635

INFO: [v++ 60-1548] Creating build summary session with primary output /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Feature_Tutorials/02-mixing-c-rtl-kernels/reference-files/run1/krnl_vadd.sw_emu.xilinx_u250_gen3x16_xdma_3_1_202020_1.xo.compile_summary, at Sat Mar 19 15:21:53 2022

INFO: [v++ 60-1316] Initiating connection to rulecheck server, at Sat Mar 19 15:21:53 2022

Running Rule Check Server on port:42461

INFO: [v++ 60-1315] Creating rulecheck session with output '/home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Feature_Tutorials/02-mixing-c-rtl-kernels/reference-files/run1/_x/reports/krnl_vadd.sw_emu.xilinx_u250_gen3x16_xdma_3_1_202020_1/v++_compile_krnl_vadd.sw_emu.xilinx_u250_gen3x16_xdma_3_1_202020_1_guidance.html', at Sat Mar 19 15:21:54 2022

INFO: [v++ 60-895] Target platform: /opt/xilinx/platforms/xilinx_u250_gen3x16_xdma_3_1_202020_1/xilinx_u250_gen3x16_xdma_3_1_202020_1.xpfm

INFO: [v++ 60-1578] This platform contains Xilinx Shell Archive '/opt/xilinx/platforms/xilinx_u250_gen3x16_xdma_3_1_202020_1/hw/hw.xsa'

INFO: [v++ 74-78] Compiler Version string: 2021.1

INFO: [v++ 60-585] Compiling for software emulation target

INFO: [v++ 60-423] Target device: xilinx_u250_gen3x16_xdma_3_1_202020_1

INFO: [v++ 60-242] Creating kernel: 'krnl_vadd'

INFO: [v++ 60-594] Finished kernel compilation

INFO: [v++ 60-586] Created krnl_vadd.sw_emu.xilinx_u250_gen3x16_xdma_3_1_202020_1.xo

INFO: [v++ 60-2343] Use the vitis_analyzer tool to visualize and navigate the relevant reports. Run the following command.

vitis_analyzer /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Feature_Tutorials/02-mixing-c-rtl-kernels/reference-files/run1/krnl_vadd.sw_emu.xilinx_u250_gen3x16_xdma_3_1_202020_1.xo.compile_summary

INFO: [v++ 60-791] Total elapsed time: 0h 0m 17s

INFO: [v++ 60-1653] Closing dispatch client.

v++ -t sw_emu --config design.cfg -l -o'krnl_vadd.sw_emu.xilinx_u250_gen3x16_xdma_3_1_202020_1.xclbin' krnl_vadd.sw_emu.xilinx_u250_gen3x16_xdma_3_1_202020_1.xo

Option Map File Used: '/tools/Xilinx/Vitis/2021.1/data/vitis/vpp/optMap.xml'

****** v++ v2021.1 (64-bit)

**** SW Build 3246112 on 2021-06-09-14:19:56

** Copyright 1986-2020 Xilinx, Inc. All Rights Reserved.

INFO: [v++ 60-1306] Additional information associated with this v++ link can be found at:

Reports: /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Feature_Tutorials/02-mixing-c-rtl-kernels/reference-files/run1/_x/reports/link

Log files: /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Feature_Tutorials/02-mixing-c-rtl-kernels/reference-files/run1/_x/logs/link

Running Dispatch Server on port: 40165

INFO: [v++ 60-1548] Creating build summary session with primary output /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Feature_Tutorials/02-mixing-c-rtl-kernels/reference-files/run1/krnl_vadd.sw_emu.xilinx_u250_gen3x16_xdma_3_1_202020_1.xclbin.link_summary, at Sat Mar 19 15:22:12 2022

INFO: [v++ 60-1316] Initiating connection to rulecheck server, at Sat Mar 19 15:22:12 2022

Running Rule Check Server on port:41281

INFO: [v++ 60-1315] Creating rulecheck session with output '/home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Feature_Tutorials/02-mixing-c-rtl-kernels/reference-files/run1/_x/reports/link/v++_link_krnl_vadd.sw_emu.xilinx_u250_gen3x16_xdma_3_1_202020_1_guidance.html', at Sat Mar 19 15:22:13 2022

INFO: [v++ 60-895] Target platform: /opt/xilinx/platforms/xilinx_u250_gen3x16_xdma_3_1_202020_1/xilinx_u250_gen3x16_xdma_3_1_202020_1.xpfm

INFO: [v++ 60-1578] This platform contains Xilinx Shell Archive '/opt/xilinx/platforms/xilinx_u250_gen3x16_xdma_3_1_202020_1/hw/hw.xsa'

INFO: [v++ 74-78] Compiler Version string: 2021.1

INFO: [v++ 60-629] Linking for software emulation target

INFO: [v++ 60-423] Target device: xilinx_u250_gen3x16_xdma_3_1_202020_1

INFO: [v++ 60-645] kernel flags are '-g -I /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Feature_Tutorials/02-mixing-c-rtl-kernels/reference-files/src/kernel_cpp -g'

WARNING: [v++ 60-2336] Parameter compiler.enableSlrComputeUnitDrc was set to true, but no SLRs were specified via the command line.

INFO: [v++ 60-586] Created krnl_vadd.sw_emu.xilinx_u250_gen3x16_xdma_3_1_202020_1.xclbin

INFO: [v++ 60-1307] Run completed. Additional information can be found in:

Guidance: /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Feature_Tutorials/02-mixing-c-rtl-kernels/reference-files/run1/_x/reports/link/v++_link_krnl_vadd.sw_emu.xilinx_u250_gen3x16_xdma_3_1_202020_1_guidance.html

Steps Log File: /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Feature_Tutorials/02-mixing-c-rtl-kernels/reference-files/run1/_x/logs/link/link.steps.log

INFO: [v++ 60-2343] Use the vitis_analyzer tool to visualize and navigate the relevant reports. Run the following command.

vitis_analyzer /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Feature_Tutorials/02-mixing-c-rtl-kernels/reference-files/run1/krnl_vadd.sw_emu.xilinx_u250_gen3x16_xdma_3_1_202020_1.xclbin.link_summary

INFO: [v++ 60-791] Total elapsed time: 0h 0m 15s

INFO: [v++ 60-1653] Closing dispatch client.

emconfigutil --platform xilinx_u250_gen3x16_xdma_3_1_202020_1

****** configutil v2021.1 (64-bit)

**** SW Build 3246112 on 2021-06-09-14:19:56

** Copyright 1986-2020 Xilinx, Inc. All Rights Reserved.

INFO: [ConfigUtil 60-895] Target platform: /opt/xilinx/platforms/xilinx_u250_gen3x16_xdma_3_1_202020_1/xilinx_u250_gen3x16_xdma_3_1_202020_1.xpfm

INFO: [ConfigUtil 60-1578] This platform contains Xilinx Shell Archive '/opt/xilinx/platforms/xilinx_u250_gen3x16_xdma_3_1_202020_1/hw/hw.xsa'

INFO: [ConfigUtil 60-1032]

emulation configuration file `emconfig.json` is created in current working directory

tkas-user@tkas-d2101:~/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Feature_Tutorials/02-mixing-c-rtl-kernels/reference-files/run1$Run software emulation

set emulation enviroment

export XCL_EMULATION_MODE=sw_emu

Run by the following command

./host krnl_vadd.sw_emu.xilinx_u250_gen3x16_xdma_3_1_202020_1.xclbin

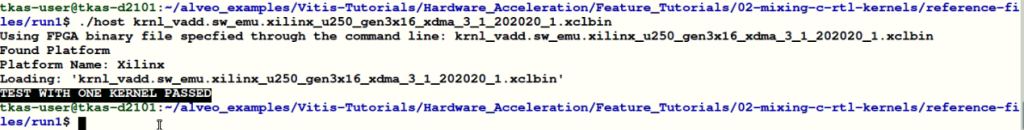

Run result

tkas-user@tkas-d2101:~/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Feature_Tutorials/02-mixing-c-rtl-kernels/reference-files/run1$ ./host krnl_vadd.sw_emu.xilinx_u250_gen3x16_xdma_3_1_202020_1.xclbin

Using FPGA binary file specfied through the command line: krnl_vadd.sw_emu.xilinx_u250_gen3x16_xdma_3_1_202020_1.xclbin

Found Platform

Platform Name: Xilinx

Loading: 'krnl_vadd.sw_emu.xilinx_u250_gen3x16_xdma_3_1_202020_1.xclbin'

TEST WITH ONE KERNEL PASSED

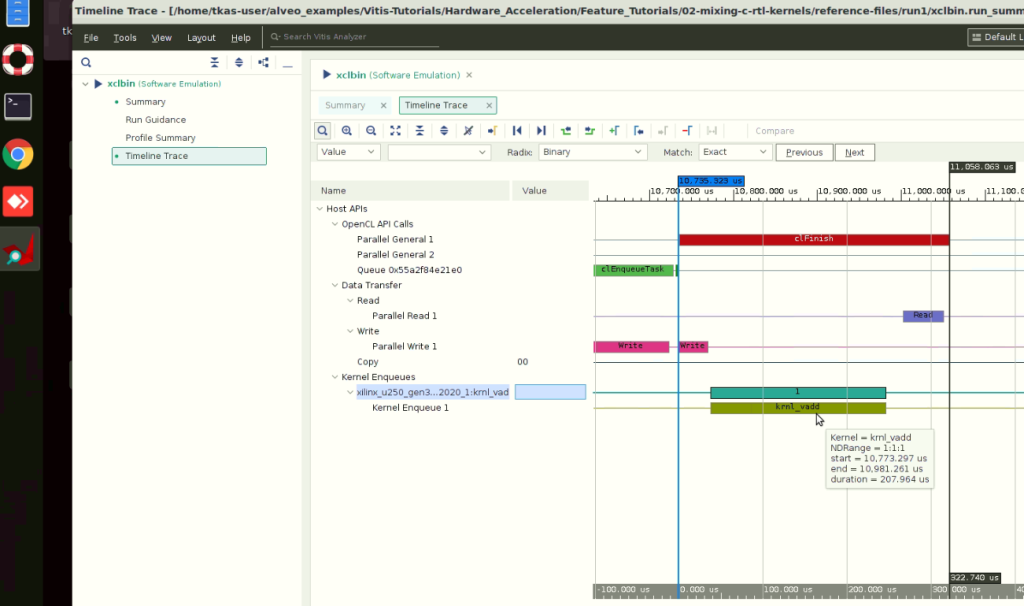

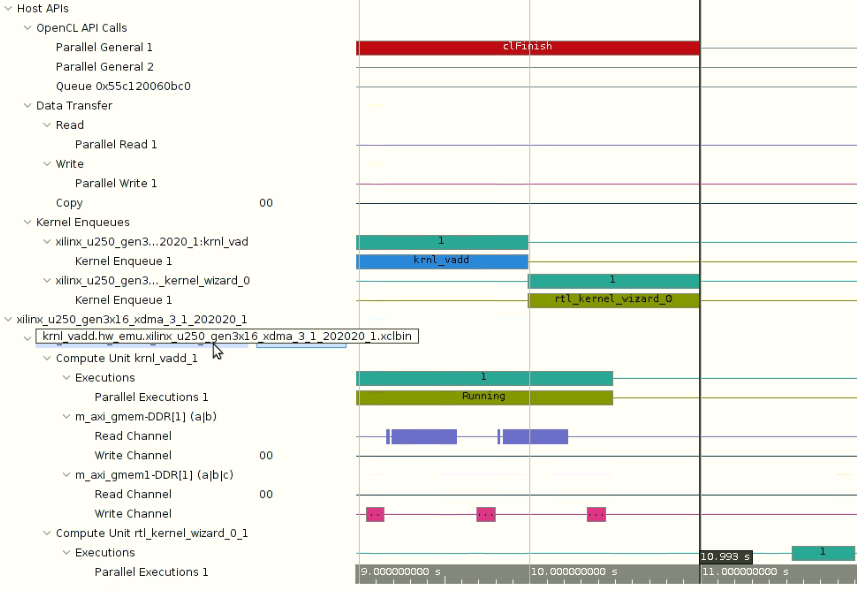

Review the Application Timeline

Review the Application Timeline generated during software emulation to visualize the host events and the kernel running.vitis_analyzer xclbin.run_summaryClick on the Application Timeline option on the left to bring up the Application Timeline.

2nd: Building an Application with C++ and RTL-Based Kernels

Create and package an RTL-based kernel using the RTL Kernel Wizard

Create the Vitis Project

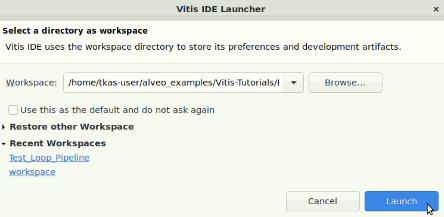

Run vitis

vitis

Select ./mixing-c-rtl-kernels/workspace as the workspace directory, and click Launch.

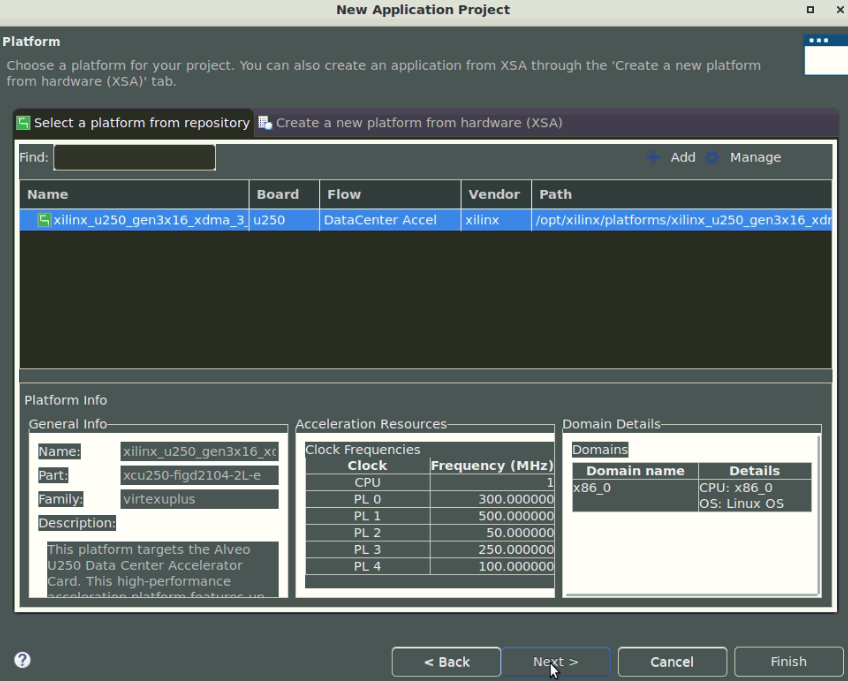

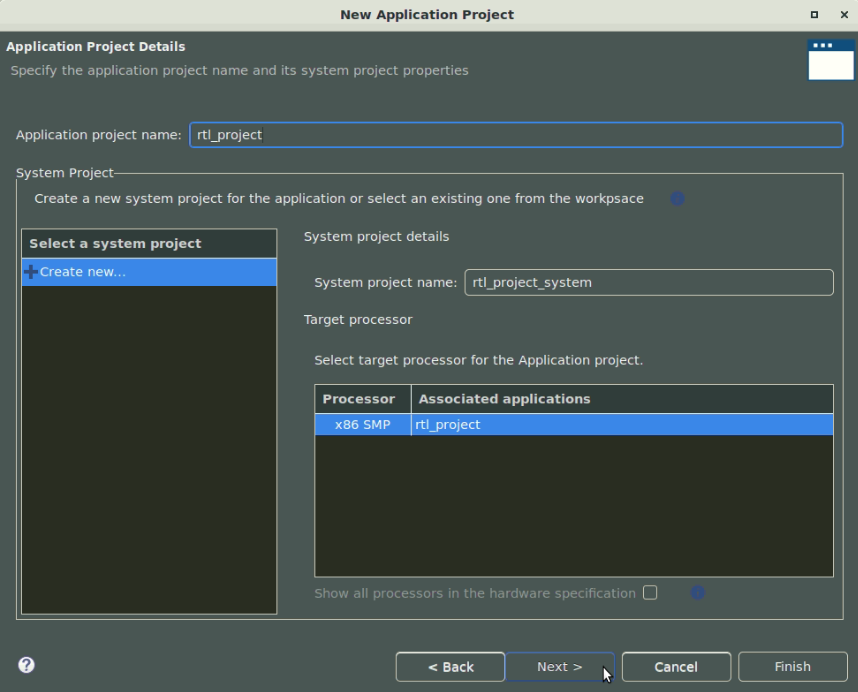

From the Welcome screen select Create Application Project to open the New Project wizard.

The first page displays a summary of the process. Click Next to proceed.

From the Platform page select the xilinx_u250_gen3x16_xdma_3_1_202020_1 platform and click Next.

From the Application Project Details page, name your project rtl_project and click Next.

Under SW Acceleration Templates, select Empty Application, and click Finish.

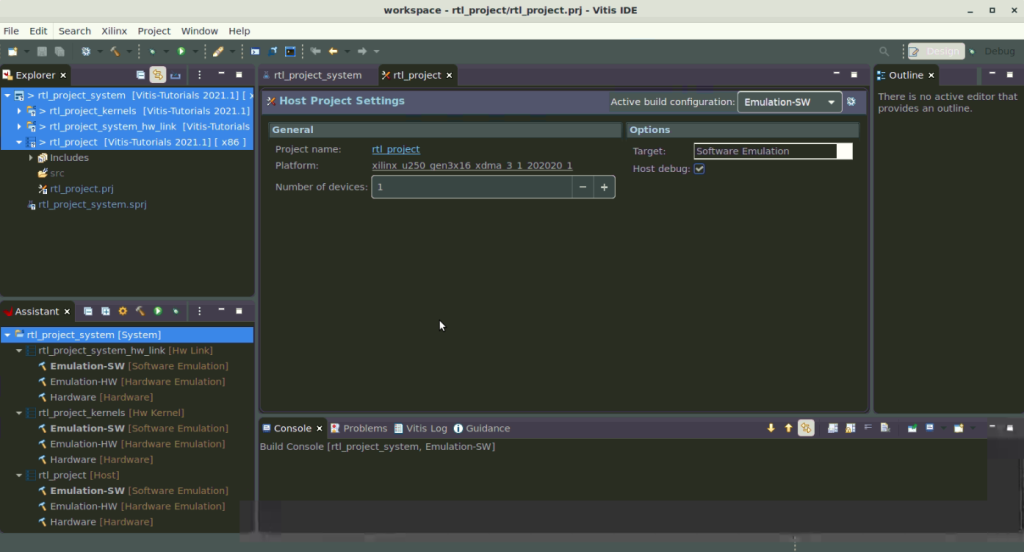

This creates a Vitis IDE project.

Next, generate an RTL-based kernel from within the Vitis IDE.

Select the menu command Xilinx > Launch RTL Kernel Wizard > rtl_project_kernels.

This opens the RTL Kernel Wizard Welcome page.The first page is a summary of the process.

Review it and click Next. In the General Settings dialog box, keep all the default settings, and click Next.

In the Scalars dialog box, set the number of scalar arguments to 0, and click Next.

In the Global Memory dialog box, keep all the default settings, and click Next.

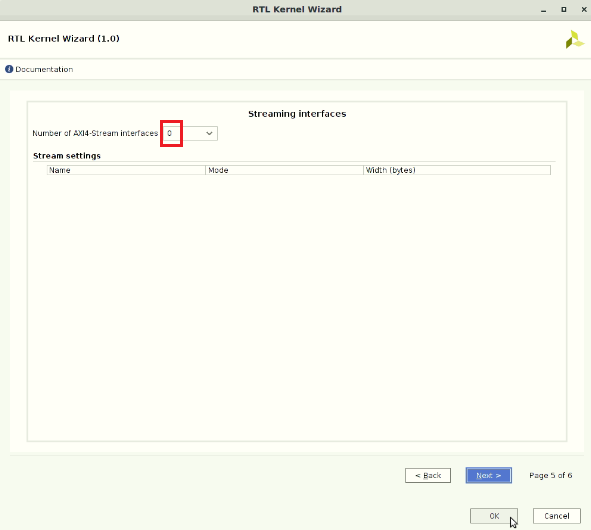

In the Streaming Interfaces dialog box, keep all the default settings, and click Next.

Note: This tutorial doesn’t have AXI steam interface

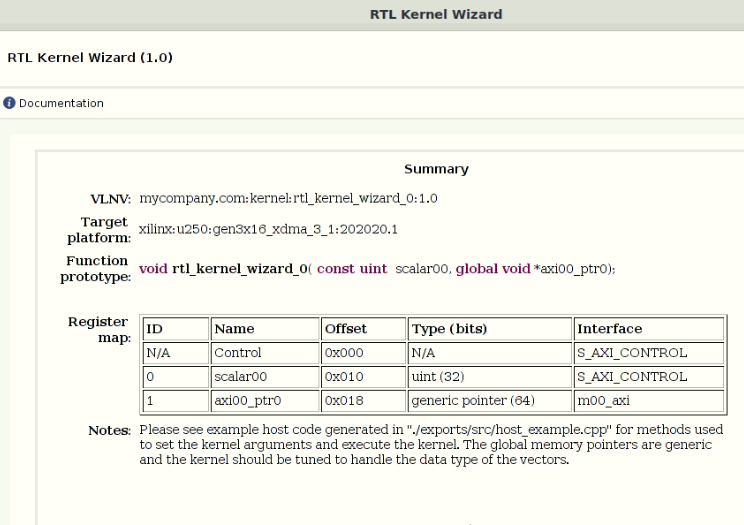

The Summary dialog box is displayed and provides a summary of the RTL kernel settings and includes a function prototype which conveys what a kernel call would look like as a C function.

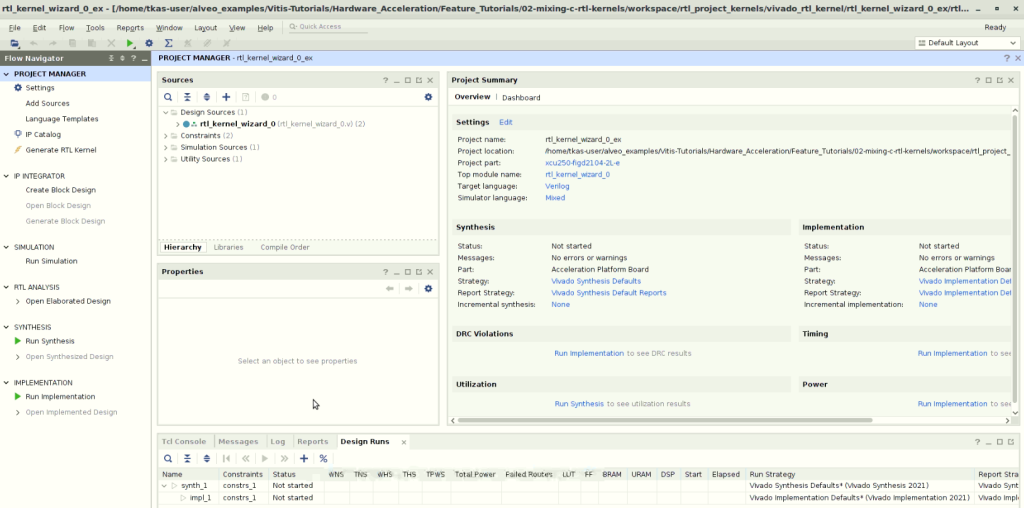

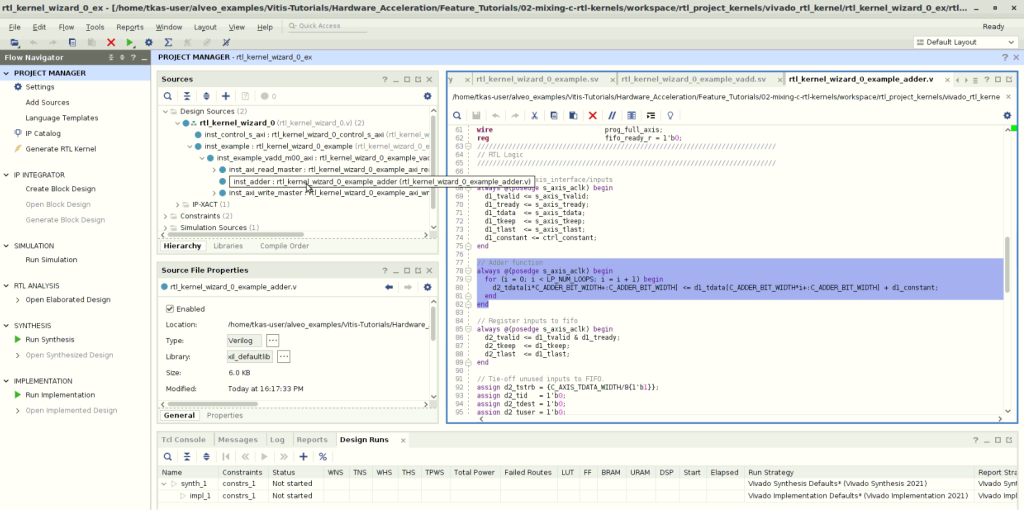

Click OK. The RTL Kernel source files have now been created and Vivado opens a project automatically with the generated RTL code corresponding to the default A = A + 1 function.

You can navigate to review the source files or even run RTL simulation. However, for this tutorial, you will not be modifying the default RTL Kernel and will only package into an object file (.xo).

Generate RTL Kernel

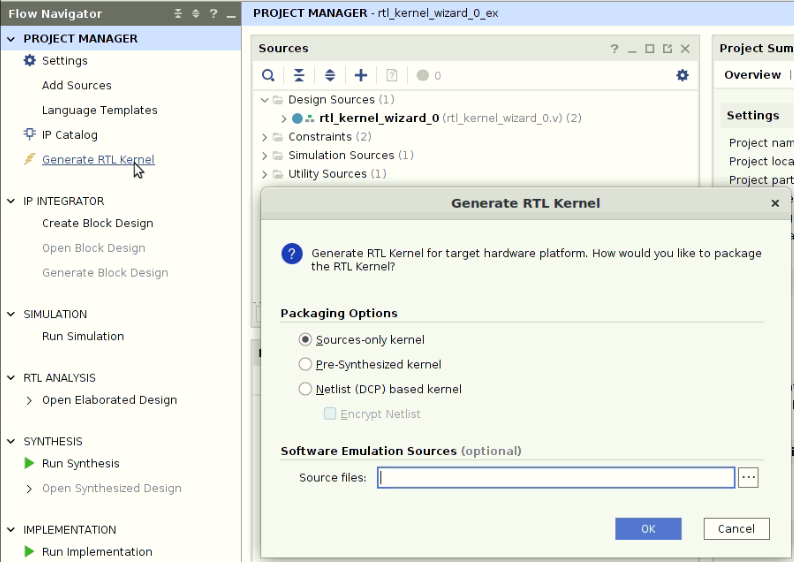

In Flow Navigator, click Generate RTL Kernel.

In the Generate RTL Kernel dialog box, select the Sources-only packaging option.

For Software Emulation Sources, you can add a C++ model of the RTL kernel,

which is used for Software Emulation.

The C++ model must be coded by the design engineer. Typically, there is no C++ model available, and Hardware Emulation is used to test the design. Because the RTL Wizard creates a C++ model of the vadd design, the steps to add this file are also provided below.

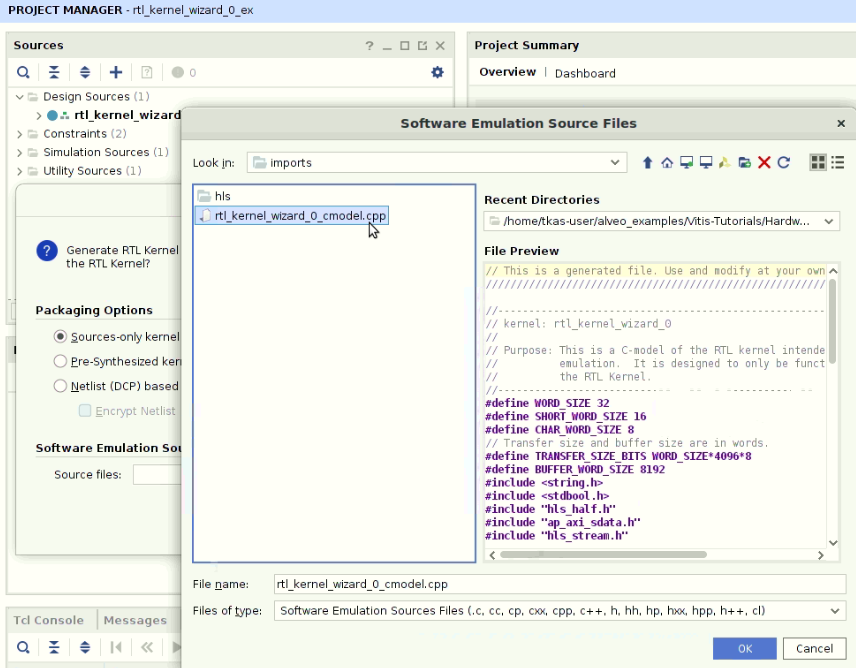

Click the Browse command (…). Double-click the imports directory.

Select the rtl_kernel_wizard_0_cmodel.cpp file and click OK.To generate the RTL kernel.

After the RTL kernel has been generated successfully, click Yes

to exit the Vivado Design Suite, and return to the Vitis IDE.

A message window displays some information related to the generated RTL kernel.

Review it and click OK.

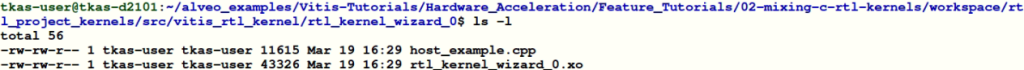

Exit the Vitis IDE.At this point, you have packaged the RTL kernel into the following object file, rtl_kernel_wizard_0.xo found in the following directory

../02-mixing-c-rtl-kernels/workspace/rtl_project_kernels/src/vitis_rtl_kernel/rtl_kernel_wizard_0

Description of Host application source code

Build and Emulation with C++ and RTL Based Kernels

With the RTL-based kernel added and host code updated, build the application, targeting hardware emulation through the updated makefile in the run2 directory. The makefile has been updated to add both the CPP and RTL-based kernels to the hardware platform file (xclbin).

Navigate to the ./02-mixing-c-rtl-kernels/reference-files/run2 directory.

Change plaform in the following files to match with your Alveo Card (xilinx_u250_gen3x16_xdma_3_1_202020_1)

- compile.cfg

- link.cfg

- and Makefile for Alveo U250 Card

Here are summary changed in Makefile

Line 18 | DEVICE := xilinx_u250_gen3x16_xdma_3_1_202020_1

Line 24 | CXXFLAGS := -I$(XILINX_XRT)/include/ -I$(XILINX_VIVADO)/include/ -Wall -O0 -g -std=c++11 -L$(XILINX_XRT)/lib/ -lOpenCL -pthread -lrt -lstdc++

Line 30-32 |

LDCLFLAGS += –profile.data=all:all:all

LDCLFLAGS += –profile.stall=all:all:all

LDCLFLAGS += –profile.exec=all:all:all

To build the application targeting hardware emulation, run the following makefile from the

./reference-files/run2 directory.

Build result

tkas-user@tkas-d2101:~/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Feature_Tutorials/02-mixing-c-rtl-kernels/reference-files/run2$ make all TARGET=hw_emu

g++ -I/opt/xilinx/xrt/include/ -I/tools/Xilinx/Vivado/2021.1/include/ -Wall -O0 -g -std=c++11 -L/opt/xilinx/xrt/lib/ -lOpenCL -pthread -lrt -lstdc++ -o 'host' '../src/host/host_step2.cpp' -lOpenCL

v++ -t hw_emu --config link.cfg --profile.data=all:all:all --profile.stall=all:all:all --profile.exec=all:all:all -l -o'krnl_vadd.hw_emu.xilinx_u250_gen3x16_xdma_3_1_202020_1.xclbin' krnl_vadd.hw_emu.xilinx_u250_gen3x16_xdma_3_1_202020_1.xo ../../script/workplace/rtl_project/src/rtl_kernel/rtl_kernel_wizard_0/rtl_kernel_wizard_0.xo

Option Map File Used: '/tools/Xilinx/Vitis/2021.1/data/vitis/vpp/optMap.xml'

****** v++ v2021.1 (64-bit)

**** SW Build 3246112 on 2021-06-09-14:19:56

** Copyright 1986-2020 Xilinx, Inc. All Rights Reserved.

INFO: [v++ 60-1306] Additional information associated with this v++ link can be found at:

Reports: /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Feature_Tutorials/02-mixing-c-rtl-kernels/reference-files/run2/_x/reports/link

Log files: /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Feature_Tutorials/02-mixing-c-rtl-kernels/reference-files/run2/_x/logs/link

Running Dispatch Server on port: 36021

INFO: [v++ 60-1548] Creating build summary session with primary output /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Feature_Tutorials/02-mixing-c-rtl-kernels/reference-files/run2/krnl_vadd.hw_emu.xilinx_u250_gen3x16_xdma_3_1_202020_1.xclbin.link_summary, at Sat Mar 19 16:53:17 2022

INFO: [v++ 60-1316] Initiating connection to rulecheck server, at Sat Mar 19 16:53:17 2022

Running Rule Check Server on port:42111

INFO: [v++ 60-1315] Creating rulecheck session with output '/home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Feature_Tutorials/02-mixing-c-rtl-kernels/reference-files/run2/_x/reports/link/v++_link_krnl_vadd.hw_emu.xilinx_u250_gen3x16_xdma_3_1_202020_1_guidance.html', at Sat Mar 19 16:53:18 2022

INFO: [v++ 60-895] Target platform: /opt/xilinx/platforms/xilinx_u250_gen3x16_xdma_3_1_202020_1/xilinx_u250_gen3x16_xdma_3_1_202020_1.xpfm

INFO: [v++ 60-1578] This platform contains Xilinx Shell Archive '/opt/xilinx/platforms/xilinx_u250_gen3x16_xdma_3_1_202020_1/hw/hw.xsa'

INFO: [v++ 74-78] Compiler Version string: 2021.1

INFO: [v++ 60-629] Linking for hardware emulation target

INFO: [v++ 60-423] Target device: xilinx_u250_gen3x16_xdma_3_1_202020_1

INFO: [v++ 60-1332] Run 'run_link' status: Not started

INFO: [v++ 60-1443] [16:53:20] Run run_link: Step system_link: Started

INFO: [v++ 60-1453] Command Line: system_link --xo /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Feature_Tutorials/02-mixing-c-rtl-kernels/reference-files/run2/krnl_vadd.hw_emu.xilinx_u250_gen3x16_xdma_3_1_202020_1.xo --xo /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Feature_Tutorials/02-mixing-c-rtl-kernels/script/workplace/rtl_project/src/rtl_kernel/rtl_kernel_wizard_0/rtl_kernel_wizard_0.xo --config /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Feature_Tutorials/02-mixing-c-rtl-kernels/reference-files/run2/_x/link/int/syslinkConfig.ini --xpfm /opt/xilinx/platforms/xilinx_u250_gen3x16_xdma_3_1_202020_1/xilinx_u250_gen3x16_xdma_3_1_202020_1.xpfm --target emu --output_dir /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Feature_Tutorials/02-mixing-c-rtl-kernels/reference-files/run2/_x/link/int --temp_dir /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Feature_Tutorials/02-mixing-c-rtl-kernels/reference-files/run2/_x/link/sys_link

INFO: [v++ 60-1454] Run Directory: /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Feature_Tutorials/02-mixing-c-rtl-kernels/reference-files/run2/_x/link/run_link

INFO: [SYSTEM_LINK 60-1316] Initiating connection to rulecheck server, at Sat Mar 19 16:53:21 2022

INFO: [SYSTEM_LINK 82-70] Extracting xo v3 file /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Feature_Tutorials/02-mixing-c-rtl-kernels/reference-files/run2/krnl_vadd.hw_emu.xilinx_u250_gen3x16_xdma_3_1_202020_1.xo

INFO: [SYSTEM_LINK 82-70] Extracting xo v3 file /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Feature_Tutorials/02-mixing-c-rtl-kernels/script/workplace/rtl_project/src/rtl_kernel/rtl_kernel_wizard_0/rtl_kernel_wizard_0.xo

INFO: [SYSTEM_LINK 82-53] Creating IP database /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Feature_Tutorials/02-mixing-c-rtl-kernels/reference-files/run2/_x/link/sys_link/_sysl/.cdb/xd_ip_db.xml

INFO: [SYSTEM_LINK 82-38] [16:53:21] build_xd_ip_db started: /tools/Xilinx/Vitis/2021.1/bin/build_xd_ip_db -ip_search 0 -sds-pf /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Feature_Tutorials/02-mixing-c-rtl-kernels/reference-files/run2/_x/link/sys_link/hw_emu/pfm_dynamic_emu.hpfm -clkid 0 -ip /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Feature_Tutorials/02-mixing-c-rtl-kernels/reference-files/run2/_x/link/sys_link/iprepo/xilinx_com_hls_krnl_vadd_1_0,krnl_vadd -ip /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Feature_Tutorials/02-mixing-c-rtl-kernels/reference-files/run2/_x/link/sys_link/iprepo/mycompany_com_kernel_rtl_kernel_wizard_0_1_0,rtl_kernel_wizard_0 -o /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Feature_Tutorials/02-mixing-c-rtl-kernels/reference-files/run2/_x/link/sys_link/_sysl/.cdb/xd_ip_db.xml

INFO: [SYSTEM_LINK 82-37] [16:53:24] build_xd_ip_db finished successfully

Time (s): cpu = 00:00:04 ; elapsed = 00:00:03 . Memory (MB): peak = 2005.691 ; gain = 0.000 ; free physical = 16956 ; free virtual = 35412

INFO: [SYSTEM_LINK 82-51] Create system connectivity graph

INFO: [SYSTEM_LINK 82-102] Applying explicit connections to the system connectivity graph: /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Feature_Tutorials/02-mixing-c-rtl-kernels/reference-files/run2/_x/link/sys_link/cfgraph/cfgen_cfgraph.xml

INFO: [SYSTEM_LINK 82-38] [16:53:24] cfgen started: /tools/Xilinx/Vitis/2021.1/bin/cfgen -nk krnl_vadd:1:krnl_vadd_1 -nk rtl_kernel_wizard_0:1:rtl_kernel_wizard_0_1 -dmclkid 0 -r /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Feature_Tutorials/02-mixing-c-rtl-kernels/reference-files/run2/_x/link/sys_link/_sysl/.cdb/xd_ip_db.xml -o /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Feature_Tutorials/02-mixing-c-rtl-kernels/reference-files/run2/_x/link/sys_link/cfgraph/cfgen_cfgraph.xml

INFO: [CFGEN 83-0] Kernel Specs:

INFO: [CFGEN 83-0] kernel: krnl_vadd, num: 1 {krnl_vadd_1}

INFO: [CFGEN 83-0] kernel: rtl_kernel_wizard_0, num: 1 {rtl_kernel_wizard_0_1}

INFO: [CFGEN 83-2226] Inferring mapping for argument krnl_vadd_1.a to DDR[1]

INFO: [CFGEN 83-2226] Inferring mapping for argument krnl_vadd_1.b to DDR[1]

INFO: [CFGEN 83-2226] Inferring mapping for argument krnl_vadd_1.c to DDR[1]

INFO: [CFGEN 83-2226] Inferring mapping for argument rtl_kernel_wizard_0_1.axi00_ptr0 to DDR[1]

INFO: [SYSTEM_LINK 82-37] [16:53:28] cfgen finished successfully

Time (s): cpu = 00:00:04 ; elapsed = 00:00:04 . Memory (MB): peak = 2005.691 ; gain = 0.000 ; free physical = 16954 ; free virtual = 35410

INFO: [SYSTEM_LINK 82-52] Create top-level block diagram

INFO: [SYSTEM_LINK 82-38] [16:53:28] cf2bd started: /tools/Xilinx/Vitis/2021.1/bin/cf2bd --linux --trace_buffer 1024 --input_file /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Feature_Tutorials/02-mixing-c-rtl-kernels/reference-files/run2/_x/link/sys_link/cfgraph/cfgen_cfgraph.xml --ip_db /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Feature_Tutorials/02-mixing-c-rtl-kernels/reference-files/run2/_x/link/sys_link/_sysl/.cdb/xd_ip_db.xml --cf_name dr --working_dir /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Feature_Tutorials/02-mixing-c-rtl-kernels/reference-files/run2/_x/link/sys_link/_sysl/.xsd --temp_dir /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Feature_Tutorials/02-mixing-c-rtl-kernels/reference-files/run2/_x/link/sys_link --output_dir /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Feature_Tutorials/02-mixing-c-rtl-kernels/reference-files/run2/_x/link/int --target_bd hw_emu/pfm_dynamic/pfm_dynamic.bd

INFO: [CF2BD 82-31] Launching cf2xd: cf2xd -linux -trace-buffer 1024 -i /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Feature_Tutorials/02-mixing-c-rtl-kernels/reference-files/run2/_x/link/sys_link/cfgraph/cfgen_cfgraph.xml -r /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Feature_Tutorials/02-mixing-c-rtl-kernels/reference-files/run2/_x/link/sys_link/_sysl/.cdb/xd_ip_db.xml -o dr.xml

INFO: [CF2BD 82-28] cf2xd finished successfully

INFO: [CF2BD 82-31] Launching cf_xsd: cf_xsd -disable-address-gen -bd hw_emu/pfm_dynamic/pfm_dynamic.bd -dn dr -dp /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Feature_Tutorials/02-mixing-c-rtl-kernels/reference-files/run2/_x/link/sys_link/_sysl/.xsd

INFO: [CF2BD 82-28] cf_xsd finished successfully

INFO: [SYSTEM_LINK 82-37] [16:53:31] cf2bd finished successfully

Time (s): cpu = 00:00:02 ; elapsed = 00:00:02 . Memory (MB): peak = 2005.691 ; gain = 0.000 ; free physical = 16947 ; free virtual = 35410

INFO: [v++ 60-1441] [16:53:31] Run run_link: Step system_link: Completed

Time (s): cpu = 00:00:12 ; elapsed = 00:00:11 . Memory (MB): peak = 1899.484 ; gain = 0.000 ; free physical = 16991 ; free virtual = 35449

INFO: [v++ 60-1443] [16:53:31] Run run_link: Step cf2sw: Started

INFO: [v++ 60-1453] Command Line: cf2sw -sdsl /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Feature_Tutorials/02-mixing-c-rtl-kernels/reference-files/run2/_x/link/int/sdsl.dat -rtd /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Feature_Tutorials/02-mixing-c-rtl-kernels/reference-files/run2/_x/link/int/cf2sw.rtd -nofilter /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Feature_Tutorials/02-mixing-c-rtl-kernels/reference-files/run2/_x/link/int/cf2sw_full.rtd -xclbin /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Feature_Tutorials/02-mixing-c-rtl-kernels/reference-files/run2/_x/link/int/xclbin_orig.xml -o /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Feature_Tutorials/02-mixing-c-rtl-kernels/reference-files/run2/_x/link/int/xclbin_orig.1.xml

INFO: [v++ 60-1454] Run Directory: /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Feature_Tutorials/02-mixing-c-rtl-kernels/reference-files/run2/_x/link/run_link

INFO: [v++ 60-1441] [16:53:34] Run run_link: Step cf2sw: Completed

Time (s): cpu = 00:00:03 ; elapsed = 00:00:03 . Memory (MB): peak = 1899.484 ; gain = 0.000 ; free physical = 16990 ; free virtual = 35450

INFO: [v++ 60-1443] [16:53:34] Run run_link: Step rtd2_system_diagram: Started

INFO: [v++ 60-1453] Command Line: rtd2SystemDiagram

INFO: [v++ 60-1454] Run Directory: /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Feature_Tutorials/02-mixing-c-rtl-kernels/reference-files/run2/_x/link/run_link

INFO: [v++ 60-1441] [16:53:34] Run run_link: Step rtd2_system_diagram: Completed

Time (s): cpu = 00:00:00 ; elapsed = 00:00:00.23 . Memory (MB): peak = 1899.484 ; gain = 0.000 ; free physical = 16982 ; free virtual = 35442

INFO: [v++ 60-1443] [16:53:34] Run run_link: Step vpl: Started

INFO: [v++ 60-1453] Command Line: vpl -t hw_emu -f xilinx_u250_gen3x16_xdma_3_1_202020_1 -g --remote_ip_cache /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Feature_Tutorials/02-mixing-c-rtl-kernels/reference-files/run2/.ipcache --output_dir /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Feature_Tutorials/02-mixing-c-rtl-kernels/reference-files/run2/_x/link/int --log_dir /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Feature_Tutorials/02-mixing-c-rtl-kernels/reference-files/run2/_x/logs/link --report_dir /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Feature_Tutorials/02-mixing-c-rtl-kernels/reference-files/run2/_x/reports/link --config /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Feature_Tutorials/02-mixing-c-rtl-kernels/reference-files/run2/_x/link/int/vplConfig.ini -k /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Feature_Tutorials/02-mixing-c-rtl-kernels/reference-files/run2/_x/link/int/kernel_info.dat --webtalk_flag Vitis --temp_dir /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Feature_Tutorials/02-mixing-c-rtl-kernels/reference-files/run2/_x/link --emulation_mode debug_waveform --no-info --iprepo /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Feature_Tutorials/02-mixing-c-rtl-kernels/reference-files/run2/_x/link/int/xo/ip_repo/mycompany_com_kernel_rtl_kernel_wizard_0_1_0 --iprepo /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Feature_Tutorials/02-mixing-c-rtl-kernels/reference-files/run2/_x/link/int/xo/ip_repo/xilinx_com_hls_krnl_vadd_1_0 --messageDb /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Feature_Tutorials/02-mixing-c-rtl-kernels/reference-files/run2/_x/link/run_link/vpl.pb /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Feature_Tutorials/02-mixing-c-rtl-kernels/reference-files/run2/_x/link/int/dr.bd.tcl

INFO: [v++ 60-1454] Run Directory: /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Feature_Tutorials/02-mixing-c-rtl-kernels/reference-files/run2/_x/link/run_link

****** vpl v2021.1 (64-bit)

**** SW Build 3246112 on 2021-06-09-14:19:56

** Copyright 1986-2020 Xilinx, Inc. All Rights Reserved.

INFO: [VPL 60-839] Read in kernel information from file '/home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Feature_Tutorials/02-mixing-c-rtl-kernels/reference-files/run2/_x/link/int/kernel_info.dat'.

INFO: [VPL 74-78] Compiler Version string: 2021.1

INFO: [VPL 60-423] Target device: xilinx_u250_gen3x16_xdma_3_1_202020_1

INFO: [VPL 60-1032] Extracting hardware platform to /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Feature_Tutorials/02-mixing-c-rtl-kernels/reference-files/run2/_x/link/vivado/vpl/.local/hw_platform

[16:53:43] Run vpl: Step create_project: Started

Creating Vivado project.

[16:53:43] Run vpl: Step create_project: Completed

[16:53:43] Run vpl: Step create_bd: Started

[16:53:51] Run vpl: Step create_bd: Completed

[16:53:51] Run vpl: Step update_bd: Started

[16:53:54] Run vpl: Step update_bd: Completed

[16:53:54] Run vpl: Step generate_target: Started

[16:55:09] Run vpl: Step generate_target: RUNNING...

[16:55:25] Run vpl: Step generate_target: Completed

[16:55:25] Run vpl: Step config_hw_emu.gen_scripts: Started

[16:55:38] Run vpl: Step config_hw_emu.gen_scripts: Completed

[16:55:38] Run vpl: Step config_hw_emu.compile: Started

[16:56:11] Run vpl: Step config_hw_emu.compile: Completed

[16:56:11] Run vpl: Step config_hw_emu.elaborate: Started

[16:56:31] Run vpl: Step config_hw_emu.elaborate: Completed

[16:56:32] Run vpl: FINISHED. Run Status: config_hw_emu.elaborate Complete!

INFO: [v++ 60-1441] [16:56:32] Run run_link: Step vpl: Completed

Time (s): cpu = 00:00:04 ; elapsed = 00:02:58 . Memory (MB): peak = 1899.484 ; gain = 0.000 ; free physical = 13727 ; free virtual = 33337

INFO: [v++ 60-1443] [16:56:32] Run run_link: Step rtdgen: Started

INFO: [v++ 60-1453] Command Line: rtdgen

INFO: [v++ 60-1454] Run Directory: /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Feature_Tutorials/02-mixing-c-rtl-kernels/reference-files/run2/_x/link/run_link

INFO: [v++ 60-991] clock name 'kernel2_clk/clk' (clock ID '1') is being mapped to clock name 'KERNEL_CLK' in the xclbin

INFO: [v++ 60-991] clock name 'kernel_clk/clk' (clock ID '0') is being mapped to clock name 'DATA_CLK' in the xclbin

INFO: [v++ 60-1230] The compiler selected the following frequencies for the runtime controllable kernel clock(s) and scalable system clock(s): Kernel (KERNEL) clock: kernel2_clk/clk = 500, Kernel (DATA) clock: kernel_clk/clk = 300

INFO: [v++ 60-1453] Command Line: cf2sw -a /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Feature_Tutorials/02-mixing-c-rtl-kernels/reference-files/run2/_x/link/int/address_map.xml -sdsl /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Feature_Tutorials/02-mixing-c-rtl-kernels/reference-files/run2/_x/link/int/sdsl.dat -xclbin /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Feature_Tutorials/02-mixing-c-rtl-kernels/reference-files/run2/_x/link/int/xclbin_orig.xml -rtd /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Feature_Tutorials/02-mixing-c-rtl-kernels/reference-files/run2/_x/link/int/krnl_vadd.hw_emu.xilinx_u250_gen3x16_xdma_3_1_202020_1.rtd -o /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Feature_Tutorials/02-mixing-c-rtl-kernels/reference-files/run2/_x/link/int/krnl_vadd.hw_emu.xilinx_u250_gen3x16_xdma_3_1_202020_1.xml

INFO: [v++ 60-1652] Cf2sw returned exit code: 0

WARNING: [v++ 60-1455] Debuggable symbols are not generated successfully, clean up /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Feature_Tutorials/02-mixing-c-rtl-kernels/reference-files/run2/_x/link/int/consolidated.cf

INFO: [v++ 60-1441] [16:56:36] Run run_link: Step rtdgen: Completed

Time (s): cpu = 00:00:05 ; elapsed = 00:00:05 . Memory (MB): peak = 1899.484 ; gain = 0.000 ; free physical = 15710 ; free virtual = 35356

INFO: [v++ 60-1443] [16:56:36] Run run_link: Step xclbinutil: Started

INFO: [v++ 60-1453] Command Line: xclbinutil --add-section DEBUG_IP_LAYOUT:JSON:/home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Feature_Tutorials/02-mixing-c-rtl-kernels/reference-files/run2/_x/link/int/debug_ip_layout.rtd --add-section BITSTREAM:RAW:/home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Feature_Tutorials/02-mixing-c-rtl-kernels/reference-files/run2/_x/link/int/behav.xse --force --target hw_emu --key-value SYS:dfx_enable:false --add-section :JSON:/home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Feature_Tutorials/02-mixing-c-rtl-kernels/reference-files/run2/_x/link/int/krnl_vadd.hw_emu.xilinx_u250_gen3x16_xdma_3_1_202020_1.rtd --append-section :JSON:/home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Feature_Tutorials/02-mixing-c-rtl-kernels/reference-files/run2/_x/link/int/appendSection.rtd --add-section CLOCK_FREQ_TOPOLOGY:JSON:/home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Feature_Tutorials/02-mixing-c-rtl-kernels/reference-files/run2/_x/link/int/krnl_vadd.hw_emu.xilinx_u250_gen3x16_xdma_3_1_202020_1_xml.rtd --add-section BUILD_METADATA:JSON:/home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Feature_Tutorials/02-mixing-c-rtl-kernels/reference-files/run2/_x/link/int/krnl_vadd.hw_emu.xilinx_u250_gen3x16_xdma_3_1_202020_1_build.rtd --add-section EMBEDDED_METADATA:RAW:/home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Feature_Tutorials/02-mixing-c-rtl-kernels/reference-files/run2/_x/link/int/krnl_vadd.hw_emu.xilinx_u250_gen3x16_xdma_3_1_202020_1.xml --add-section SYSTEM_METADATA:RAW:/home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Feature_Tutorials/02-mixing-c-rtl-kernels/reference-files/run2/_x/link/int/systemDiagramModelSlrBaseAddress.json --key-value SYS:PlatformVBNV:xilinx_u250_gen3x16_xdma_3_1_202020_1 --output /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Feature_Tutorials/02-mixing-c-rtl-kernels/reference-files/run2/krnl_vadd.hw_emu.xilinx_u250_gen3x16_xdma_3_1_202020_1.xclbin

INFO: [v++ 60-1454] Run Directory: /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Feature_Tutorials/02-mixing-c-rtl-kernels/reference-files/run2/_x/link/run_link

XRT Build Version: 2.11.634 (2021.1)

Build Date: 2021-06-08 22:08:45

Hash ID: 5ad5998d67080f00bca5bf15b3838cf35e0a7b26

Creating a default 'in-memory' xclbin image.

Section: 'DEBUG_IP_LAYOUT'(9) was successfully added.

Size : 1160 bytes

Format : JSON

File : '/home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Feature_Tutorials/02-mixing-c-rtl-kernels/reference-files/run2/_x/link/int/debug_ip_layout.rtd'

Section: 'BITSTREAM'(0) was successfully added.

Size : 38507581 bytes

Format : RAW

File : '/home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Feature_Tutorials/02-mixing-c-rtl-kernels/reference-files/run2/_x/link/int/behav.xse'

Section: 'MEM_TOPOLOGY'(6) was successfully added.

Format : JSON

File : 'mem_topology'

Section: 'IP_LAYOUT'(8) was successfully added.

Format : JSON

File : 'ip_layout'

Section: 'CONNECTIVITY'(7) was successfully added.

Format : JSON

File : 'connectivity'

Section: 'CLOCK_FREQ_TOPOLOGY'(11) was successfully added.

Size : 274 bytes

Format : JSON

File : '/home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Feature_Tutorials/02-mixing-c-rtl-kernels/reference-files/run2/_x/link/int/krnl_vadd.hw_emu.xilinx_u250_gen3x16_xdma_3_1_202020_1_xml.rtd'

Section: 'BUILD_METADATA'(14) was successfully added.

Size : 3069 bytes

Format : JSON

File : '/home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Feature_Tutorials/02-mixing-c-rtl-kernels/reference-files/run2/_x/link/int/krnl_vadd.hw_emu.xilinx_u250_gen3x16_xdma_3_1_202020_1_build.rtd'

Section: 'EMBEDDED_METADATA'(2) was successfully added.

Size : 4665 bytes

Format : RAW

File : '/home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Feature_Tutorials/02-mixing-c-rtl-kernels/reference-files/run2/_x/link/int/krnl_vadd.hw_emu.xilinx_u250_gen3x16_xdma_3_1_202020_1.xml'

Section: 'SYSTEM_METADATA'(22) was successfully added.

Size : 9595 bytes

Format : RAW

File : '/home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Feature_Tutorials/02-mixing-c-rtl-kernels/reference-files/run2/_x/link/int/systemDiagramModelSlrBaseAddress.json'

Section: 'PARTITION_METADATA'(20) was successfully appended to.

Format : JSON

File : 'partition_metadata'

Section: 'IP_LAYOUT'(8) was successfully appended to.

Format : JSON

File : 'ip_layout'

Successfully wrote (38544271 bytes) to the output file: /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Feature_Tutorials/02-mixing-c-rtl-kernels/reference-files/run2/krnl_vadd.hw_emu.xilinx_u250_gen3x16_xdma_3_1_202020_1.xclbin

Leaving xclbinutil.

INFO: [v++ 60-1441] [16:56:36] Run run_link: Step xclbinutil: Completed

Time (s): cpu = 00:00:00.05 ; elapsed = 00:00:00.08 . Memory (MB): peak = 1899.484 ; gain = 0.000 ; free physical = 15672 ; free virtual = 35354

INFO: [v++ 60-1443] [16:56:36] Run run_link: Step xclbinutilinfo: Started

INFO: [v++ 60-1453] Command Line: xclbinutil --quiet --force --info /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Feature_Tutorials/02-mixing-c-rtl-kernels/reference-files/run2/krnl_vadd.hw_emu.xilinx_u250_gen3x16_xdma_3_1_202020_1.xclbin.info --input /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Feature_Tutorials/02-mixing-c-rtl-kernels/reference-files/run2/krnl_vadd.hw_emu.xilinx_u250_gen3x16_xdma_3_1_202020_1.xclbin

INFO: [v++ 60-1454] Run Directory: /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Feature_Tutorials/02-mixing-c-rtl-kernels/reference-files/run2/_x/link/run_link

INFO: [v++ 60-1441] [16:56:37] Run run_link: Step xclbinutilinfo: Completed

Time (s): cpu = 00:00:00.23 ; elapsed = 00:00:00.24 . Memory (MB): peak = 1899.484 ; gain = 0.000 ; free physical = 15672 ; free virtual = 35354

INFO: [v++ 60-1443] [16:56:37] Run run_link: Step generate_sc_driver: Started

INFO: [v++ 60-1453] Command Line:

INFO: [v++ 60-1454] Run Directory: /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Feature_Tutorials/02-mixing-c-rtl-kernels/reference-files/run2/_x/link/run_link

INFO: [v++ 60-1441] [16:56:37] Run run_link: Step generate_sc_driver: Completed

Time (s): cpu = 00:00:00 ; elapsed = 00:00:00 . Memory (MB): peak = 1899.484 ; gain = 0.000 ; free physical = 15672 ; free virtual = 35354

WARNING: [v++ 60-2336] Parameter compiler.enableSlrComputeUnitDrc was set to true, but no SLRs were specified via the command line.

INFO: [v++ 60-244] Generating system estimate report...

INFO: [v++ 60-1092] Generated system estimate report: /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Feature_Tutorials/02-mixing-c-rtl-kernels/reference-files/run2/_x/reports/link/system_estimate_krnl_vadd.hw_emu.xilinx_u250_gen3x16_xdma_3_1_202020_1.xtxt

INFO: [v++ 60-586] Created krnl_vadd.hw_emu.xilinx_u250_gen3x16_xdma_3_1_202020_1.xclbin

INFO: [v++ 60-1307] Run completed. Additional information can be found in:

Guidance: /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Feature_Tutorials/02-mixing-c-rtl-kernels/reference-files/run2/_x/reports/link/v++_link_krnl_vadd.hw_emu.xilinx_u250_gen3x16_xdma_3_1_202020_1_guidance.html

Steps Log File: /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Feature_Tutorials/02-mixing-c-rtl-kernels/reference-files/run2/_x/logs/link/link.steps.log

INFO: [v++ 60-2343] Use the vitis_analyzer tool to visualize and navigate the relevant reports. Run the following command.

vitis_analyzer /home/tkas-user/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Feature_Tutorials/02-mixing-c-rtl-kernels/reference-files/run2/krnl_vadd.hw_emu.xilinx_u250_gen3x16_xdma_3_1_202020_1.xclbin.link_summary

INFO: [v++ 60-791] Total elapsed time: 0h 3m 30s

INFO: [v++ 60-1653] Closing dispatch client.

emconfigutil --platform xilinx_u250_gen3x16_xdma_3_1_202020_1

****** configutil v2021.1 (64-bit)

**** SW Build 3246112 on 2021-06-09-14:19:56

** Copyright 1986-2020 Xilinx, Inc. All Rights Reserved.

INFO: [ConfigUtil 60-895] Target platform: /opt/xilinx/platforms/xilinx_u250_gen3x16_xdma_3_1_202020_1/xilinx_u250_gen3x16_xdma_3_1_202020_1.xpfm

INFO: [ConfigUtil 60-1578] This platform contains Xilinx Shell Archive '/opt/xilinx/platforms/xilinx_u250_gen3x16_xdma_3_1_202020_1/hw/hw.xsa'

INFO: [ConfigUtil 60-1032]

emulation configuration file `emconfig.json` is created in current working directoryAs before, run emulation, and generate and review the Application Timeline by running the following commands from within the run2 directory.Set XCL_EMULATION_MODE environment variable for hardware emulation and Run hardware Emulation

export XCL_EMULATION_MODE=hw_emu

./host krnl_vadd.hw_emu.xilinx_u250_gen3x16_xdma_3_1_202020_1.xclbin

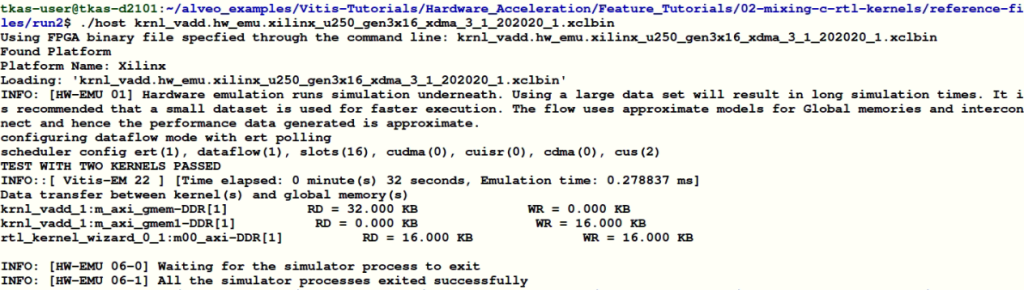

Output message from running hardware emulation

tkas-user@tkas-d2101:~/alveo_examples/Vitis-Tutorials/Hardware_Acceleration/Feature_Tutorials/02-mixing-c-rtl-kernels/reference-files/run2$ ./host krnl_vadd.hw_emu.xilinx_u250_gen3x16_xdma_3_1_202020_1.xclbin

Using FPGA binary file specfied through the command line: krnl_vadd.hw_emu.xilinx_u250_gen3x16_xdma_3_1_202020_1.xclbin

Found Platform

Platform Name: Xilinx

Loading: 'krnl_vadd.hw_emu.xilinx_u250_gen3x16_xdma_3_1_202020_1.xclbin'

INFO: [HW-EMU 01] Hardware emulation runs simulation underneath. Using a large data set will result in long simulation times. It is recommended that a small dataset is used for faster execution. The flow uses approximate models for Global memories and interconnect and hence the performance data generated is approximate.

configuring dataflow mode with ert polling

scheduler config ert(1), dataflow(1), slots(16), cudma(0), cuisr(0), cdma(0), cus(2)

TEST WITH TWO KERNELS PASSED

INFO::[ Vitis-EM 22 ] [Time elapsed: 0 minute(s) 32 seconds, Emulation time: 0.278837 ms]

Data transfer between kernel(s) and global memory(s)

krnl_vadd_1:m_axi_gmem-DDR[1] RD = 32.000 KB WR = 0.000 KB

krnl_vadd_1:m_axi_gmem1-DDR[1] RD = 0.000 KB WR = 16.000 KB

rtl_kernel_wizard_0_1:m00_axi-DDR[1] RD = 16.000 KB WR = 16.000 KB

INFO: [HW-EMU 06-0] Waiting for the simulator process to exit

INFO: [HW-EMU 06-1] All the simulator processes exited successfully

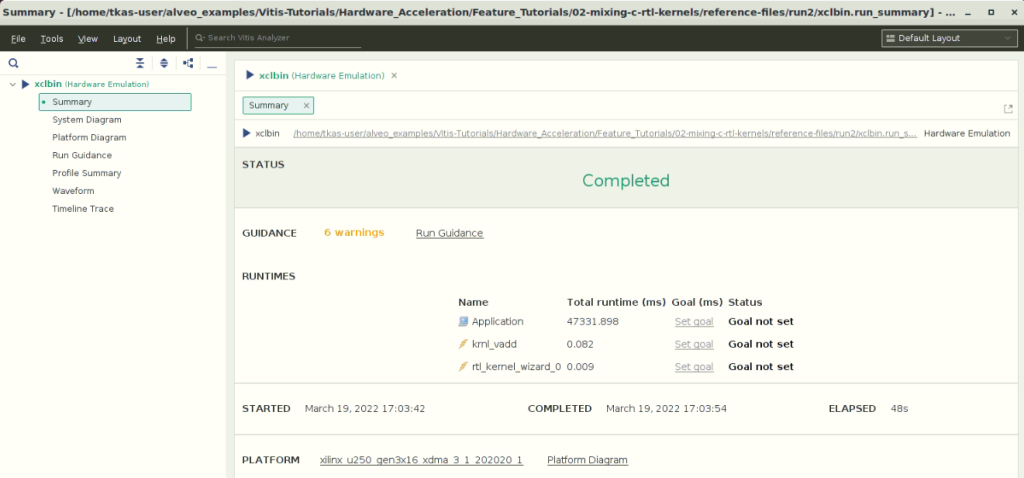

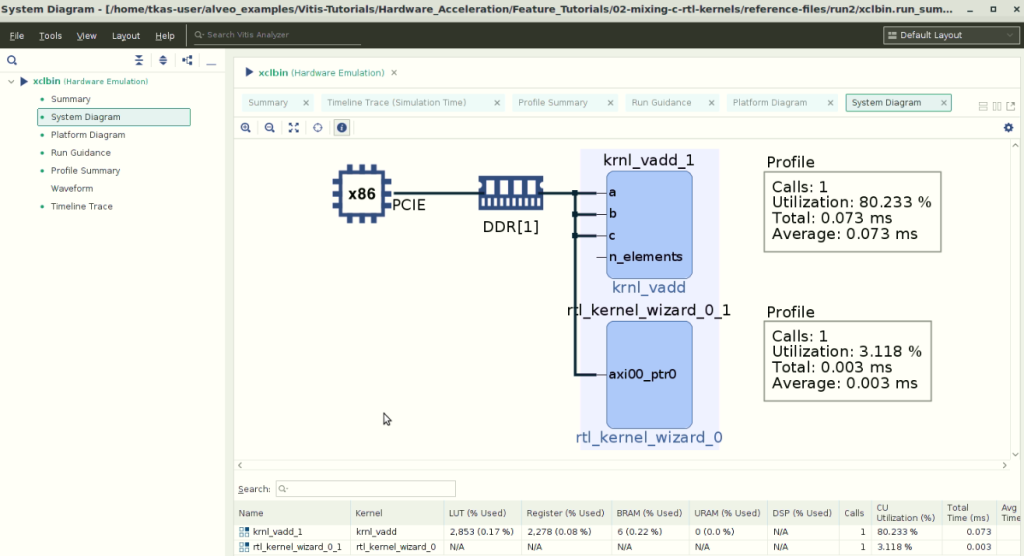

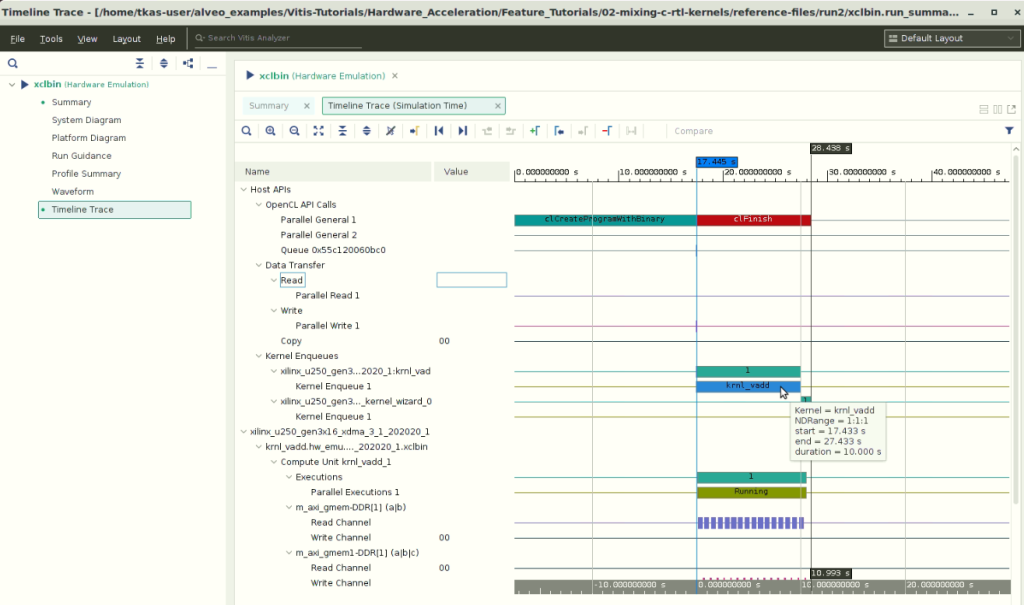

View the Application Timeline report in the Vitis analyzer.

vitis_analyzer xclbin.run_summary

After reviewing, close the Application Timeline, and exit Vitis analyzer.

RTL kernel as Vivado project

==================== END ====================