AAT Demo Datamover with Hardware Emulation

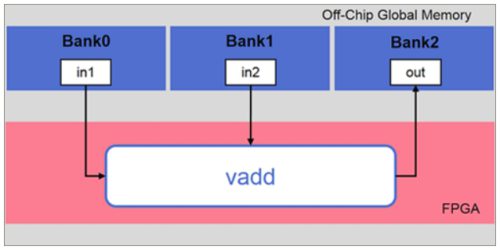

Datamover on AAT Demo After Both tutorial on AAT demo focusing on the running the AAT. Now, it is time to look in its features which is called Datamover. The Datamover provides a bi-directional datapath to the host. The uplink is used for transferring the updated Orderbook and the downlink transfer the requests to trade. There are 2 types of...