rmNVMe IPコアCPU不要で同時にNVMeSSDへの複数データストリーム・アクセス!

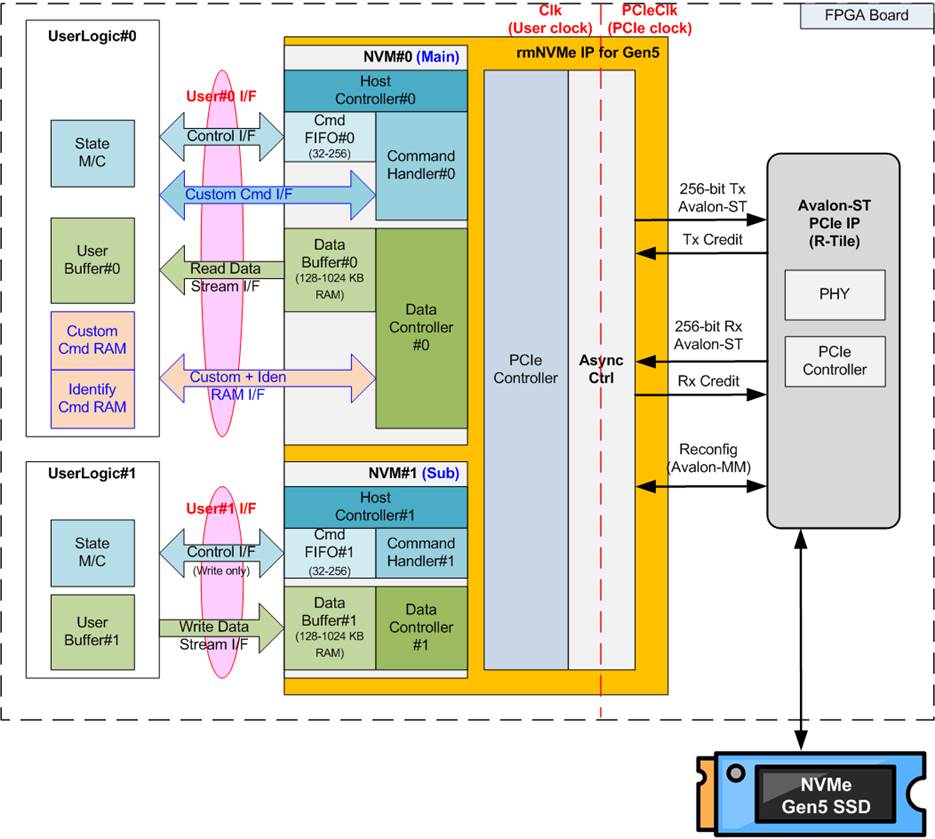

rmNVMe-IP (ランダム・アクセス&マルチ・ユーザー NVMe IP) は、高IOPS ランダム・アクセスを要求するアプリケーション向けに高度に最適化された、超高性能NVMe ホスト・コントローラーです。 rmNVMe-IP

は複数のユーザー・インターフェイスをサポートし、各ユーザーは単一NVMe SSDに対して同時にリード/ライトアクセスを実行できます。

rmNVMe-IP は、リアルタイムでのセンサー・データの融合/処理、OS/ファイルシステムのオフロードなど、高速ランダム・アクセス・パフォーマンスを必要とするアプリケーションに最適です。CPU不要で完全ハードウェア・ロジック構成のため、エネルギー効率、高パフォーマンス、低消費リソースの面で大きなアドバンテージがあります。

| CPU/外部メモリ不要 Gen5対応 標準版 |

PCIe Soft IP内蔵 PCIe Hard IP不要 |

500K IOPS超の ランダム・アクセス |

マルチ・ユーザー R/W同時対応 |

マルチ・ユーザー ランダム・アクセス |

|

|

|

|

|

rmNVMe-IP 紹介ビデオ

|

|

特長

|

ブロック図 * Click to show more detail |

詳細資料ダウンロード

またDGニュースから通知を受け取ることができます。DGニュースを受け取る

技術詳細資料 & 無償評価ファイル

| 対応デバイス | Agilex™ 7 シリーズ |

||||

| IP core | データシート | リファレンスデザインドキュメント | デモ手順書 | 無償評価デモファイル | デモビデオ |

| rmNVMe-IP (Gen5) |

Rev1.0 | Rev1.0 | Rev1.0 | Agilex-I |  |

| rmNVMe-IP (Gen4) |

Rev1.0 | Rev1.0 | Rev1.1 | Agilex-F | |

アプリケーション例

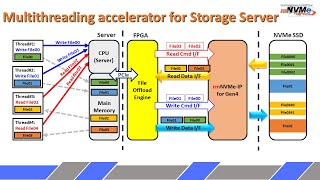

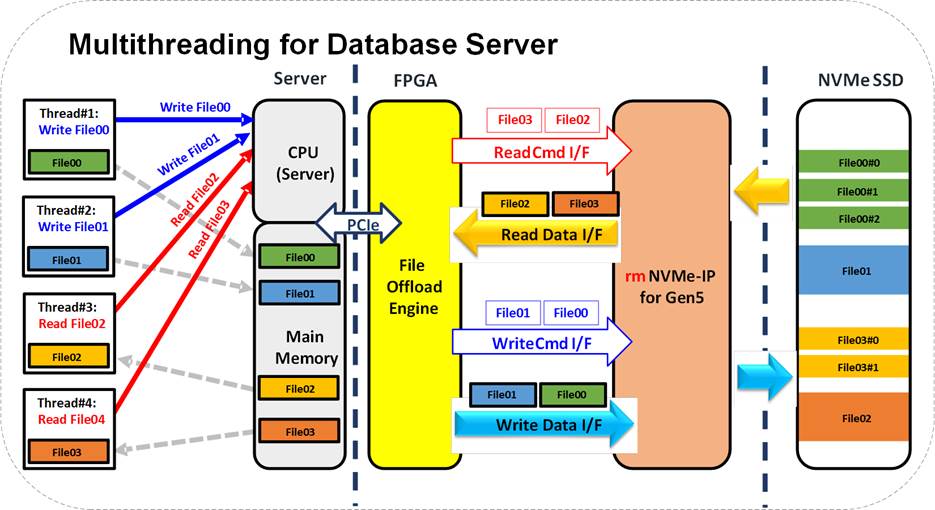

データベース・サーバーのマルチ・スレッド化

FPGAは、データベース・サーバーがNVMe SSDにアクセスするためのオフロード・エンジンとして使われます。大規模なシステムでは、複数のスレッドがデータベースにアクセスし、多くの読み書き要求がCPUに送られます。大容量データの書き込みは通常、メインメモリに保存されます。FPGAプラットフォームのPCIeエンジンは、オフロードエンジンがCPUからコマンド要求を受け取り、高性能で直接メインメモリ内のデータにアクセスできるようにインターフェースを提供します。

ファイル・オフロード・エンジンは、読み取りコマンド・インターフェースと書き込みコマンド・インターフェースを通じてrmNVMe IPに読み書きの要求を送信します。書き込みデータは全て、書き込みデータ・インターフェースを通じてNVMe SSDに保存され、NVMe SSDからの読み込みデータは読み込みデータ・インターフェースを介してファイルオフロードエンジンに戻り、最終的にはメインメモリを通じてスレッドに返されます。

このハードウェア・システムにより、データベースに高性能アクセスできると同時に、CPUリソースを少なく済ませることが可能になります。

Alliance Partner

株式会社デザイン・ゲートウェイ

本社東京都小金井市中町3-23-17

R&D

89/26 Amornpan 205 Tower1, 18th floor, Ratchadapisek7 (Nathong) Alley, Ratchadapisek Road, Din Daeng, Bangkok, 10400 THAILAND

AI Lab

Faculty of Engineering, Chulalongkorn University, 12th floor, Engineering 4 Building (Charoenvidsavakham), Phayathai Rd., Wang Mai, Pathumwan, Bangkok, 10330 THAILAND