CPU-less TLS1.3 Offload IP core for FPGA Acceleration

Features┃Block diagram┃Document Download┃Performance Comparison┃Applications

Please receive technical document update from DG News Letter. Subscribe to DG News

Please receive technical document update from DG News Letter. Subscribe to DG News

Technical document update page

Technical document update page

About price and licence of the IP core, please contact Design Gateway.

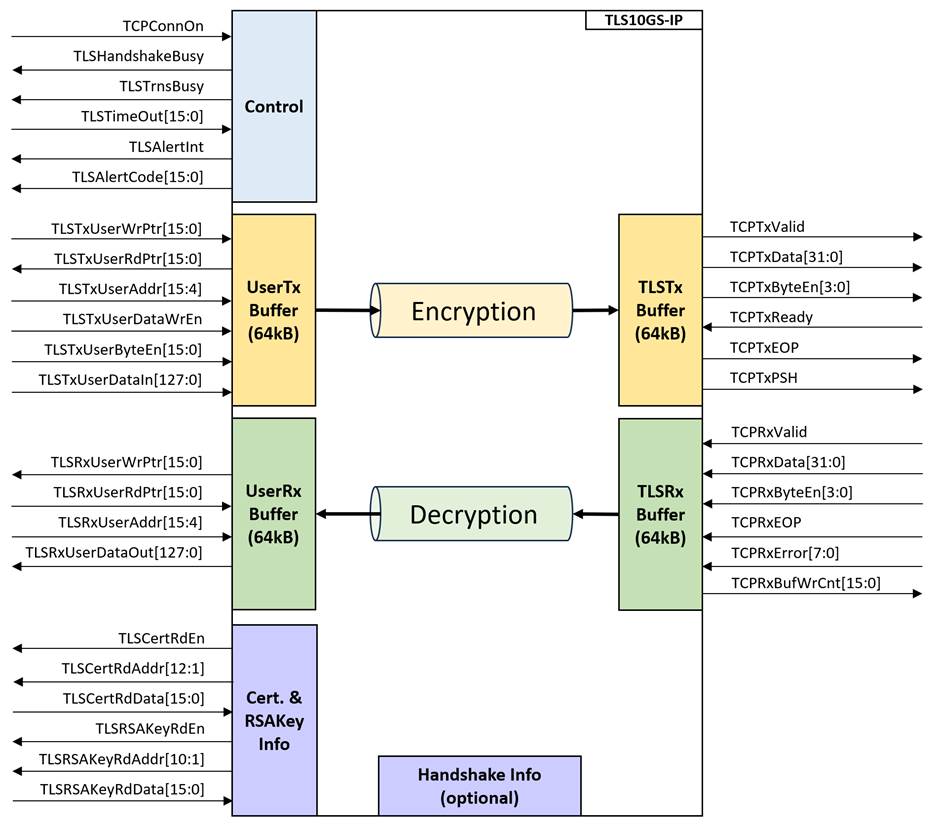

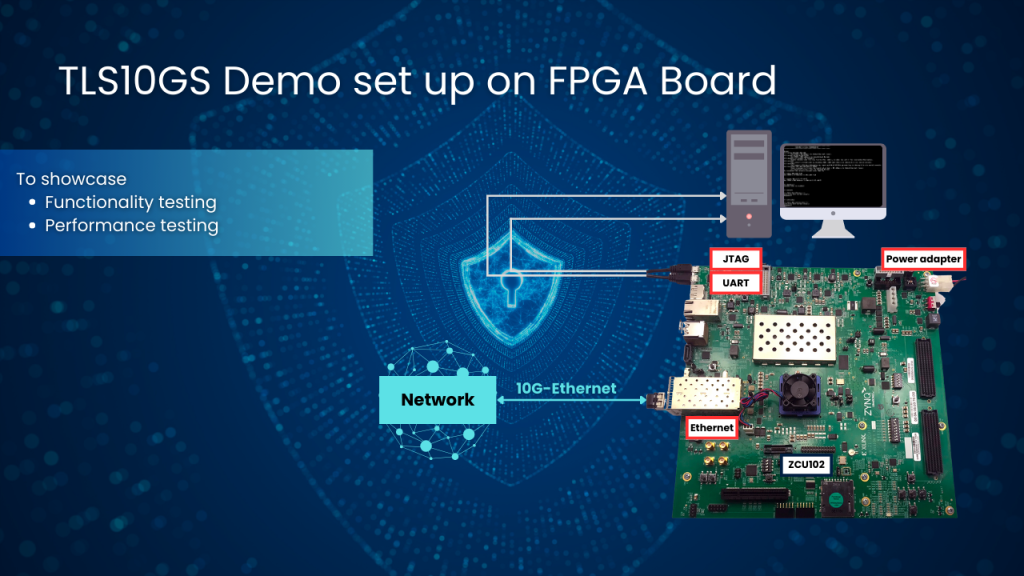

TLS1.3 IP (Transport Layer Security IP) is the CPU-less & High-performance TLS v1.3 protocol engine for FPGA Acceleration with no CPU and external memory required. Providing maximum Gigabit Ethernet throughput for highly secure data transmission over 1G/10G/25G/100G network. Protect your valuable data from potential security breaches by using TLS secure transmission now! Especially, in Industrial IoT & Automation, Aerospace & Defense Applications.

Our TLS 1.3 IP core demo can successfully demonstrate very high throughput HTTPS Upload and Download with standard web server by pure hardware logic on FPGA.

Features

|

Block diagram * Click to show more detail |

Document download

Technical Documents

| Support Devices | please contact us | ||||

| IP core | Datasheet | Reference Design Document | Demo Instruction Document | Free Evaluation demo file | |

| TLS 1.3 Server 10G IP |

contact us | ||||

|

|

|||||

| TLS 1.3 Client 10G IP |

contact us | ||||

|

|

|||||

| TLS 1.3 Client 1G IP |

contact us | ||||

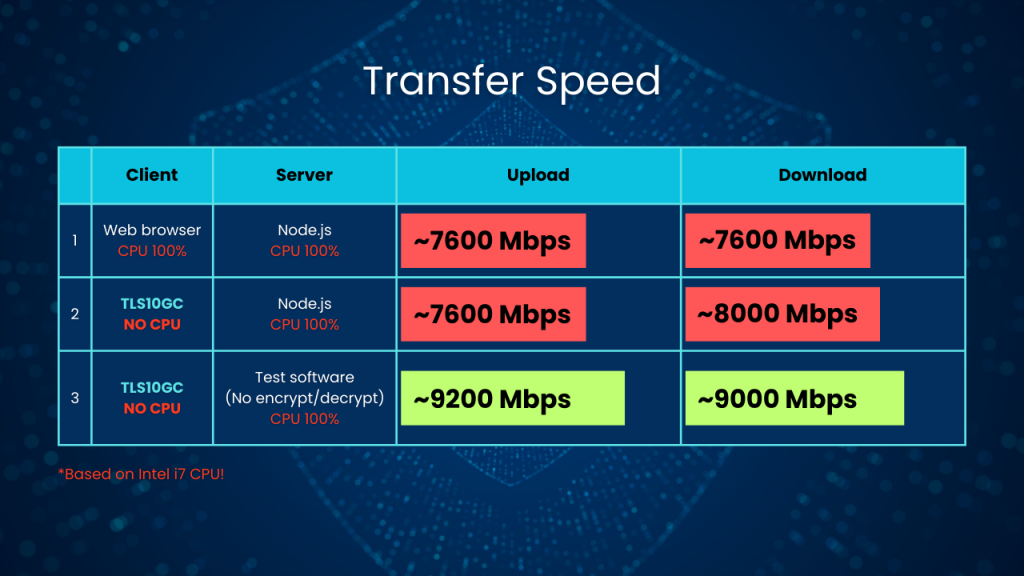

Performance Comparison

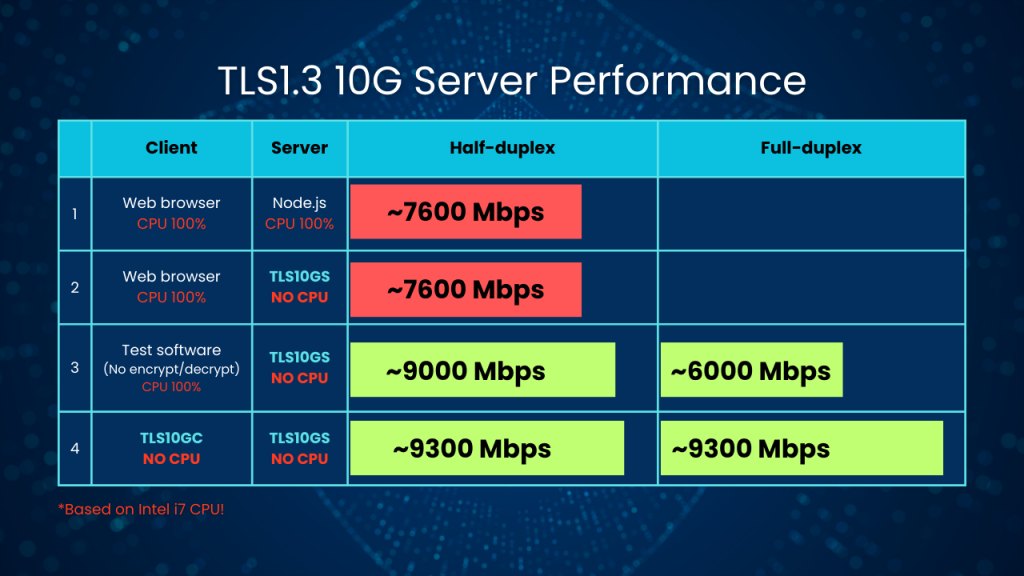

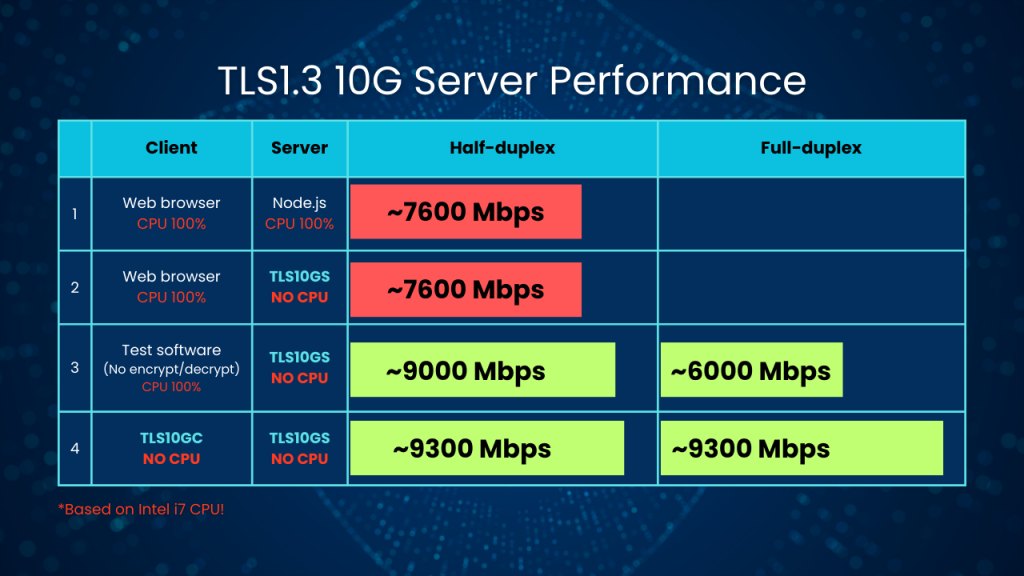

TLS1.3 Server 10G IP

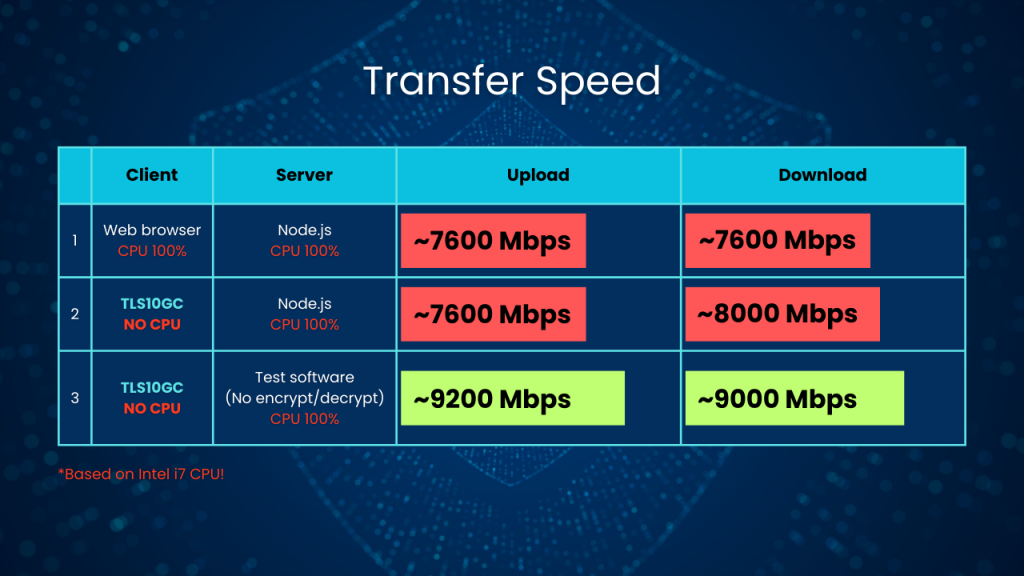

TLS1.3 Client 10G IP

Free evaluation before purchasing

|

Free evaluation demo is available on Altera FPGA boards. contact us |

Application example

.png) |

Aerospace TelemetryEnsure the integrity and confidentiality of sensitive inflight data streams from remote sensors in aerospace applications. FPGA-accelerated TLS 1.3 outpaces software-only solutions, safeguarding critical flight information. Read more |

.png) |

Medical Device ConnectivityProtect patient data in transit between medical devices and healthcare systems. Our solution provides the robust encryption and authentication mechanisms needed to comply with stringent healthcare regulations and safeguard patient privacy. Read more |

About price and licence of the IP core, please contact Design Gateway.

Alliance Partner

Design Gateway Co., Ltd.

Head Office3-23-17 Naka-cho, Koganei, Tokyo, JAPAN

R&D

89/26 Amornpan 205 Tower1, 18th floor, Ratchadapisek7 (Nathong) Alley, Ratchadapisek Road, Din Daeng, Bangkok, 10400 THAILAND

AI Lab

Faculty of Engineering, Chulalongkorn University, 12th floor, Engineering 4 Building (Charoenvidsavakham), Phayathai Rd., Wang Mai, Pathumwan, Bangkok, 10330 THAILAND