FPGA SolutionsApplications

FPGA Solutions for Vertical Market

|

We specialize in Intellectual Property (IP) Core & Solution development, which is designed from ground up to simplify complex protocols processing without need CPU. Our design philosophy is to create the hardware solutions that optimize for high performance, simple usage, while using lowest possible resources. We cover various domains such as data storage, networking, security, and application-specific protocol engines targeting FPGA platforms. DG's IP core Solutions for Vertical Market page to introduces application example by FPGA & DG IPs. Learn More |

Aerospace |

Automotive |

Media |

AI |

HPC |

Finance |

MFG |

Medical |

Robotics |

Fintech

Design Gateway's super low latency Network IP cores have been adopted by a strategic customer in Thailand to implement software-based trading algorithms into FPGA Accelerator using AMD's high-level synthesis framework and super low latency trading reference design from Design Gateway. This has resulted in a significant trading latency improvement from millisecond level down to microsecond level or even faster. Learn more

FPGA-based accelerator systems proven to deliver ultra-fast trading capabilities at the Stock Exchange of Thailand

|

Turnkey Accelerator system

|

TKAS-D2101 Specification

|

Cloud Storage

Most cloud infrastructures use Network Interface Cards (NICs) for NVMe/TCP connections. However, traditional CPU-based storage solutions face bottlenecks, high power consumption, and scalability issues.

.png) |

To solve these challenges, Design Gateway and DYNANIC have developed an FPGA-based NVMe/TCP offload engine. This innovation offers:

This breakthrough enhances cloud storage performance, making it more scalable and energy-efficient. Watch our live demo to see how the system:

Ready to boost your cloud storage with FPGA-powered acceleration? Contact Us |

FPGA Accelerator Cards

Alveo V80 |

Alveo V70 |

Alveo U50 |

Alveo U45N |

Alveo X3522PV |

Document download

| Document name |

| Presentation : IP Cores & Solutions for FPGA Accelerator |

| Product Leaflet : Alveo Card |

| Getting Started with Turnkey Accelerator Systems TKAS-D2101 |

Avilable Demos on Alveo Accelerator card

| Devices | Alveo U250, Alveo U50 |

||||

| IP core | Demo | Reference Design Document | Demo Instruction Document | FPGA Board Setup | Free Evaluation demo file |

LL Network IP |

Accelerated Algorithmic Trading (AAT) Demo | Rev2.0 | Rev1.1 | U250 U50 |

|

LL 10G EMAC IP |

Accelerated Algorithmic Trading (AAT) QDMA Demo | Rev1.00 | X3522 U50 U55C U250 |

||

LL 10G EMAC IP |

Accelerated Algorithmic Trading (AAT) Demo | Rev1.0 | Rev1.1 | U250 U50 |

|

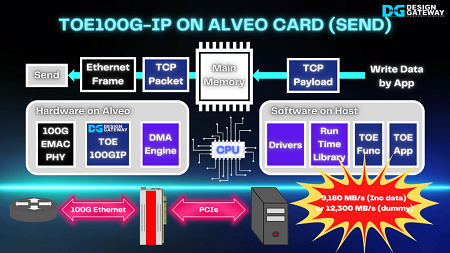

TOE100G-IP |

DMA Demo | Rev1.0 | Rev1.0 | Rev1.0 | U250 U50 |

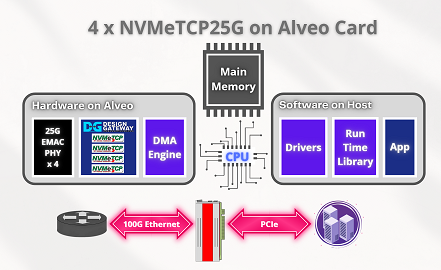

NVMeTCP25G-IP |

4ch Demo | Rev1.0 | Rev1.0 | U50 | |

Demo Video on Youtube | Blog Article |

AAT QDMA DemoAccelerated Algorithmic Trading (AAT) demo originated from AMD/Xilinx to demonstrate the HFT environment with the Alveo card. At first, the target system acts as the stock market will send UDP market data to the Alveo card. The AAT system on the Alveo captures and processes the market data, then returns the TCP trading order back to the target system. Design Gateway improves the original demo and develop on the Vivado platform and integrating DG LL10G Ethernet MAC IP to minimize this demo latency. |

Demo Video on Youtube | Blog Article |

4 x NVMeTCP25G DemoDesign Gateway provide 4 x NVMeTCP25G reference design on Alveo Card to fully utilize 100GbE (25G x 4) Ethernet interface port on Alveo Card and demonstrate NVMe/TCP Host performance on Alveo Card with NVMeTCP Target. Each NVMeTCP connection performance can achieve 2GB/s or more depended on NVMeTCP Target. This reference design is available for NVMeTCP25G core customer for evaluation and shorten your development time. |

|

Full 100G TCP offload by TOE100G-IPTCP transmission at 100G speed is a compute-intensive workload for CPUs and it is difficult to achieve high sustained throughput without hardware accelerator. TOE100G-IP Core is designed to fully offload TCP transmission from CPU by pure hardware logic. Our demo application on Alveo Card can achieve nearly 100G throughput with minimal CPU usage. |

YouTube Video Series

Product Introduction [EP0] |

System Setup & Validation [EP1] |

DG LL 10G EMAC-IP with AMD’s AAT demo [EP2] |

GZIP Compression demo [EP3] Gzip demo on Alveo |

Blogs

Alliance Partner

Design Gateway Co., Ltd.

Head Office3-23-17 Naka-cho, Koganei, Tokyo, JAPAN

R&D

89/26 Amornpan 205 Tower1, 18th floor, Ratchadapisek7 (Nathong) Alley, Ratchadapisek Road, Din Daeng, Bangkok, 10400 THAILAND

AI Lab

Faculty of Engineering, Chulalongkorn University, 12th floor, Engineering 4 Building (Charoenvidsavakham), Phayathai Rd., Wang Mai, Pathumwan, Bangkok, 10330 THAILAND