NVMe over TCP IP coreEnd-to-End NVMe-oF TCP connectivity with no CPU!

NVMeTCP IP is the standalone host side NVMe Over Fabric (NVMe/TCP) controller with

no CPU and external memory required. Enabling very high-performance remote

access to NVMe-oF Storage Server by simple user logic. Greatly reduce design

complexity and development time. Allowing your FPGA Card/Board to get access

to the existing NVMe-oF storage infrastructure remotely and directly over

FPGA’s network interface with maximum possible performance.

This IP core license includes the reference design for Altera FPGA boards.

It helps you to reduce development time and cost.

Features

- NVMe/TCP (NVMe over TCP) host controller (Initiator), based on NVMe-oF specification rev 1.1 and NVMe specification rev 1.4

- Access one NVMe SSD on the target (Subsystem), selected by NVMe name (NQN)

- Command: Write and Read

- High performance:

- NVMeTCP25G-IP: Write at 2500 Mbyte/s and Read at 2600 Mbyte/s (1Mbyte buffer)

- NVMeTCP10G-IP: Write at 1200 Mbyte/s and Read at 1200 Mbyte/s (1Mbyte buffer)

- Data interface: Memory-mapped interface

- Data size per command: Fixed at 4 Kbytes

- Maximum command: 256 or less, limited by Read buffer size for Read command

- Configurable Read buffer size: 32Kbytes (up to 8 Read Cmd) - 1Mbytes (up to 256 Read Cmd)

- Supported NVMe/TCP target:

- IOCCSZ (I/O Queue Command Capsule Support Size): More than or equal to 4160 (1040h)

- MQES (Maximum Queue Entries Supported): More than or equal to 256 (100h)

- MAXCMD (Maximum Outstanding Commands): More than or equal to 256 (100h)

- Authentication: Not required

- Networking: 10Gb Ethernet speed in the same network for transferring ARP request/reply packet by using jumbo frame packet

- Customized service

- NVMe/TCP Target in different network that cannot transfer ARP packet to get Target MAC address

- The network that does not support jumbo frame packet

- NVMe-IP for Altera FPGAs listed on Altera Solution Acceleration Partner Offerings

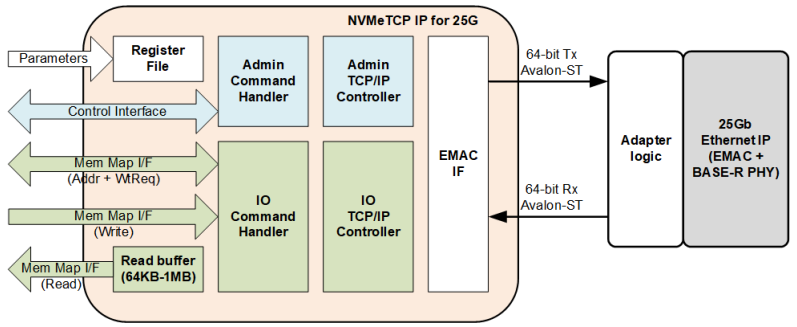

Block diagram

Document download

YouTube Video

|

Accelerating Cloud Storage with FPGA-Based NVMe over TCP |

|

Live Demo: FPGA-Accelerated Cloud Storage with NVMe/TCP |

Documents for each Device families

| Support Devices | Arria 10 GX | |||||

| IP core & Option | Datasheet | Reference Design Document | Demo Instruction Document | FPGA Board Set up Document | Free Evaluation demo file | |

| NVMeTCP25G-IP | Rev1.0 | Rev1.0 | Rev1.0 | Rev1.0 | Agilex-F | |

| Cloud Accelerator Demo | Rev1.00 | Rev1.00 | N6010 |  |

||

|

|

||||||

| NVMeTCP10G-IP | Rev1.0 | Rev1.0 | Rev1.1 | Rev1.0 | A10GX | |

Free demo file for evaluation

Free evaluation demo is available on Altera FPGA boards.Merits & Advantages of NVMeTCP IP core

- Simply attach the remote NVMe SSD Storage to your FPGA Card/Board without PCIe hard IP and/or MPSoC

- Very high performance with over 95% network bandwidth utilization.

- Enabling NVMeoF(NVMe/TCP) host side on your FPGA with no CPU and DDR

- Scalable storage capacity & performance with multiple IPs implementation

Application example

.jpg) |

AutomotiveIn modern vehicles, FPGAs often handle data from sensors, cameras, and radar systems. With our NVMeTCP IP Core, this data can be processed in real-time and then sent via 10G or 25G Ethernet to a remote NVMeTCP storage server. This approach not only saves space and power on the vehicle but also ensures that massive amounts of data are stored reliably and efficiently. More solution |

.jpg) |

AerospaceAt satellite ground stations, FPGAs manage the downlink of data from satellites. By utilizing the NVMeTCP IP Core, this critical data can be quickly transmitted over 10G or 25G Ethernet to remote storage servers. This method allows for the secure and efficient storage of large volumes

of satellite data without compromising on performance or scalability. |

About price and licence of this IP core, please contact Design Gateway.

Alliance Partner

Design Gateway Co., Ltd.

Head Office3-23-17 Naka-cho, Koganei, Tokyo, JAPAN

R&D

89/26 Amornpan 205 Tower1, 18th floor, Ratchadapisek7 (Nathong) Alley, Ratchadapisek Road, Din Daeng, Bangkok, 10400 THAILAND

AI Lab

Faculty of Engineering, Chulalongkorn University, 12th floor, Engineering 4 Building (Charoenvidsavakham), Phayathai Rd., Wang Mai, Pathumwan, Bangkok, 10330 THAILAND