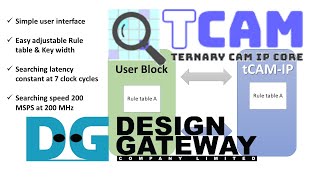

tCAM IP core300 MSPS by constant latency at 7 clock cycles

Features┃Block diagram┃Document Download┃Applications

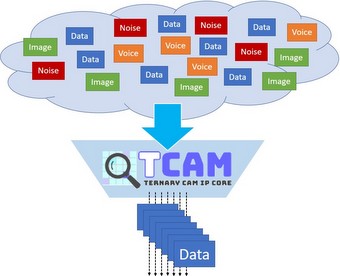

tCAM-IP is a high performance, extremely low latency and highly configurable ternary

content-addressable memory IP. tCAM-IP can make deterministic search at

300 MSPS continuously speed with constant latency at 7 clock cycles. It can achieve matching/filtering performance at 300,000,000 packets

per second over 40G/100G Ethernet. It is ideal for variant applications

such as network packet filtering/forwarding, intelligent switch/router,

deep packet inspection and network security application. We can provide

tCAM-IP custom reference design together with TOE40G/10G/1G-IP, UDP40G/10G/1G-IP, EMAC-IP based on customer requirements. Contact Us

tCAM-IP is a high performance, extremely low latency and highly configurable ternary

content-addressable memory IP. tCAM-IP can make deterministic search at

300 MSPS continuously speed with constant latency at 7 clock cycles. It can achieve matching/filtering performance at 300,000,000 packets

per second over 40G/100G Ethernet. It is ideal for variant applications

such as network packet filtering/forwarding, intelligent switch/router,

deep packet inspection and network security application. We can provide

tCAM-IP custom reference design together with TOE40G/10G/1G-IP, UDP40G/10G/1G-IP, EMAC-IP based on customer requirements. Contact Us

Please receive technical document update from DG News Letter. Subscribe to DG News

Please receive technical document update from DG News Letter. Subscribe to DG News

Technical document update page

Technical document update page

For more detail, please Contact Us

tCAM-IP is a high performance, extremely low latency and highly configurable ternary

content-addressable memory IP. tCAM-IP can make deterministic search at

300 MSPS continuously speed with constant latency at 7 clock cycles. It can achieve matching/filtering performance at 300,000,000 packets

per second over 40G/100G Ethernet. It is ideal for variant applications

such as network packet filtering/forwarding, intelligent switch/router,

deep packet inspection and network security application. We can provide

tCAM-IP custom reference design together with TOE40G/10G/1G-IP, UDP40G/10G/1G-IP, EMAC-IP based on customer requirements. Contact Us

tCAM-IP is a high performance, extremely low latency and highly configurable ternary

content-addressable memory IP. tCAM-IP can make deterministic search at

300 MSPS continuously speed with constant latency at 7 clock cycles. It can achieve matching/filtering performance at 300,000,000 packets

per second over 40G/100G Ethernet. It is ideal for variant applications

such as network packet filtering/forwarding, intelligent switch/router,

deep packet inspection and network security application. We can provide

tCAM-IP custom reference design together with TOE40G/10G/1G-IP, UDP40G/10G/1G-IP, EMAC-IP based on customer requirements. Contact UsFeatures

|

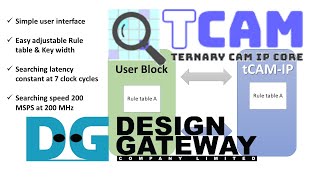

Super High-speed Searching & Filtering |

YouTube Video |

|

tCAM-IP introduction |

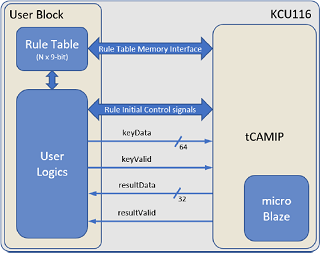

Block Diagram

|

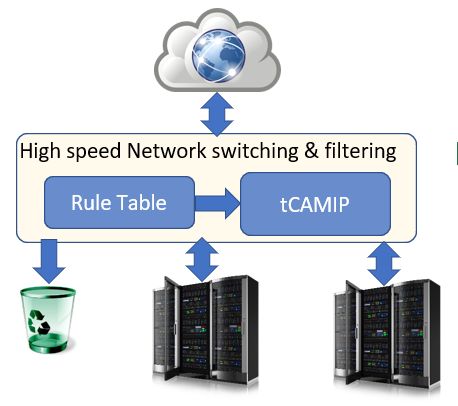

Example Block Diagram for Network switching & filtering application |

Document & Demo file download

| Document name | tCAM-IP |

| Presentation | Rev1.0XE |

| Introduction Video |

|

Technical Documents & Free Evaluation files

| Document Name | AMD |

| Datasheet | Rev2.00 |

| Reference Design Document | Rev2.01 |

| Demo Instruction Document | Rev2.01 |

| Free Evaluation Demo file | KCU116 |

|

|

|

|

|

| UDP Packet Switching Reference Design Document | Rev1.00 |

| UDP Packet Switching Demo Instruction | Rev1.01 |

| UDP Packet Switching Demo Free Evaluation file | KCU116 |

|

|

Alliance Partner

Design Gateway Co., Ltd.

Head Office3-23-17 Naka-cho, Koganei, Tokyo, JAPAN

R&D

89/26 Amornpan 205 Tower1, 18th floor, Ratchadapisek7 (Nathong) Alley, Ratchadapisek Road, Din Daeng, Bangkok, 10400 THAILAND

AI Lab

Faculty of Engineering, Chulalongkorn University, 12th floor, Engineering 4 Building (Charoenvidsavakham), Phayathai Rd., Wang Mai, Pathumwan, Bangkok, 10330 THAILAND