TOE-IPコア シリーズTOE200G-IP が Agilex I シリーズに対応!!

特長┃ブロック図┃資料ダウンロード┃アプリケーション例┃注文情報

最新資料アップデート情報はこちらで確認できます。

最新資料アップデート情報はこちらで確認できます。

またDGニュースから通知を受け取ることができます。DGニュースを受け取る

1分でわかる記事: TCP通信のマルチ・セッションで100GbE帯域を最大活用

1分でわかる記事: TCP通信のマルチ・セッションで100GbE帯域を最大活用

TOE100G-IP紹介&アプリ例は、YouTubeで視聴頂けます。こちら

TOE100G-IPと最適アプリが1分でわかる 動画まとめ記事

ブログ記事: 医療、テスト・計測、航空宇宙、産業向けアプリケーションに実績 10G TCPオフロード・エンジンIPコア

TCP/IPオフローディング・エンジンIPコア (TOE200G/100G/40G/25G/10G/1G-IP) は、従来高価なハイエンドCPUを必要とされた複雑なTCP/IP送受信処理を、外部CPUでの処理を必要としないCPUレスの純ハードロジックのみで構成した画期的なソリューションです。 Altera社のFPGAに対応したリファレンスデザインをコア製品に標準添付しており、製品開発の短縮に役立てることができます。 また、Altera社製FPGAボード用評価デモファイルを準備しておりますので、購入前に無償で本コアを実機で評価・お試し頂けます。

特長

|

|

ブロック図

TOE200GADV-IP |

TOE100G-IP |

||

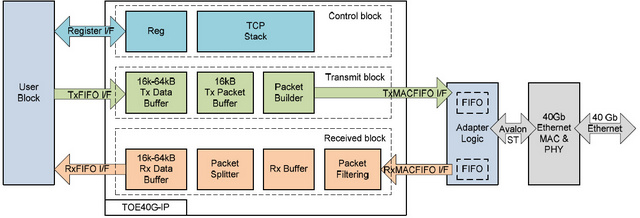

TOE40G-IP |

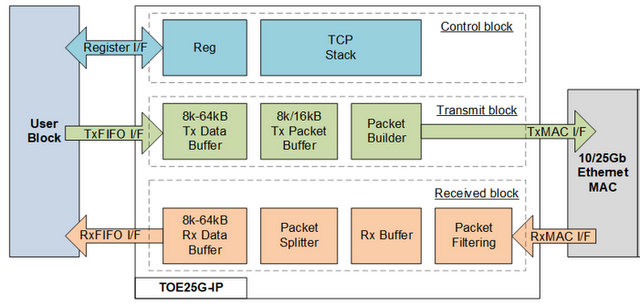

TOE25G-IP |

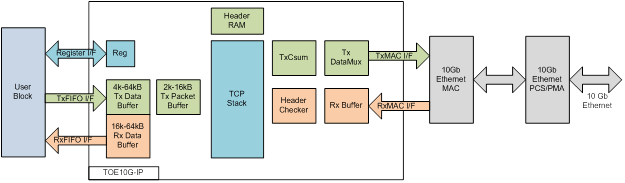

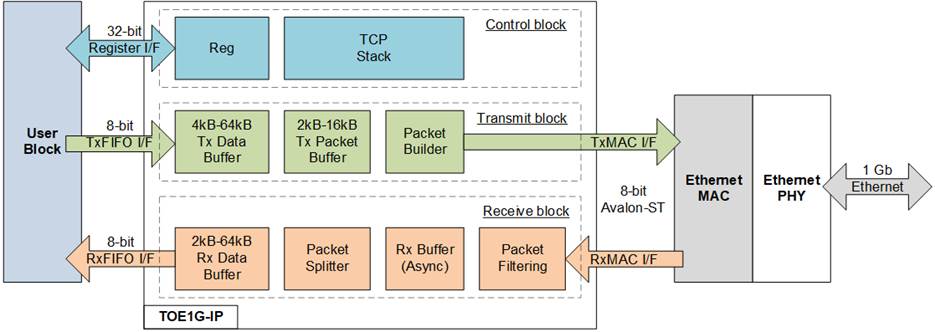

TOE10G-IP |

TOE1G-IP |

詳細資料ダウンロード

またDGニュースから通知を受け取ることができます。DGニュースを受け取る

営業用資料

| 資料 | リビジョン |

| ギガビットIPコア ブロシュアー | Rev2025Q1JA |

| TOE-IPコアシリーズ プレゼンテーション | Rev2.0AJ |

| TOE10G-IP 用 10GEMAC-IP プレゼンテーション | Rev1.0AJ |

| 紹介ビデオ |

TOE25G-IP 紹介 |

| ブログ記事 |

- |

デバイスファミリ別詳細資料 & 無償評価ファイル

| 対応デバイス | Agilex™ 7 I-Series/F-Series, Stratix®10 MX/TX | |||||

| IPコア & オプション |

データシート | リファレンスデザイン ドキュメント | デモ手順書 | FPGAボード セットアップ手順書 | 無償評価デモファイル | |

TOE200GADV-IP TOE200GADV-IP |

Rev1.01 | Rev1.00 | Rev1.00 | Rev1.00 | Agilex™ 7 I-Series |

|

TOE100GADV-IP TOE100GADV-IP |

Agilex™ 7 I-Series |

|||||

TOE100G-IP TOE100G-IP |

Rev2.0 | Rev2.1 | Rev1.2 | Rev3.2 | Agilex™ 7 F-Series Stratix 10 MX Stratix 10 TX |

|

| 4セッション | Rev1.0 | Rev1.0 | Rev3.2 | Stratix 10 TX | ||

| 対応デバイス | Altera PAC, Arria®10 GX | |||||

TOE40G-IP TOE40G-IP |

Rev1.1 | Rev1.0 | Rev1.0 | Arria 10 GX |  |

|

| Altera PAC | Rev1.0 | Rev1.0 | Altera PAC |  |

||

| 対応デバイス | Agilex™ 7 F-Series, Stratix®10 GX | |||||

TOE25G-IP TOE25G-IP |

Rev1.3 | Rev1.2 | Rev1.3 | Rev2.2 | Agilex-F Stratix 10 GX Stratix 10 MX |

|

| 対応デバイス | IntelPAC, Stratix® 10 GX, Arria® 10 SX, Arria® 10 GX, Cyclone® 10 GX | |||||

| IPコア &オプション |

データシート | リファレンスデザイン | デモ手順書 | FPGA ボードセットアップ | 無償評価デモファイル | |

TOE10G-IP TOE10G-IP |

Rev2.00 | Rev2.00 Rev1.0 (PAC) |

Rev2.04 Rev1.0 (PAC) |

Rev3.2 | Altera PAC Stratix 10 GX Stratix 10 MX Arria 10 SX Arria 10 GX Cyclone 10 GX |

Arria 10 SX  Altera PAC |

| 2 port デモ | Rev1.01 | Rev1.0 | Rev3.2 | Arria 10 GX | ||

| 10G EMAC-IP | Rev1.2 | Rev1.0 | Rev1.0 | Cyclone 10 GX | ||

| マルチセッション | Rev1.0J | Rev1.0J | Arria 10 SX | |||

| 対応デバイス | Arria® 10 SX, Cyclone® 10 GX, Arria® V GX, Cyclone® V E, Stratix® IV GX | |||||

TOE1G-IP TOE1G-IP |

Rev3.01 | Rev2.00 | Rev2.02 | Rev2.02 | Arria 10 SX Arria 10 GX Arria V GX Cyclone V E |

|

| 2 port デモ | Rev1.0 | Rev1.0 | Cyclone 10 GX | |||

| FTP サーバ デモ with SATA-IP & exFAT-IP | Rev1.0 | Rev1.0 | Cyclone 10 GX |  |

||

マルチ・セッション リファレンス・デザインで、PCとのTCP通信を最大化

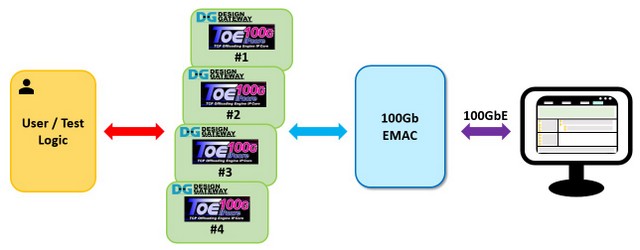

| TOE100G-IP マルチ・セッション リファレンス・デザインは、TOE100G-IP複数インスタンスによりマルチ・セッションの同時転送を可能にすることで、TCPスループットを最大化します。 マルチ・セッション化により、PCの制約により生じるTCP通信のパフォーマンスの低下を大幅に改善し、高価なエンタープライズ向けサーバーではなくても、超高速TCP通信を実現するソリューションを提供します。 |

|

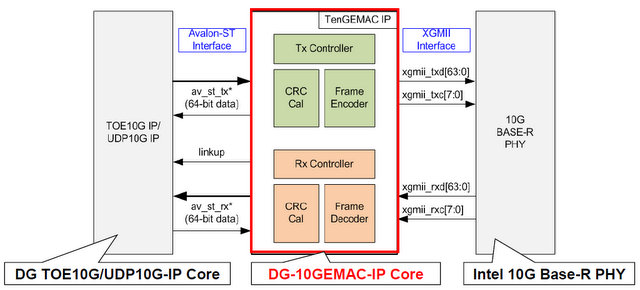

DG 10GEMAC コアで、最小19.2nsの超低レイテンシを実現

DG 10GEMAC コアは、TOE/UDP10G-IP専用に最適化された MAC レイヤを提供します。Altera製MACと完全I/F互換しており、下記の特長を備えます。

|

|

| DG 10GEMAC-IP | Altera 10GEMAC | |

| Tx レイテンシ (clk freq.=156.25MHz) | 19.2ns (3clk) | 76.8ns (12clk) |

| Rx レイテンシ (clk freq.=156.25MHz) | 44.8ns (7clk) | 83.2ns (13clk) |

| ALMs | 1362 | 1617 |

| Registers | 1259 | 3015 |

| Block Memory | 0 | 2320 |

アプリケーション例

TOE-IPは、データスループット要件の急速な増大に対応するための最適ソリューションです。超・高速ネットワーク通信を必要とするアプリケーション例

- マルチ・チャネルHDビデオ・ストリーミング

- カメラ、LIDAR、レーダー、センサーのマルチ・チャネルで構成される自動運転開発システム

- MRIやPETスキャンなどの医療用スキャナー

TOE100G-IP紹介&アプリ例は、YouTubeで視聴頂けます。こちら

TOE100G-IPと最適アプリが1分でわかる 動画まとめ記事

TOE10G-IP 採用実績

.jpg) パイプライン検知・検査システム (画像クリックで拡大) |

.jpg) CTスキャン (画像クリックで拡大) |

||

.png) 衛星追跡システム |

.png) 半導体製造装置 |

.png) 眼科医療装置 |

.png) ビデオ機器 |

.jpg) 魚群探知システム |

.jpg) レーダー・システム |

.jpg) 産業向けプリンタ |

.jpg) 無線通信制御システム |

注文情報

| IPコア | IPコア 型番 | 対応デバイス |

|

TOE200G-IP-A7I | Agilex™ 7 I-Series |

|

TOE100G-IP-A7F | Agilex™ 7 F-Series |

| TOE100G-IP-S10MX | Stratix® 10 MX | |

| TOE100G-IP-S10TX | Stratix® 10 TX | |

|

TOE40G-IP-A10 | Arria® 10 |

|

TOE25G-IP-AGLF | Agilex™ 7 F-Series |

| TOE25G-IP-S10GX | Stratix® 10 GX | |

|

TOE10G-IP-PAC | Altera PAC |

| TOE10G-IP-A10 | Arria® 10 | |

| TOE10G-IP-C10 | Cyclone® 10 | |

|

TOE1G-IP-A10 | Arria® 10 |

| TOE1G-IP-C10 | Cyclone® 10 | |

| TOE1G-IP-A5 | Arria® V | |

| TOE1G-IP-C5 | Cyclone® V | |

| TOE1G-IP-S4 | Stratix® IV | |

| 追加オプション | DG-10GEMAC-IP-A | TOE/UDP10G-IP専用EMAC-IP |

Alliance Partner

株式会社デザイン・ゲートウェイ

本社東京都小金井市中町3-23-17

R&D

89/26 Amornpan 205 Tower1, 18th floor, Ratchadapisek7 (Nathong) Alley, Ratchadapisek Road, Din Daeng, Bangkok, 10400 THAILAND

AI Lab

Faculty of Engineering, Chulalongkorn University, 12th floor, Engineering 4 Building (Charoenvidsavakham), Phayathai Rd., Wang Mai, Pathumwan, Bangkok, 10330 THAILAND