USB3.0-IP coreFAT32 Data Recorder is available!!

Features┃Block diagram┃Document Download┃Applications

Technical document update page

Technical document update page

USB3.0(device)-IP

USB3.0(device)-IP

evaluation on Cyclone IV GX

Video Clip on youtube

DesignGateway provide 1-hour limited free sof file. You can evaluate USB3.0-IP

core on Altera FPGA development kit before purchasing the IP core.

For the evaluation, USB3.0-HSMC adaptor board is necessary.(P/N: AB08-USB3HSMC). Please ask Design Gateway.

Go to Registration page to get password

Go to Registration page to get password

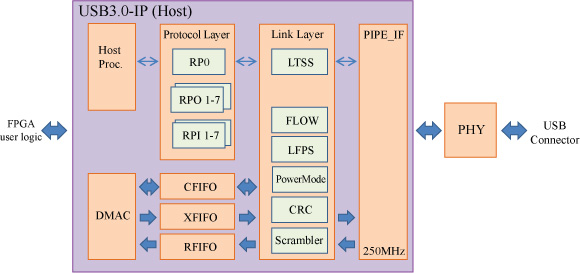

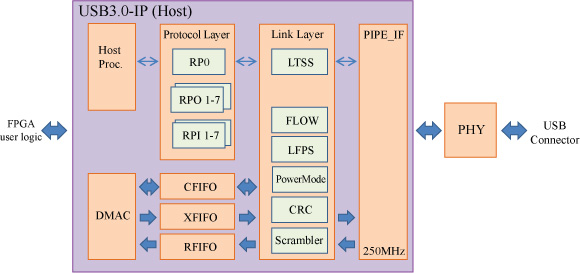

USB3.0-IPcore compliants with the USB 3.0 specification Revision1.0 and work on Altera

5-Series, Cyclone IV, Arria II, Stratix IV FPGA devices.

This IPcore provide link layer, protocol layer. Physical layer interfaces

to PHY chip by TI.

DesignGateway provide 1-hour limited free sof file for Altera FPGA

evaluation board. You can evaluate on Altera Altera development kit

before purchasing the IPcore.

Features

- Compliant with the USB3.0 specification Revision1.0

- USB3.0 Host or Device Controller

- Implement link layer and protocol layer

- IP core clocks are adjustable (250MHz for PIPE I/F, more than 125MHz for internal)

- Support 16bit PIPE interface

- Support IN/OUT end point up to 15 points

- 1 point for control

- 7 points each for IN/OUT - Support All transmission taps (Control, Bulk, Isochronous and Interrupt transmission)

- Simple transaction interface with Host processor or DMA interface

- Able to evaluate on Altera FPGA Development Kit before purchasing the IPcore

Go to Registration page to get password

Go to Registration page to get password

- USB protocol stack is provided by Macnica Macspire. Able to support Video class (UVC) and Audio class (ADC). Please contact Macnica Macspire

Block diagram (Host)

Document download

Common Documents

| Document name | Download |

| USB3.0-IP core Leaflet | Rev2.0 |

| USB3.0-IP core Presentation | Rev1.1 |

| FAT32 Data Recorder Presentation | Rev1.0 |

| AB08-USB3HSMC Board Manual | Rev1.2 |

| Device Family | Cyclone V E, Arria V GX, Cyclone IV GX, Arria II GX, Stratix IV GX | ||||

| IP core& Option |

Datasheet | Reference Design Document | Demo Instruction | Free Evaluation demo file * Ask Password |

|

| USB3.0-IP (Host) |

Rev1.4 | Rev1.0 | Rev1.2 | Cyclone V E Arria V GX |

|

| USB3.0-IP (Device) |

Rev1.4 | Rev1.1 | Rev1.3 | Cyclone V E Arria V GX Cyclone IV GX Arria II GX Stratix IV GX |

|

| FAT32 Data Recorder Demo | Presentation Rev1.0 |

Rev1.0 | Rev1.0 | Cyclone V E Arria V GX |

|

Free sof file for evaluation

USB3.0(device)-IP

USB3.0(device)-IPevaluation on Cyclone IV GX

Video Clip on youtube

For the evaluation, USB3.0-HSMC adaptor board is necessary.(P/N: AB08-USB3HSMC). Please ask Design Gateway.

Performance

USB3.0-IP core can achieve maximum performance of current USB3.0 system.

USB3.0-IP core (external PHY less) evaluation on Stratix IV GX FPGA dev

kit USB3.0-IP core (external PHY less) evaluation on Stratix IV GX FPGA dev

kit(with AB13-USB3PCIe adaptor board) |

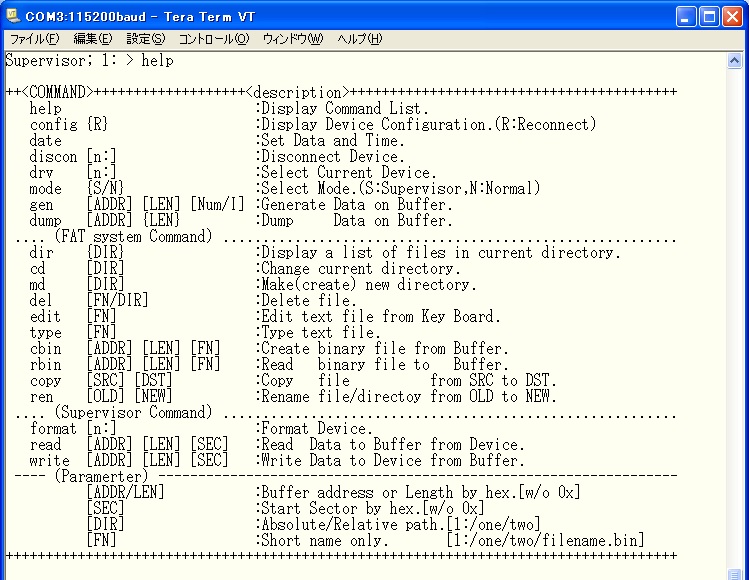

USB3.0-IP core Host Reference Design USB3.0-IP core Host Reference DesignSupport FAT32 commands |

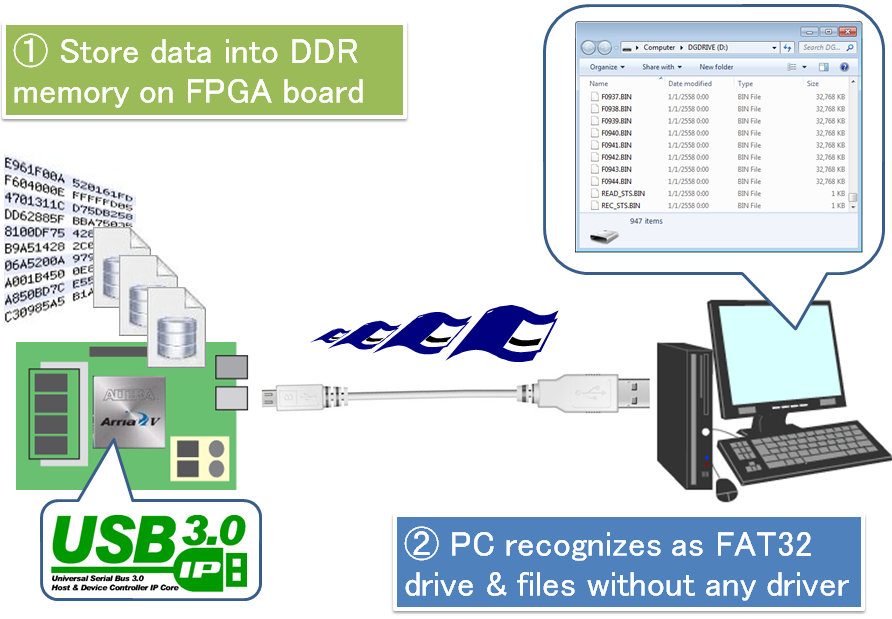

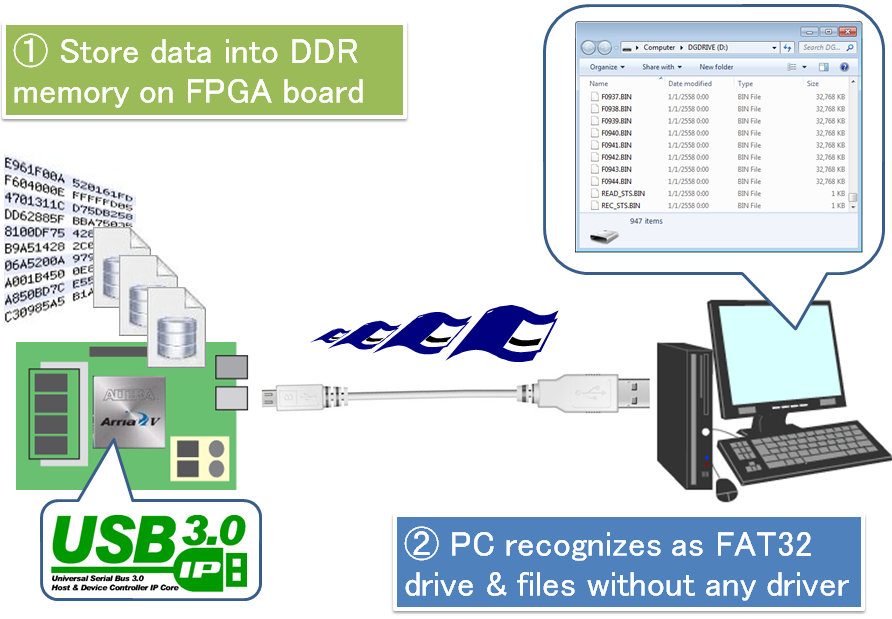

Application: FAT32 data recording system (Device Side)

You can easily build FAT32 data recorder system with USB3.0 Device IP core.System Overview

Features

- PC recognizes as FAT32 external storage without any driver for Windows or Linux!

- FAT32 data recorder reference design is available.

- Free evaluation bit file for Altera FPGA development kits.

Accessories

| Accessories for evaluation | Description |

| USB3.0-HSMC adaptor board for Altera FPGA dev kit. USB3.0 TypeAtoA cable(1m) is attached. |

Alliance Partner

Design Gateway Co., Ltd.

Head Office3-23-17 Naka-cho, Koganei, Tokyo, JAPAN

R&D

89/26 Amornpan 205 Tower1, 18th floor, Ratchadapisek7 (Nathong) Alley, Ratchadapisek Road, Din Daeng, Bangkok, 10400 THAILAND

AI Lab

Faculty of Engineering, Chulalongkorn University, 12th floor, Engineering 4 Building (Charoenvidsavakham), Phayathai Rd., Wang Mai, Pathumwan, Bangkok, 10330 THAILAND