IPLock AES Encryption IP Security System

IP Lock is FPGA logic security system which used very reliable AES encryption

technology. IP properties in FPGA are protected from illegal copy by only

including IP Lock in FPGA and connecting with encryption controller chip.

IP Lock is FPGA logic security system which used very reliable AES encryption

technology. IP properties in FPGA are protected from illegal copy by only

including IP Lock in FPGA and connecting with encryption controller chip.

Document download | Demo video on Youtube

Features

- Strong security by AES encryption

- Change & encrypt authentication data at about 200msec cycle

- Generate true random authentication data by natural random number generator

- Stop user logic when removing the chip

- Connecting I/O with FPGA are only 2 pins

- No need to input clock to IP Lock logic

- Provide easy "Laboratories Pack" and "IP Lock Writer + blank chip"

What is AES Cryptosystem ?

AES(Advanced Encryption Standard) is common key cryptosystem chosen by NIST, US. Both encryption and decryption are high speed. And it is also stronger than triple DES. So it is noticed as encryption standard for next generation replaced with DES. Currently AES is adopted with security for financial system, LAN system and so on.Easy to Get Started with the Laboratories Pack

The Laboratories Pack includes encryption chips pre-programmed with a unique ID at the time of shipment by Design Gateway. This fixed ID key cannot be

rewritten. To prevent duplication, each pack contains chips with a different unique ID, so the IP Lock core must be used with the chips from the same package.

Design Gateway offers 10-chip packs (IPL-010L) and 30-chip packs (IPL-030L),

making this product ideal for prototyping and small-lot production.

The Laboratories Pack includes encryption chips pre-programmed with a unique ID at the time of shipment by Design Gateway. This fixed ID key cannot be

rewritten. To prevent duplication, each pack contains chips with a different unique ID, so the IP Lock core must be used with the chips from the same package.

Design Gateway offers 10-chip packs (IPL-010L) and 30-chip packs (IPL-030L),

making this product ideal for prototyping and small-lot production. Contents of Laboratories pack (IPL-010L):

- Encryption chip 10 pcs or 30 pcs

- CD-ROM

- IP Lock core (Altera / AMD)

- VHDL example source code

- User Manual(PDF)

Writer pack for Mass production

The Writer Pack is designed for mass production. Users can write custom ID keys to blank encryption chips using the IP Lock Writer. An optional ID key can be set for each product or lot. The Writer Pack includes 3 blank chips (IPL-CHP). For mass production, use the Writer Pack together with blank chips (IPL-CHP or IPL-CHP1.8V, MOQ = 100 pcs). IP Lock Writer (IPL-003WR)

IP Lock Writer (IPL-003WR) Blank Encryption chip (IPL-CHP)

Blank Encryption chip (IPL-CHP)- IP Lock Writer

- Blank Encryption chip (IPL-CHP) 3pcs

- USB Cable

- CD-ROM

- Software for IP Lock writer (for writing ID key)

- IP Lock core (Altera / AMD)

- VHDL example source code

- User Manual(PDF)

Easy to protect your Logic data! just add simple circuit on the board!!

- Step1: Prepare SOIC-8 pattern for security chip on your board

- Step2: When you need FPGA logic protection, purchase IPLock product

- Step3: Compile your FPGA logic with IPLock core

- Step4: Put IPLock security chip on FPGA board

- Step5: Complete IP core protection!

|

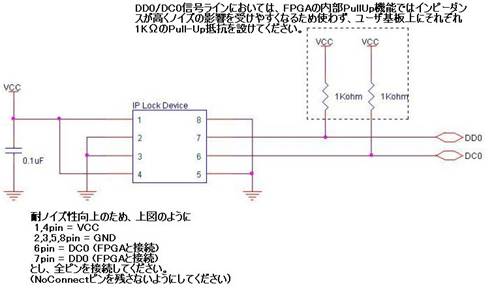

Note: Connect to Virtex-7 Device (with IPL-CHP) DC0/DD0 pin must connect to HR I/O bank. I/O voltage must be 2.5V or 3.3V. In case that HR I/O bank cannot be set I/O voltage more than 2.5V or DC0/DD0 pin connect to HP I/O bank, please choose IPL-CHP1.8V. |

- Board design requirement: 0.1uF Capacitor 1 pc and 1Kohm Resistor 2 pcs

- FPGA IO pin: 2 lines

Technical Documents

| Document | File Name |

| Sales Leaflet | IPL-LF-V1.2E.pdf |

| Presentation | IPL-PR-E.pdf |

| Users Manual for Laboratories Pack IPL-010L/030L | IPLSTD_UserManual1_7_E.pdf |

| Users Manual for Writer Pack IPL-003WR | IPLWR_UserManual1_8_E.pdf |

| How to transfer design with IPLock from ISE to Vivado | IPLock_ISE_Vivado_E.pdf |

| IP Lock Support Devices List | IPL-LIST.pdf for IPL-CHP

IPL-LIST-1.8V.pdf for IPL-CHP1.8V |

|

Software Download

| Software for IPLock Writer Pack |

Support Windows10 Please see "Readme.txt" in the zip file. |

Ordering Information

| Part Number | Note |

| IPL-010L | IPLock Laboratories pack, contains encryption chip (IPL-CHP) 10 pcs with fixed ID key |

| IPL-030L | IPLock Laboratories pack, contains encryption chip (IPL-CHP) 30 pcs with fixed ID key |

| IPL-003WR | IPLock Writer Pack, contains blank encryption chip (IPL-CHP) 3pcs |

| IPL-CHP | Blank chip for Writer pack, MOQ=100pcs |

| IPL-CHP1.8V | Blank chip for Writer pack, Support 1.8V I/O, MOQ=100pcs |

Available now on Mouser!!

Alliance Partner

Design Gateway Co., Ltd.

Head Office3-23-17 Naka-cho, Koganei, Tokyo, JAPAN

R&D

89/26 Amornpan 205 Tower1, 18th floor, Ratchadapisek7 (Nathong) Alley, Ratchadapisek Road, Din Daeng, Bangkok, 10400 THAILAND

AI Lab

Faculty of Engineering, Chulalongkorn University, 12th floor, Engineering 4 Building (Charoenvidsavakham), Phayathai Rd., Wang Mai, Pathumwan, Bangkok, 10330 THAILAND