UDP-IP core seriesFully Hardware-Based UDP/IP Stack Implementation with Agilex 5 Support

Features | Block diagram | Document Download | Applications

Technical document update page

Technical document update page

UDP100G/40G/25G/10G/1G IP core is the epochal solution implemented without CPU. This IP core is suitable for network application. This IP product includes

reference design for Altera FPGA. It helps you to reduce development time.

DesignGateway provide free evaluation demo file for Altera FPGA boards.

You can evaluate UDP10G-IP core on real board before purchasing.

- All Hard wired Logic TCP Offloading Engine TOE-IP core series

- Super Low Latency UDP(Rx/Tx)-IP for Fintech Visit here

Features

|

|

Block diagram

UDP100G-IP |

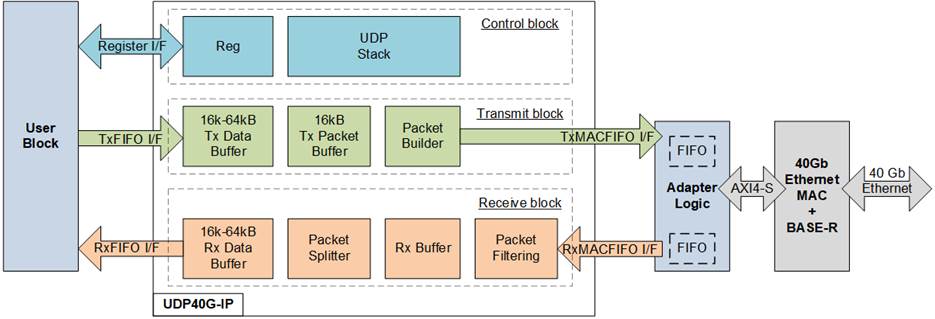

UDP40G-IP |

UDP25G-IP |

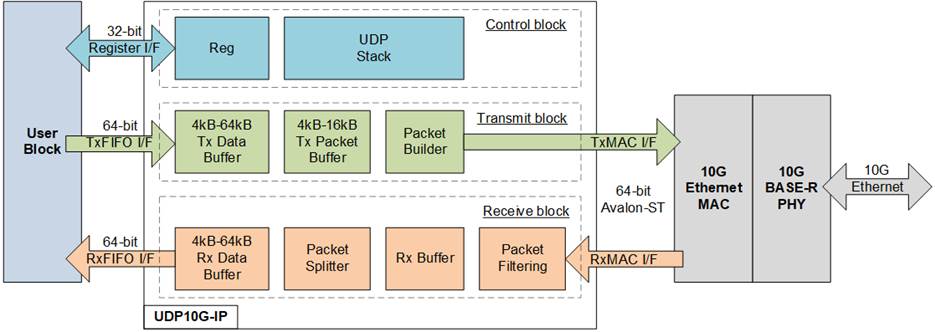

UDP10G-IP |

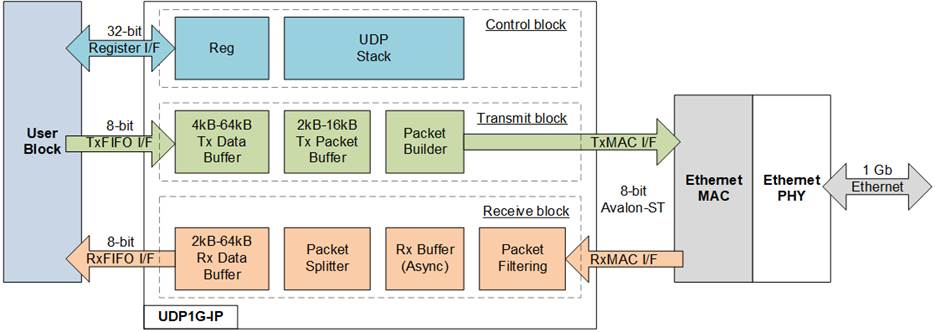

UDP1G-IP |

Videos on YouTube

UDP-IP Introduction |

Reference Design Introduction |

UDP-IP Performance Demo |

UDP-IP Application Examples |

Document & Demo sof file download

| Document name | UDP100G/40G/25G/10G/1G-IP |

| UDP-IP core Presentation | Rev2.0AE |

| DG EMAC-IP Presentation (for UDP10G-IP) | Rev1.0AE |

| IP core simple introduction Blog |

High efficiency up to 4963MB/sec UDP-IP transfer Evaluation Demo

UDP-IP ideal for applications that require real-time & multicast |

| Support Devices | Agilex™ 7 F-Series, Arria® 10 GX/SX, Cyclone 10 GX, Arria V GX, Cyclone V E | |||||

| IP core & Option |

Datasheet | Reference Design Document | Demo Instruction | FPGA Setup Document | Free Evaluation file | |

| UDP100G-IP | Rev1.0 | Rev1.0 | Rev1.02 | Rev3.2 | Agilex F-Series |  |

| UDP40G-IP | Rev1.1 | Rev1.0 | Rev1.0 | - | Arria® 10 GX |  |

| UDP25G-IP | Rev1.0 | Rev1.0 | Rev1.01 | Rev2.2 | Agilex F-Series |  |

| UDP10G-IP | Rev2.00 | Rev2.00 | Rev2.03 | Rev3.03 | Agilex 7 I-Series Agilex 5 Sulfur Arria® 10 SX Arria® 10 GX |

|

| 10GEMAC-IP | Rev1.2 | Rev1.0 | Rev1.0 | Cyclone® 10 GX | ||

| UDP1G-IP | Rev2.00 | Rev2.00 | Rev2.01 | Rev2.02 | Arria 10 GX Arria 10 SX Arria V GX Cyclone V E |

|

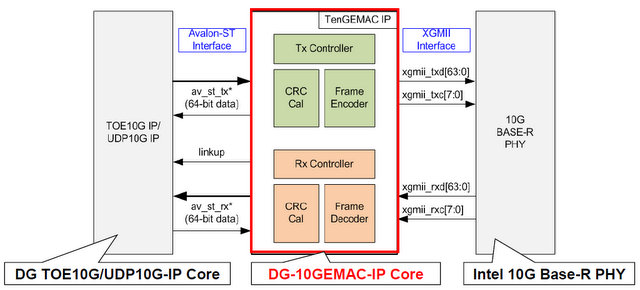

Super low-latency DG 10GbE MAC core for UDP10G-IP

DG 10GbE MAC core implements the MAC layer for UDP10G-IP core and fully

compatible with Altera MAC. It has many advantages.

|

|

| DG 10GEMAC-IP | Altera 10GEMAC | |

| Tx latency (clk freq.=156.25MHz) | 19.2ns (3clk) | 76.8ns (12clk) |

| Rx latency (clk freq.=156.25MHz) | 44.8ns (7clk) | 83.2ns (13clk) |

| ALMs | 1362 | 1617 |

| Registers | 1259 | 3015 |

| Block Memory | 0 | 2320 |

Free sof file for evaluation

DesignGateway provide 1-hour limitation free sof file for Altera FPGA Development Boards. You can evaluate UDP100G/40G/25G/10G/1G-IP core on real board before purchasing.Suitable Applications

Radar system |

Electronics Control Unit (ECU) |

Network game Console |

Delay Tolerant Network (DTN) Investigation |

Alliance Partner

Design Gateway Co., Ltd.

Head Office3-23-17 Naka-cho, Koganei, Tokyo, JAPAN

R&D

89/26 Amornpan 205 Tower1, 18th floor, Ratchadapisek7 (Nathong) Alley, Ratchadapisek Road, Din Daeng, Bangkok, 10400 THAILAND

AI Lab

Faculty of Engineering, Chulalongkorn University, 12th floor, Engineering 4 Building (Charoenvidsavakham), Phayathai Rd., Wang Mai, Pathumwan, Bangkok, 10330 THAILAND