muNVMe IPMultiple data stream access to NVMe SSD simultaneously without CPU!

Features | Block diagram | Document Download

NVMe-IP core series Selection Guide to choose suitable solution

* Features and specifications are planned and subject to change without

notice.

Technical document update page

Technical document update page

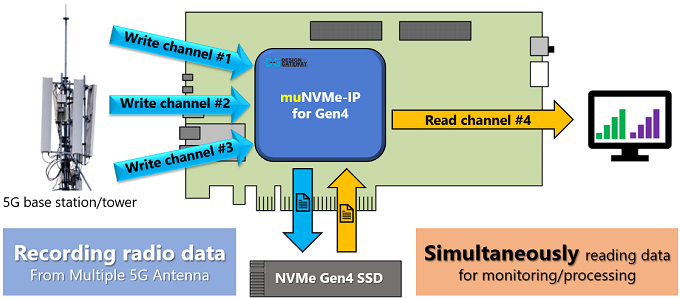

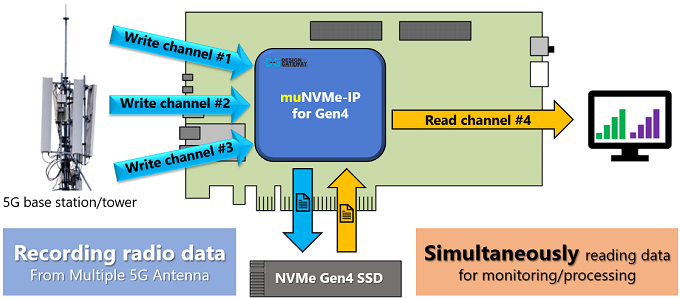

muNVMe-IP is suitable data storage solutions for next generation 5G/6G base station or data logger.

About price and licence of this IP core, please contact Design Gateway.

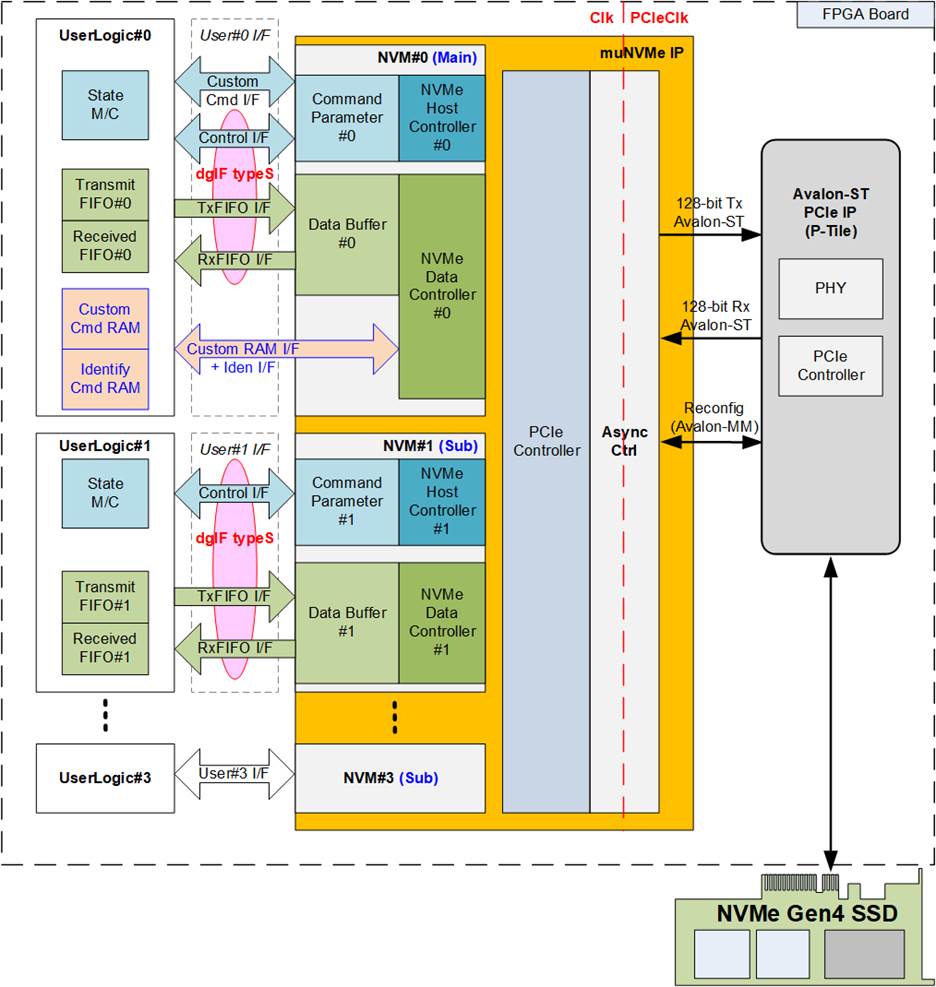

muNVMe-IP (Multi User NVMe IP) is designed and optimized for multiple data stream access to single NVMe SSD by multiple users simultaneously. muNVMe-IP can achieve close to SSD's maximum possible throughput for both mixed read/write and same direction access. This IP is recommended for the application that requires high performance & multiple data streaming or sequential access over single NVMe SSD by pure hardware logic without CPU/OS. Customization to increase the number of users is possible upon customer's requirements.

| No CPU/DDR required Standard Type |

No PCIe Hard IP required | >500K IOPS random write access | Multi user simultaneously access | Random Access By Multiple Users |

|

|

|

|

|

Features

|

|

Block diagram * Click to view |

Document download

Technical Documents

| Support Devices | Agilex™ F series, Arria 10 GX |

|||||

| IP core | Datasheet | Reference Design Document | Demo Instruction Document | FPGA Board Setup | Evaluation demo file | Demo Video |

| muNVMe-IP (Gen4) | Rev1.0 | Rev1.1 | Rev1.1 | Rev4.2 | Agilex-F |  |

| muNVMe-IP (Gen3) | Rev1.0 | Rev1.0 | Rev2.0 | Rev4.2 | Arria 10 GX | |

Application Example

muNVMe-IP is suitable data storage solutions for next generation 5G/6G base station or data logger.

Accessories for evaluation

| Accessories for evaluation | Description | |

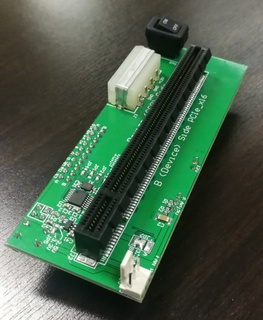

AB18-PCIeX16 AB18-PCIeX16 |

PCIe x16 Lanes Crossover adapter board for NVMe-IP evaluation Download manual |

Purchase |

About price and licence of this IP core, please contact Design Gateway.

Alliance Partner

Design Gateway Co., Ltd.

Head Office3-23-17 Naka-cho, Koganei, Tokyo, JAPAN

R&D

89/26 Amornpan 205 Tower1, 18th floor, Ratchadapisek7 (Nathong) Alley, Ratchadapisek Road, Din Daeng, Bangkok, 10400 THAILAND

AI Lab

Faculty of Engineering, Chulalongkorn University, 12th floor, Engineering 4 Building (Charoenvidsavakham), Phayathai Rd., Wang Mai, Pathumwan, Bangkok, 10330 THAILAND