NVMe IP corePCIe Gen5 is now available On Agilex™ I-Series!!

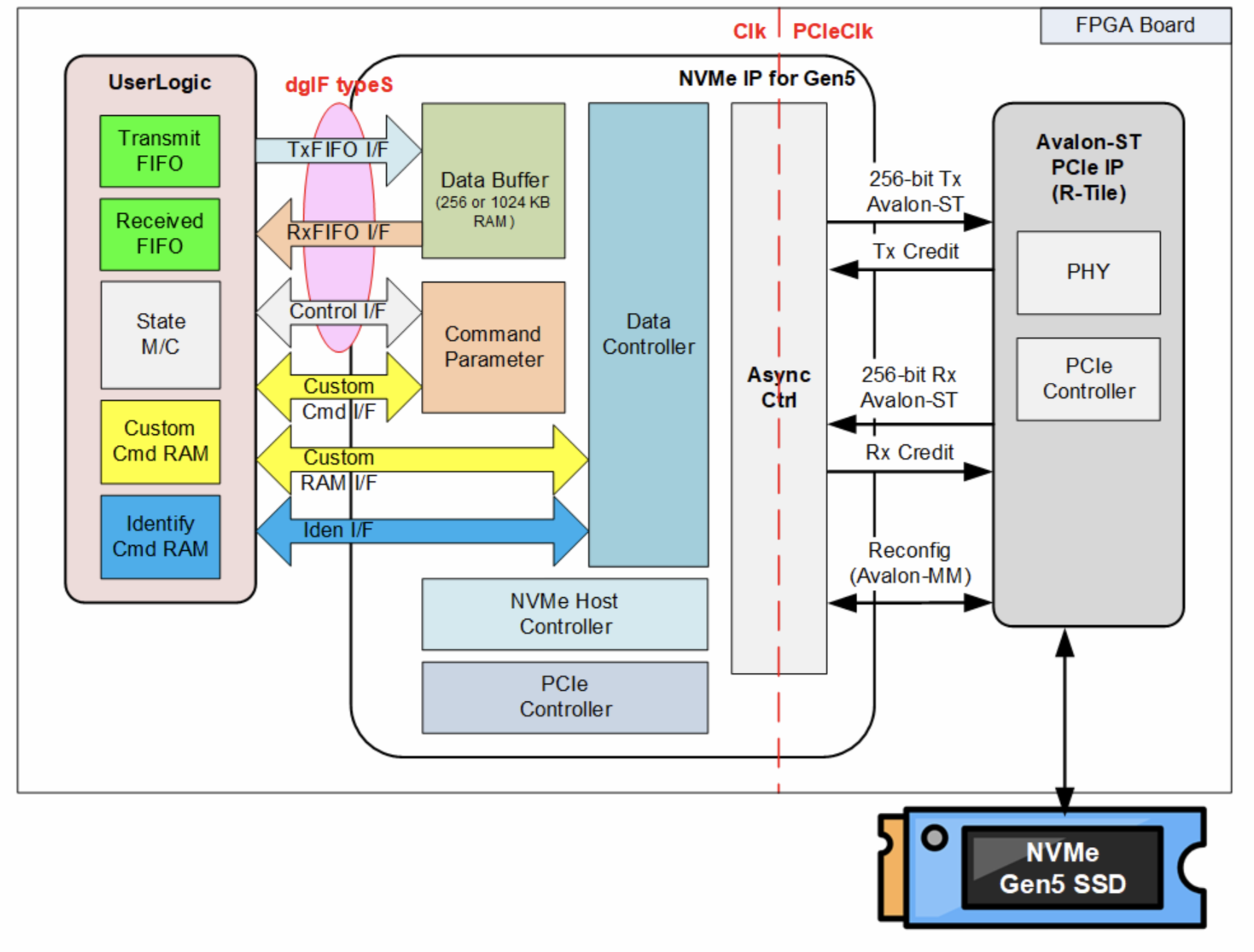

NVMe IP core is standalone NVMe Host Controller with built-in optimized PCIe Bridge and Internal Memory Buffer, designed to handle NVMe Protocol without need CPU/OS and External DDR memory. It’s recommended for the application which requires high performance, high storage capacity, very compact system size and easily to support multiple NVMe SSDs.

NVMeG3 IP including PCIe Gen3 Soft IP inside enable the NVMe SSD interface for non-embedded

PCIe Gen3 Hard IP Devices. Break the barriers of NVMe interface, Allow

to build multi-channel RAID system with very high performance and lowest

possible FPGA resources consumption. Learn more about NVMeG3 IP

This IP core license includes the reference design for Altera FPGA boards.

It helps you to reduce development time and cost.

raNVMe-IP (Random Access) is the new generation of NVMe-IP series which is intentionally optimized for random access. raNVMe-IP can achieve more than 500K IOPS for random write access on high performance NVMe SSD without CPU intervention. Ideal for the application which requires multiple access to NVMe SSD with best performance. Learn more about raNVMe IP

muNVMe-IP (Multi User) is pure hardware logic solutions for very high throughput, multiple data streaming access to NVMe SSD simultaneously without CPU. Simplify your system complexity and maximize performance.Learn more about muNVMe IP

rmNVMe-IP (Random Access & Multi User)is very high performance NVMe Host Controller which is highly optimized for high-IOPS random access applications. rmNVMe-IP supports multiple user interfaces, each user can simultaneously read/write to a single NVMe SSD at the same time.Learn more about rmNVMe IP

| No CPU/DDR required Standard Type |

No PCIe Hard IP required | >500K IOPS random write access | Multi user simultaneously access | Random Access By Multiple Users |

|

|

|

|

|

Features

|

|

Block diagram for Agilex™ 7 I-series | PCIe Gen5 * Click to show more detail for Agilex™ 7 F-series | PCIe Gen4 * Click to show more detail for Stratix® 10 GX * Click to show more detail |

Document download

Common Documents

| Document name | Revision | |

| DG IP core Brochure | Rev2023Q4 | |

| NVMe-IP核 | Rev2.4CA (中文) | |

| NVMe-IP core Presentation | Rev2.3EA | |

| NVMe-IP core series Selection Guide | Rev1.0E | |

IP core Introduction |

Reference design Introduction |

|

NVMe-IP Gen5 Introduction & Demo |

NVMe-IP Gen5 Secure Erase Command & Demo |

|

Technical Documents

PCIe Gen5| Support Devices | Agilex™ 7 I-series | |||||

| IP core & Option |

Datasheet | Reference Design Document | Demo Instruction Document | FPGA Board Setup | Free Evaluation demo file | |

| NVMe-IP (Gen5) | Rev1.0 | Rev1.0 | Rev1.01 | Rev1.2 | Agilex™ 7 I-series |

|

| NVMe-IP Gen5 4ch RAID0 |

Rev1.0 | Rev1.0 | Rev1.2 | Agilex™ 7 I-series |

|

|

| NVMe-IP Gen5 2ch RAID0 |

Rev1.0 | Rev1.0 | Rev1.2 | Agilex™ 7 I-series |

|

|

| Support Devices | Agilex™ 7 F-series |

|||||

| IP core & Option |

Datasheet | Reference Design Document | Demo Instruction Document | FPGA Board Setup | Free Evaluation demo file | |

| NVMe-IP Gen4 | Rev2.0 | Rev2.0 | Rev2.0 | Rev4.2 | Agilex™ 7 F-series |

|

| NVMe-IP Gen4 4ch RAID0 |

Rev1.1 | Rev1.1 | Rev1.0 | Agilex™ 7 F-series |

||

| Support Devices | Agilex™ 5 E-series Stratix® 10 GX, Arria® 10 SX, Arria® 10 GX, Cyclone® 10 GX, Arria® V GX |

|||||

| IP core & Option |

Datasheet | Reference Design Document | Demo Instruction Document | FPGA Board Setup | Free Evaluation demo file | |

| NVMe-IP for Agilex 5™ E-series | Rev1.00 | Rev4.06 | Rev4.03 | Sulfur Agilex™ 5 E-series |

||

| NVMe-IP for Stratix® 10 GX | Rev1.0 | Rev1.0 | Rev4.06 | Rev4.03 | Stratix® 10 GX | |

| NVMe-IP | Rev3.06 | Rev3.5 | Rev4.06 | Rev4.03 | Arria® 10 SX Arria® 10 GX Cyclone® 10 GX Arria® V GX ALARIC DevKit Terasic TR5 |

Arria 10 SX Dev kit  ALARIC DevKit |

| 2ch RAID0 | Rev1.1 | Rev2.1 | Arria 10 SX Alaric DevKit |

|

||

| exFAT-IP for NVMe-IP |

Rev1.3 | Rev1.2 | Rev1.3 | Arria 10 GX | ||

| FAT32-IP for NVMe-IP |

Rev1.0 | Rev1.0 | Rev1.0 | Arria 10 SX Arria 10 GX |

||

| NVMe IP for PCIe switch *Customization Support. Please ask us. |

Rev1.2 | Rev1.1 | Rev1.1 | Arria 10 GX |  |

|

| with Linux | Rev1.0 | Rev1.0 | Arria 10 SX | |||

Accessories for evaluation

| Accessories for evaluation | Description | |

AB20-U2PCI AB20-U2PCI |

PCIe Gen5 SSD support, U.2/U.3-PCIe adapter board for NVMe-IP evaluation . Able to connect 4 U.2/U.3 NVMe SSDs. * SSD is not included. Product manual |

Purchase |

AB19-M2PCI AB19-M2PCI |

PCIe Gen5 SSD support, M.2-PCIe adapter board for NVMe-IP evaluation. Able to connect

4 NVMe SSDs. * SSD is not included. Download manual |

Purchase |

AB17-M2FMC AB17-M2FMC |

M.2-FMC adapter board for NVMe-IP evaluation. Able to connect 2 NVMe SSDs.

* SSD is not included. Download manual |

Purchase |

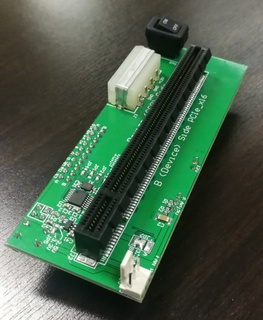

AB18-PCIeX16 AB18-PCIeX16 |

PCIe x16 Lanes Crossover adapter board for NVMe-IP evaluation Download manual |

Purchase |

About price and licence of this IP core, please contact Design Gateway.

Performance

PCIe Gen5 SSD 4ch RAID demo

NVMe-IP core achieves Write 40 GB/s on Agilex™ I-Series FPGA with PCIe Gen5 4ch RAID0.YouTube : NVMe-IP PCIe Gen5 4ch RAID0 Evlaution Demo on Agilex™ I-Series

PCIe Gen5 SSD demo

NVMe-IP core achieves Write 10,186 MB/s, Read 8,479 MB/s on Agilex™ I-Series FPGA with PCIe Gen5 SSD.(Gigabyte AORUS Gen5 10000 SSD, LFSR 128GB data)

YouTube : NVMe-IP PCIe Gen5 Evlaution Demo on Agilex™ I-Series

PCIe Gen4 SSD 4ch RAID demo

NVMe-IP core achieves ultra high-speed 21GB/sec for both Read and Write on Agilex™ 7 FPGA with PCIe Gen4 4ch RAID0!!YouTube : NVMe-IP PCIe Gen4 4ch RAID0 Evlaution Demo on Agilex™ F-Series

You can evaluate the performance on Altera FPGA boards with free download sof file before purchasing. We prepare adaptor boards AB17-M2FMC, AB18-PCIeX16, AB19-M2PCI for the evaluation.

Application example

NVMe-IP core is the best solution for applications which requires huge data transmission with high-speed. |

|

|

|

|

| Surveillance Camera | Data Logger | Video Editing System | Medical Image Analysis | Aerospace & Defense |

Alliance Partner

Design Gateway Co., Ltd.

Head Office3-23-17 Naka-cho, Koganei, Tokyo, JAPAN

R&D

89/26 Amornpan 205 Tower1, 18th floor, Ratchadapisek7 (Nathong) Alley, Ratchadapisek Road, Din Daeng, Bangkok, 10400 THAILAND

AI Lab

Faculty of Engineering, Chulalongkorn University, 12th floor, Engineering 4 Building (Charoenvidsavakham), Phayathai Rd., Wang Mai, Pathumwan, Bangkok, 10330 THAILAND