NVMeG3 IP coreNVMe PCIe Gen3 SSD is available!!

Features┃Block diagram┃Document Download┃Applications

NVMe-IP core series Selection Guide to choose suitable solution

Please receive technical document update from DG News Letter. Subscribe to DG News

Please receive technical document update from DG News Letter. Subscribe to DG News

Technical document update page

Technical document update page

About price and licence of this IP core, please contact Design Gateway.

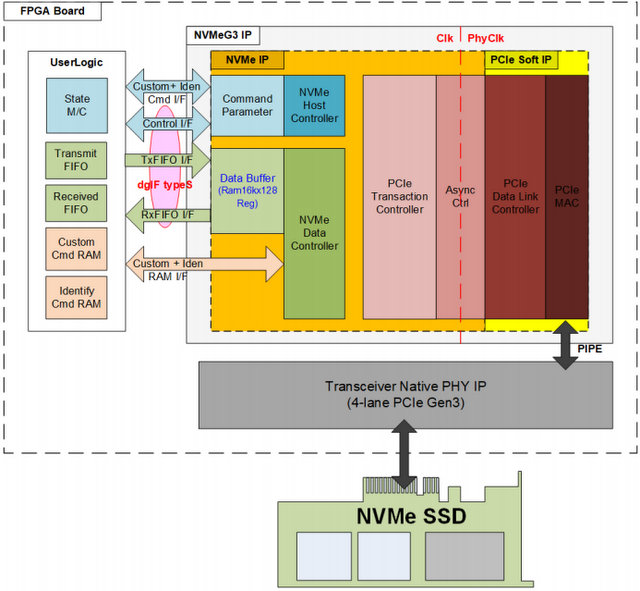

NVMeG3 IP with PCIe Gen3 Soft IP enable the NVMe SSD interface for non-embedded PCIe Gen3 Hard IP Devices.

Break the barriers of NVMe interface, Allow to build multi-channel RAID

system with very high performance and lowest possible FPGA resources consumption.

This IP core license includes the reference design for Altera FPGA

boards. It helps you to reduce development time and cost.

| No CPU/DDR required Standard Type |

No PCIe Hard IP required | >500K IOPS random write access | Multi user simultaneously access | Random Access By Multiple Users |

|

|

|

|

|

Features

|

|

Block diagram * Click to View |

Document download

Common Documents

| Document name | Revision |

| NVMe-IP core Leaflet | Rev2.3 |

| NVMe-IP核 | Rev2.4CA (中文) |

| NVMe-IP core Presentation | Rev2.3EA |

Documents for each Device families

| Document name | Arria 10 GX | |

| NVMeG3-IP with PCIe Gen3 Soft-IP | NVMeG3-IP Datasheet | Rev1.1 |

| Reference Design Document | Rev1.0 | |

| Demo Instruction Document | Rev4.05 | |

| FPGA Setup Document | Rev4.2 | |

| Free Evaluation demo file | Arria 10 GX | |

|

||

Accessories for evaluation

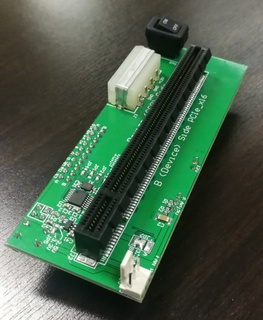

| Accessories for evaluation | Description | |

AB18-PCIeX16 AB18-PCIeX16 |

PCIe x16 Lanes Crossover adapter board for NVMe-IP evaluation Download manual |

Purchase |

About price and licence of this IP core, please contact Design Gateway.

Application example

NVMeG3-IP core is the best solution for applications which requires huge data transmission with high-speed. |

|

|

|

|

| Surveillance Camera | Data Logger | Video Editing System | Medical Image Analysis | Aerospace & Defense |

Articles

Alliance Partner

Design Gateway Co., Ltd.

Head Office3-23-17 Naka-cho, Koganei, Tokyo, JAPAN

R&D

89/26 Amornpan 205 Tower1, 18th floor, Ratchadapisek7 (Nathong) Alley, Ratchadapisek Road, Din Daeng, Bangkok, 10400 THAILAND

AI Lab

Faculty of Engineering, Chulalongkorn University, 12th floor, Engineering 4 Building (Charoenvidsavakham), Phayathai Rd., Wang Mai, Pathumwan, Bangkok, 10330 THAILAND